High-speed signal sampling and synchronizing framework and method applied to signal processing chip

A signal processing chip, high-speed signal technology, used in signal transmission systems, electrical signal transmission systems, instruments, etc., can solve the problems of multi-channel signals being unable to synchronize, high-speed signal sampling is unstable, etc., to achieve stable transmission and achieve stability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The specific embodiment of the present invention is described in detail below in conjunction with specific embodiment:

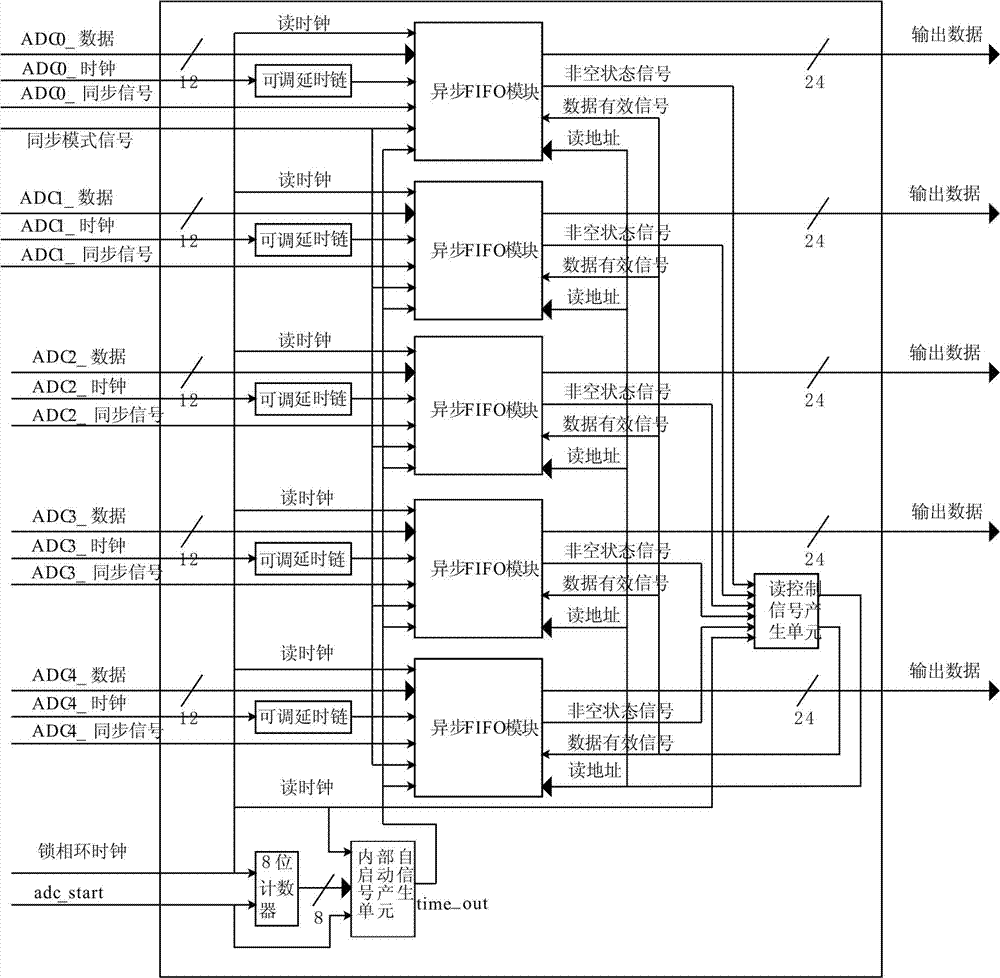

[0027] see figure 1 , the high-speed signal sampling and synchronous architecture applied to the signal processing chip provided by the present invention includes an adjustable delay chain module, an asynchronous FIFO module, a read control signal generating unit, an internal self-starting signal generating unit and a first counter; The input 5 ADC signals are sampled and processed synchronously.

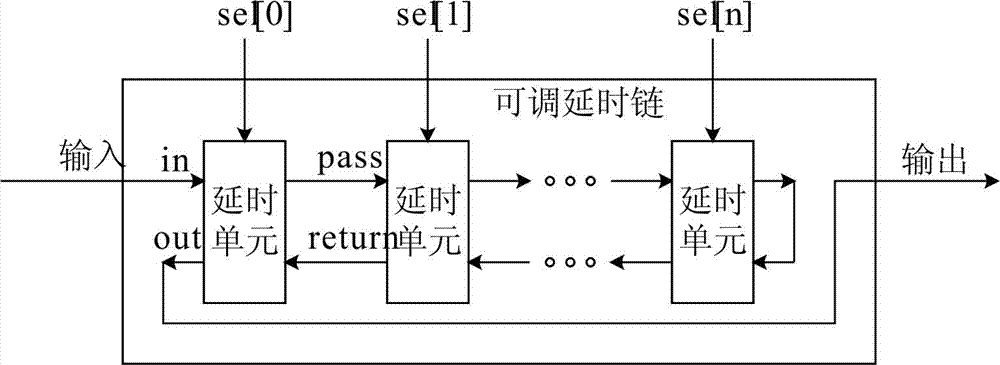

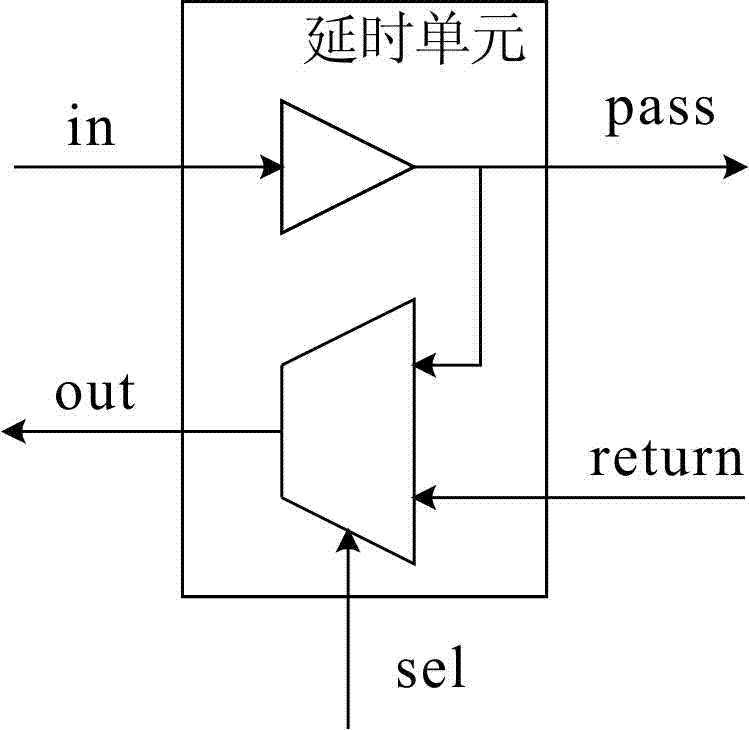

[0028] Among them, the adjustable delay chain module is used to perform adjustable delay processing on the input ADC clock signal, so that the ADC clock and ADC data can maintain a precise phase relationship, so that a single signal can be sampled accurately; where, The total length of the adjustable delay chain is controlled within 1 clock cycle, so that the clock can always sample (delay) the ADC data by adjusting the length of the delay chain under any ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More