Rd+ based 8b/10b coding circuit

A coding circuit and coding technology, applied in the field of coding circuits, can solve the problem of too many memory resources, and achieve the effect of saving memory resources and saving resources significantly.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

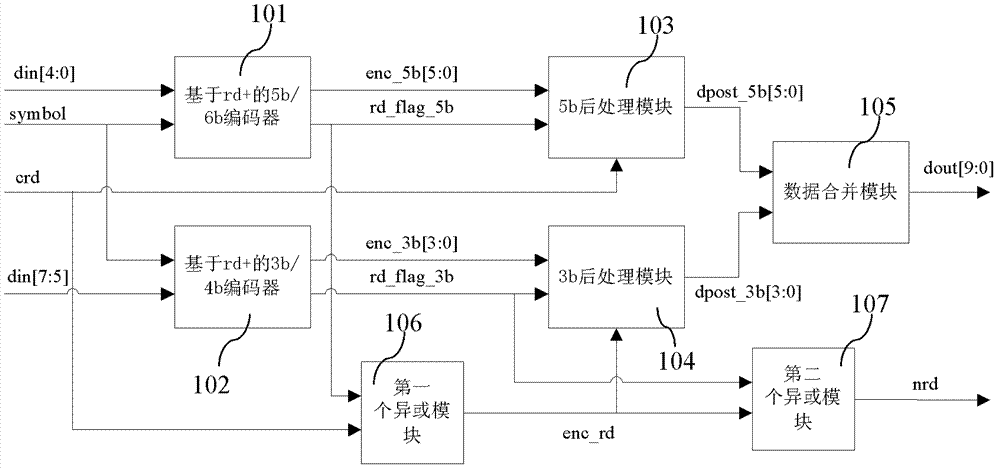

[0021] Such as figure 1 Shown is a structural diagram of an rd+-based 8b / 10b encoding circuit according to an embodiment of the present invention. The rd+-based 8b / 10b encoding circuit in the embodiment of the present invention is composed of rd+-based 5b / 6b encoder (enc_5b_to_6b) 101, rd+-based 3b / 4b encoder (enc_3b_to_4b) 102, 5b post-processing module (post_5b) 103, 3b A processing module (post_3b) 104, a data merging module (data_merge) 105, a first exclusive OR module (xor1) 106, and a second exclusive OR module (xor2) 107 are formed.

[0022] The rd+-based 5b / 6b encoder 101 is a 5b / 6b encoder based on an rd+ encoding method; the rd+-based 3b / 4b encoder 102 is a 3b / 4b encoder based on an rd+ encoding method.

[0023] The external input data is 8-bit data, and the 8-bit data is split into low 5-bit data and high 3-bit data, and the low 5-bit data is input to the rd+-based 5b / 6b encoder 101, and the high 3-bit Data is input to the rd+ based 3b / 4b encoder 102 . The extern...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More