PowerPC architecture based multifunctional low-power-consumption bus communication module

A technology of bus communication and low power consumption, applied in the field of data communication, can solve the problems of high power consumption, great influence on system stability and reliability, and high system heat dissipation design requirements, so as to reduce power consumption, reduce task overhead, The effect of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

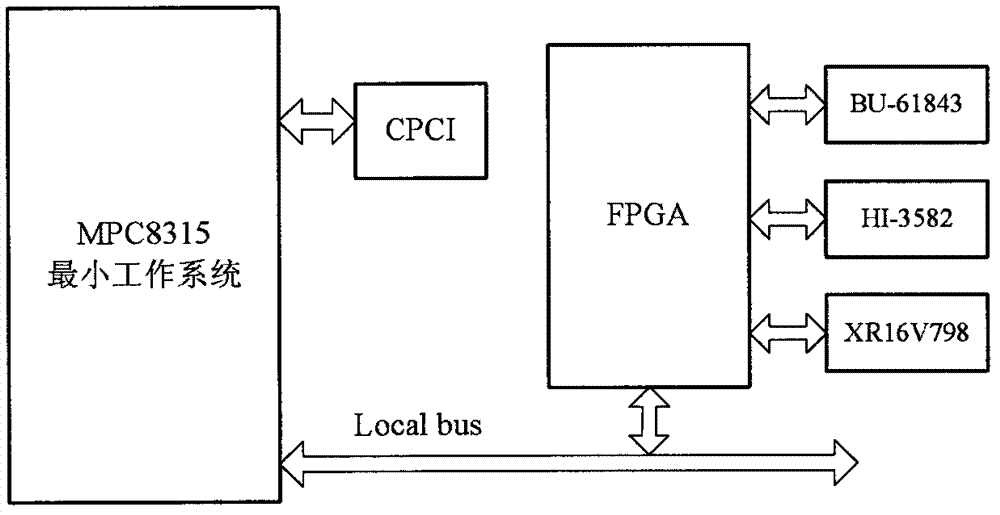

[0014] as attached figure 1 The multi-function bus communication module shown mainly includes the following three parts: the organizational structure of the hardware; the configuration of the underlying BSP of the MPC8315; the logic control and coordination inside the FPGA.

[0015] 1) The hardware structure of the multi-function bus communication module

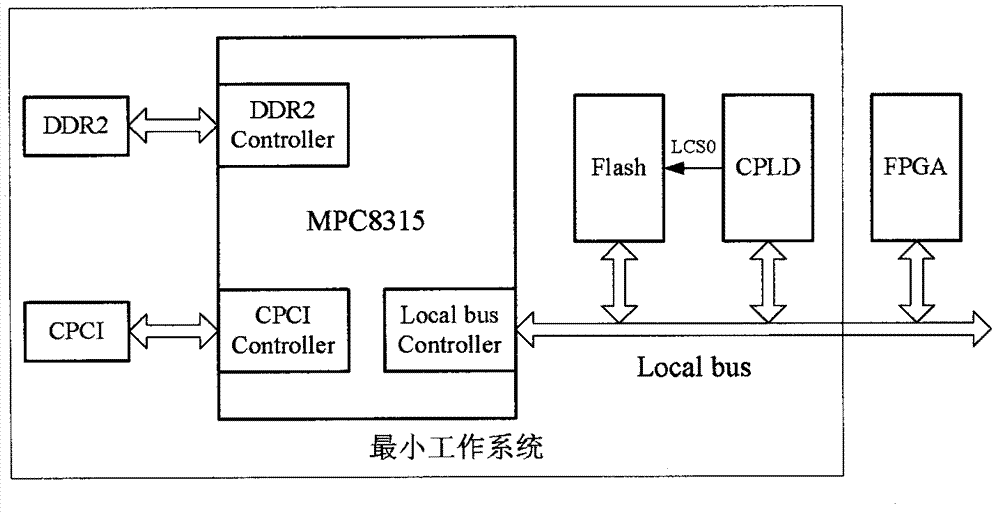

[0016] MPC8315 minimum working system: including one piece of MPC8315, four pieces of SDRAM, one piece of CPLD and one piece of NORFlash, as attached figure 2 shown. The maximum operating frequency of MPC8315 is 400MHz, the maximum power consumption of the core is 1.69W, and the maximum power consumption of the Local bus used to connect peripheral chips is 0.056W. MPC8315 greatly reduces the power consumption of the system while reducing the operating frequency, and the performance degradation caused by the reduction of the main frequency can be compensated by the back-end FPGA, thus greatly reducing the power consumpti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More