Chip validation method and device and system based on field programmable gate array (FPGA)

A verification method and chip technology, applied in the direction of instruments, static indicators, etc., can solve the problems of low verification coverage, inability to objectively and accurately realize automatic verification, etc., and achieve the effect of improving the coverage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

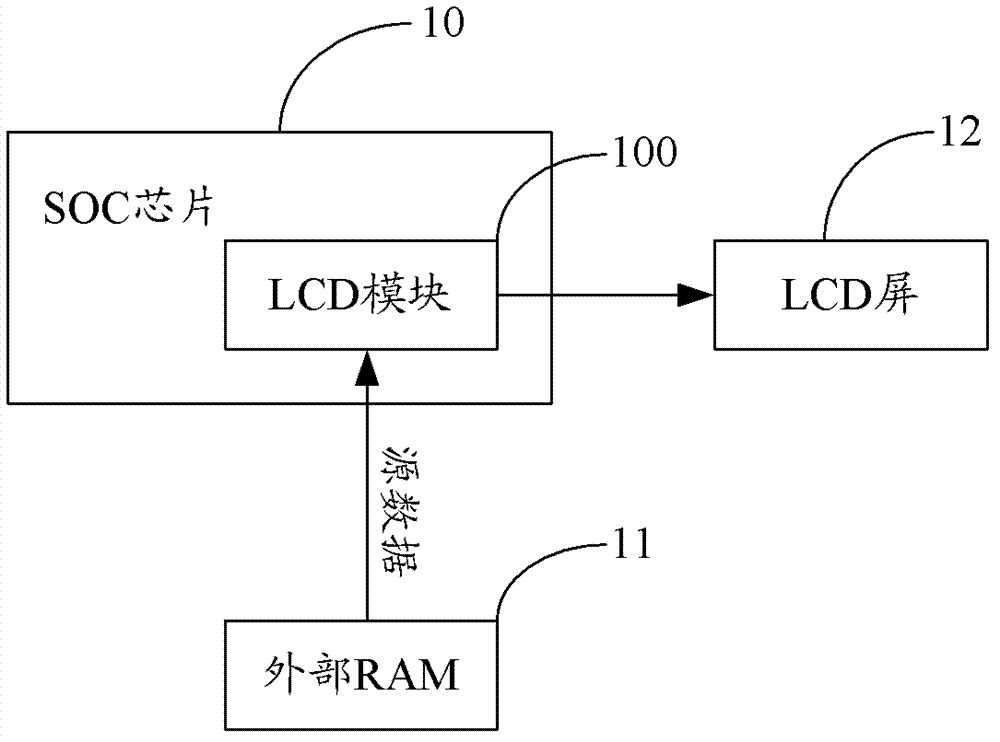

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0027] The embodiment of the present invention verifies the LCD module by randomly generating source data, and uses a monitoring unit to compare the result data with reference data, thereby realizing objective and accurate automatic verification and improving verification coverage.

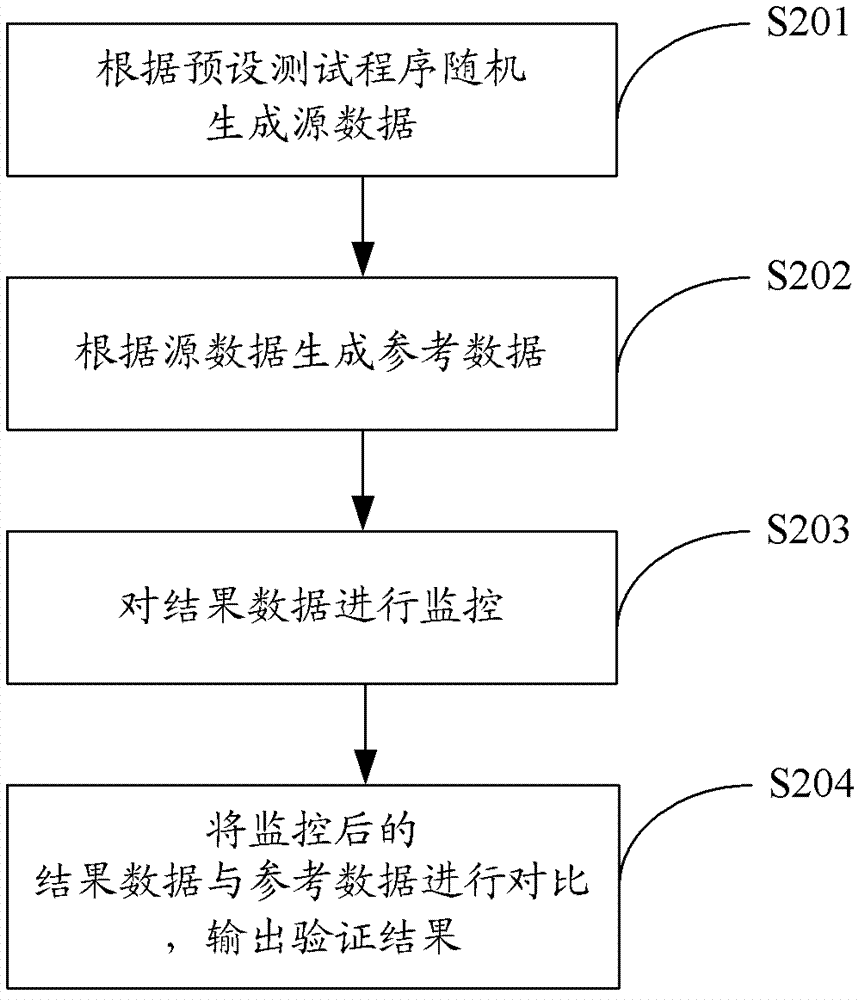

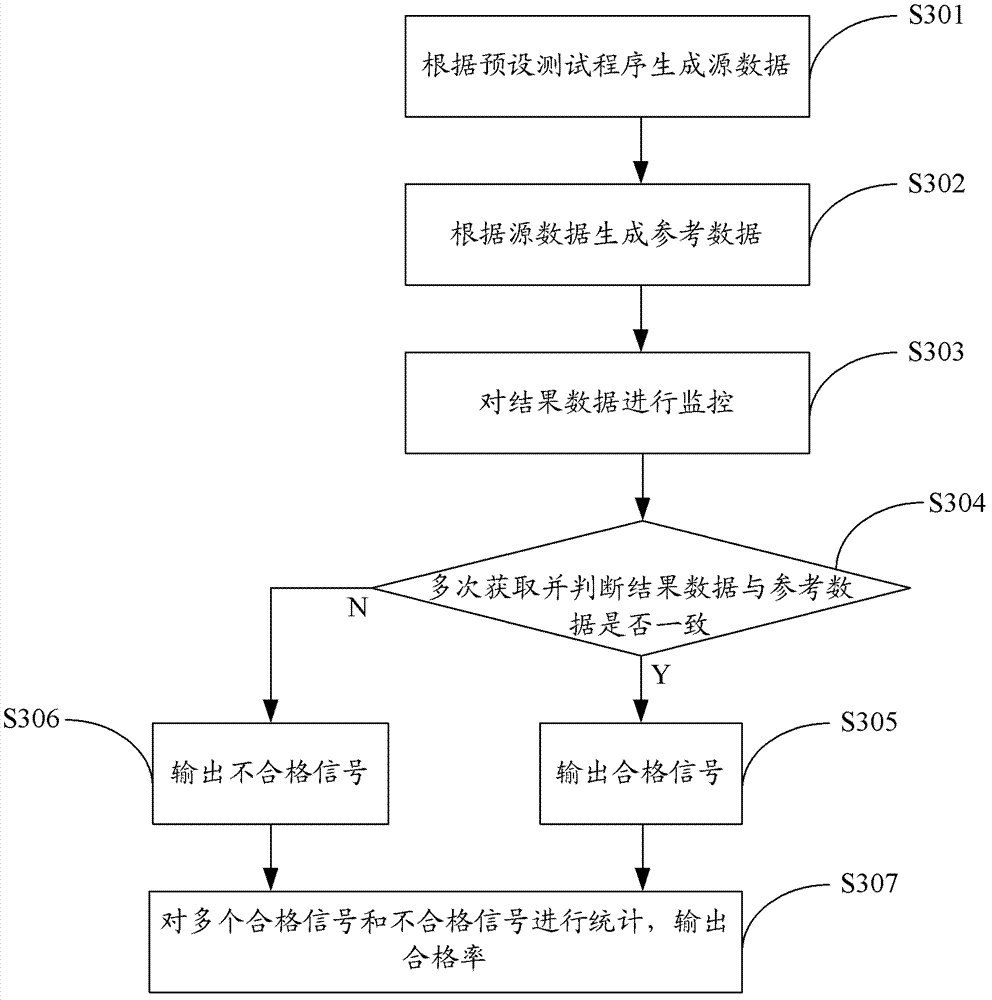

[0028] figure 2 The implementation flow of the FPGA-based chip verification method provided by the first embodiment of the present invention is shown. For the convenience of description, only the parts related to the present invention are shown.

[0029] As an embodiment of the present invention, this FPGA-based chip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More