8-bit semiconductor storage unit, manufacturing method and storage unit array thereof

An 8-bit, storage unit technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, information storage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0056] In order to clearly describe the structure and method of the present invention, the meanings of the following terms are defined here:

[0057] "Relative" means that the two are symmetrical about the center of the symmetry point, and "adjacent" means that the two are close to each other.

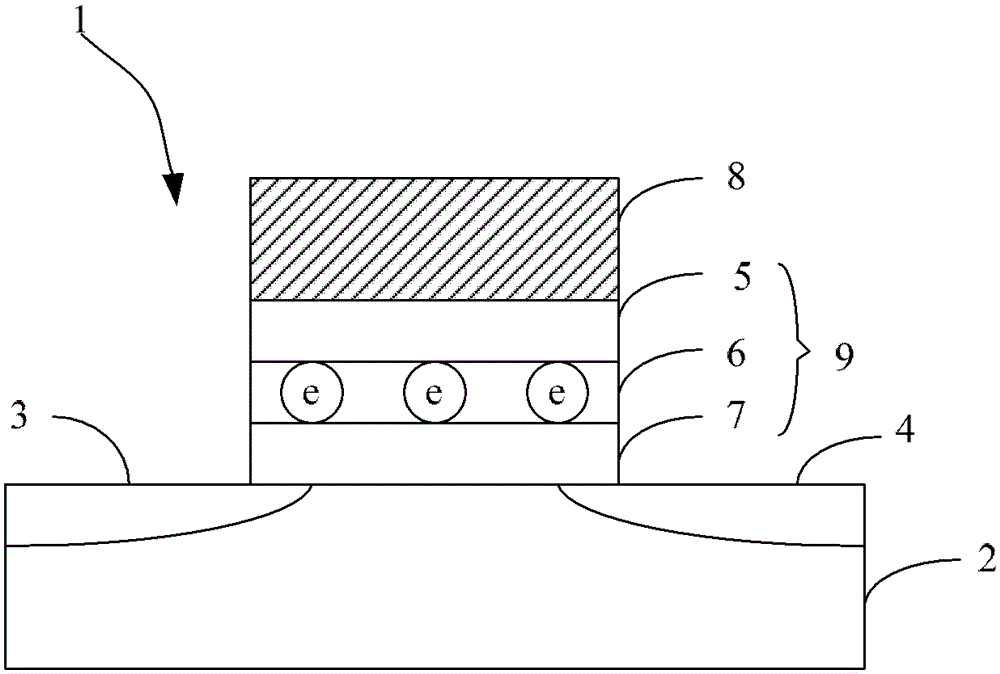

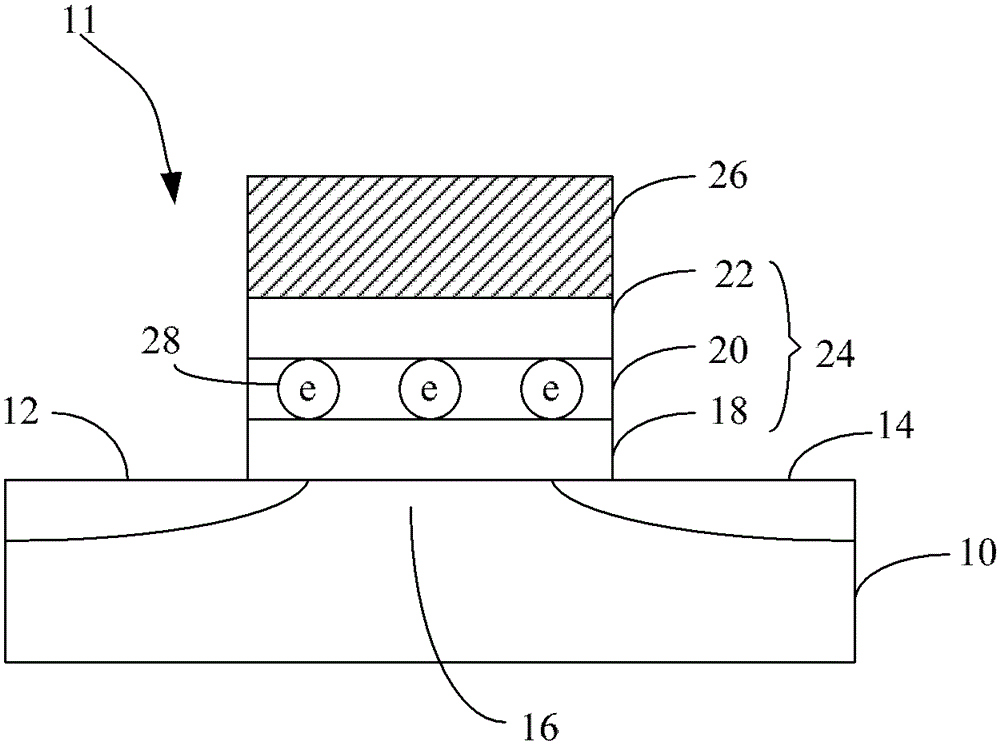

[0058] The present invention provides an 8-bit memory cell, which includes a source region and a drain region, a semiconductor fin, a gate region, and an active region and a gate region disposed on a semiconductor substrate. , A charge storage recombination layer having a charge trapping layer.

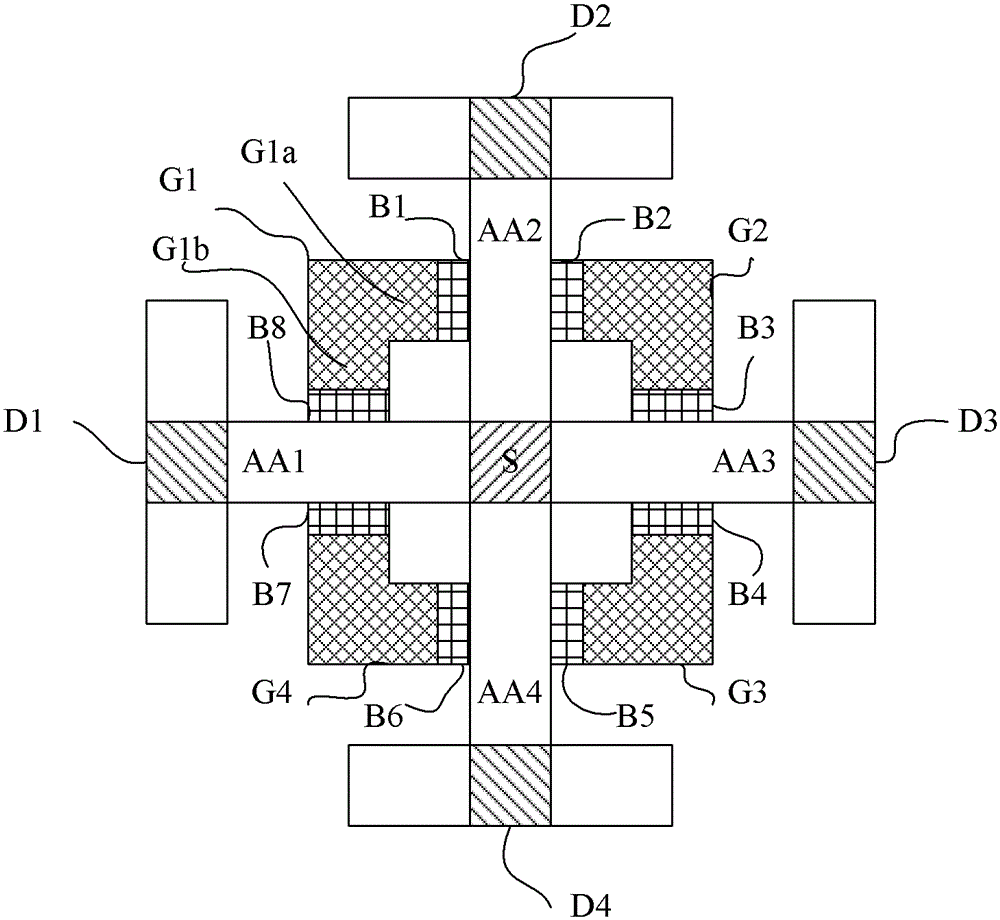

[0059] image 3 It is a top view of the semiconductor storage unit of the present invention, such as image 3 The semiconductor storage unit shown includes one sourc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More