Internal storage static state partition and virtualization method

A virtualization and static technology, applied in the direction of memory address/allocation/relocation, memory system, instrument, etc., can solve the problems of high performance overhead, double page table space, large space overhead, etc., and achieve the effect of low performance overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

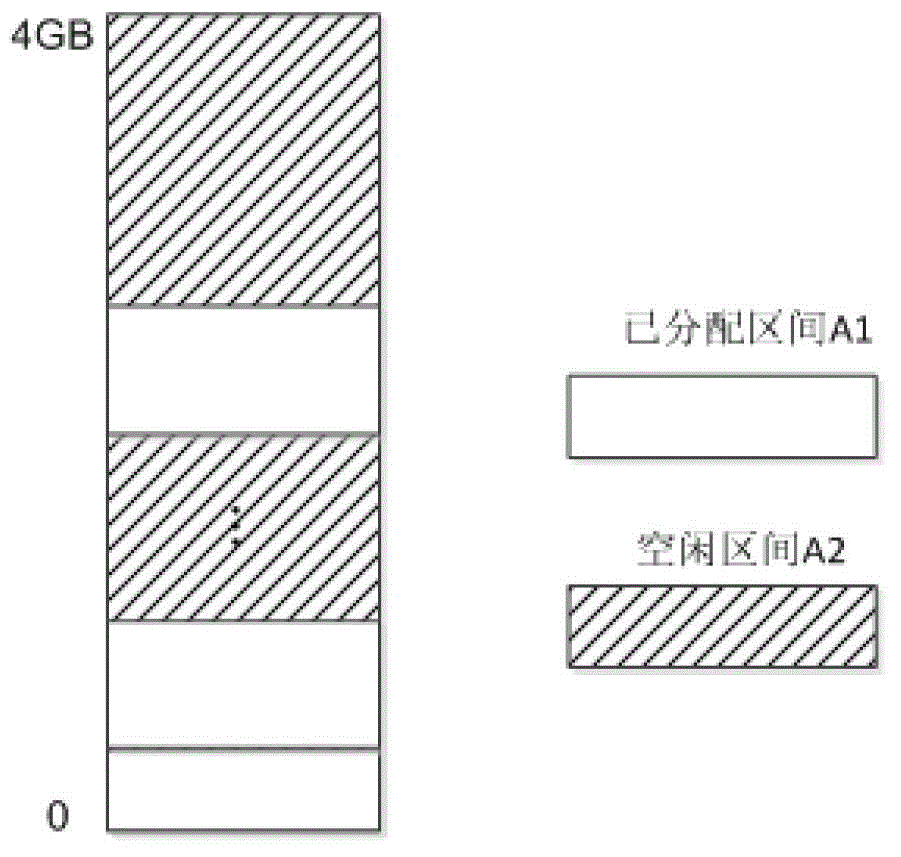

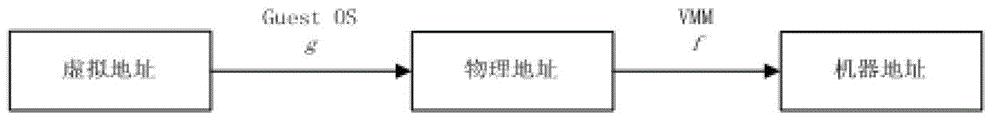

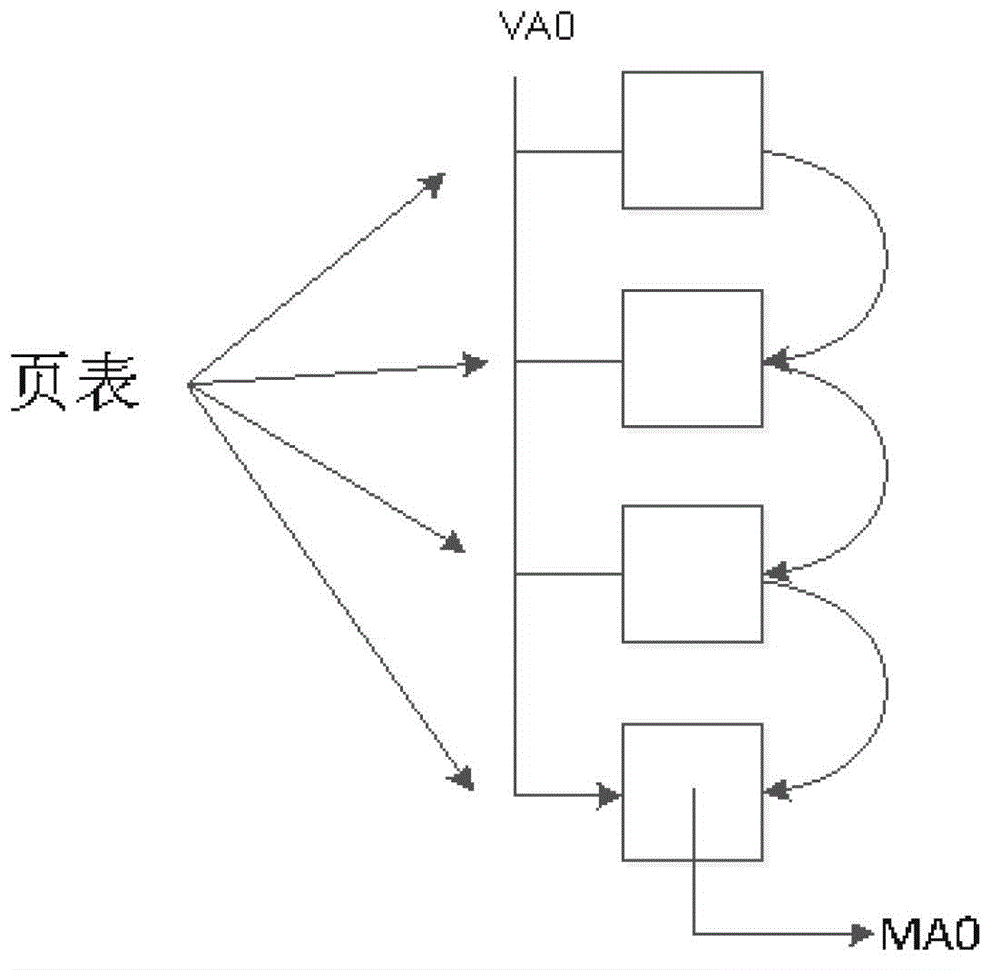

[0030] Different from the prior art that uses dynamic allocation to realize memory virtualization, and the virtual machine requests memory from the host machine when it needs memory; the embodiment of the present invention adopts static memory allocation, and pre-allocates a fixed-size memory when the virtual machine is created. Memory. Correspondingly, in the memory static partition virtualization method based on TLB Miss filling according to the embodiment of the present invention, memory virtualization mode transparent to the virtual machine kernel is implemented by means of static allocation of memory and modification of the TLB Miss filling process, which has low Features of performance overhead and low memory overhead.

[0031] The princi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More