Loop circuit compensating circuit

A loop compensation and circuit technology, applied in the direction of adjusting electrical variables, control/regulating systems, instruments, etc., can solve the problems of large layout area, excessive circuit layout, unfavorable product miniaturization, etc., to reduce the layout area, The effect of increasing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

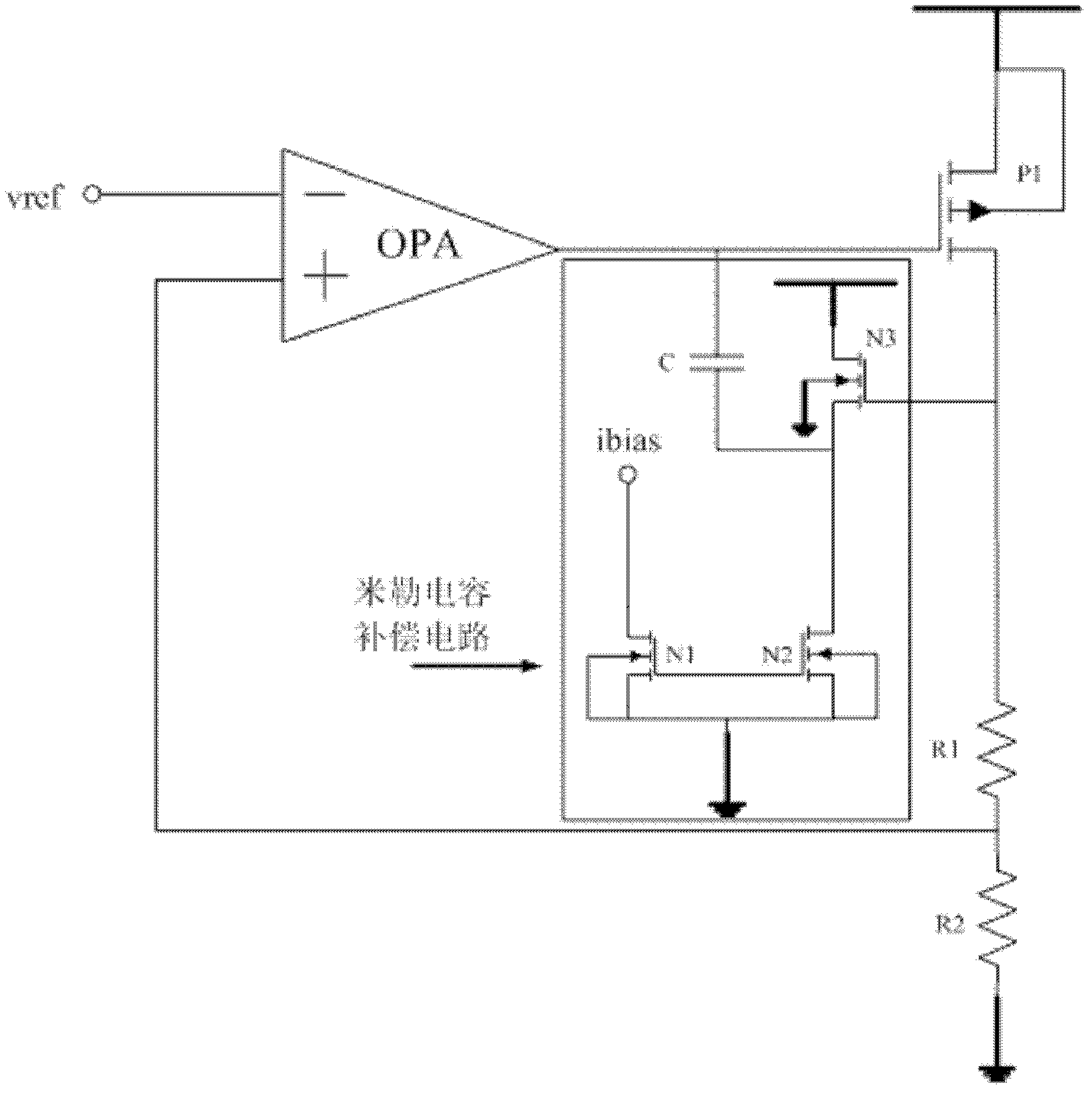

Image

Examples

Embodiment Construction

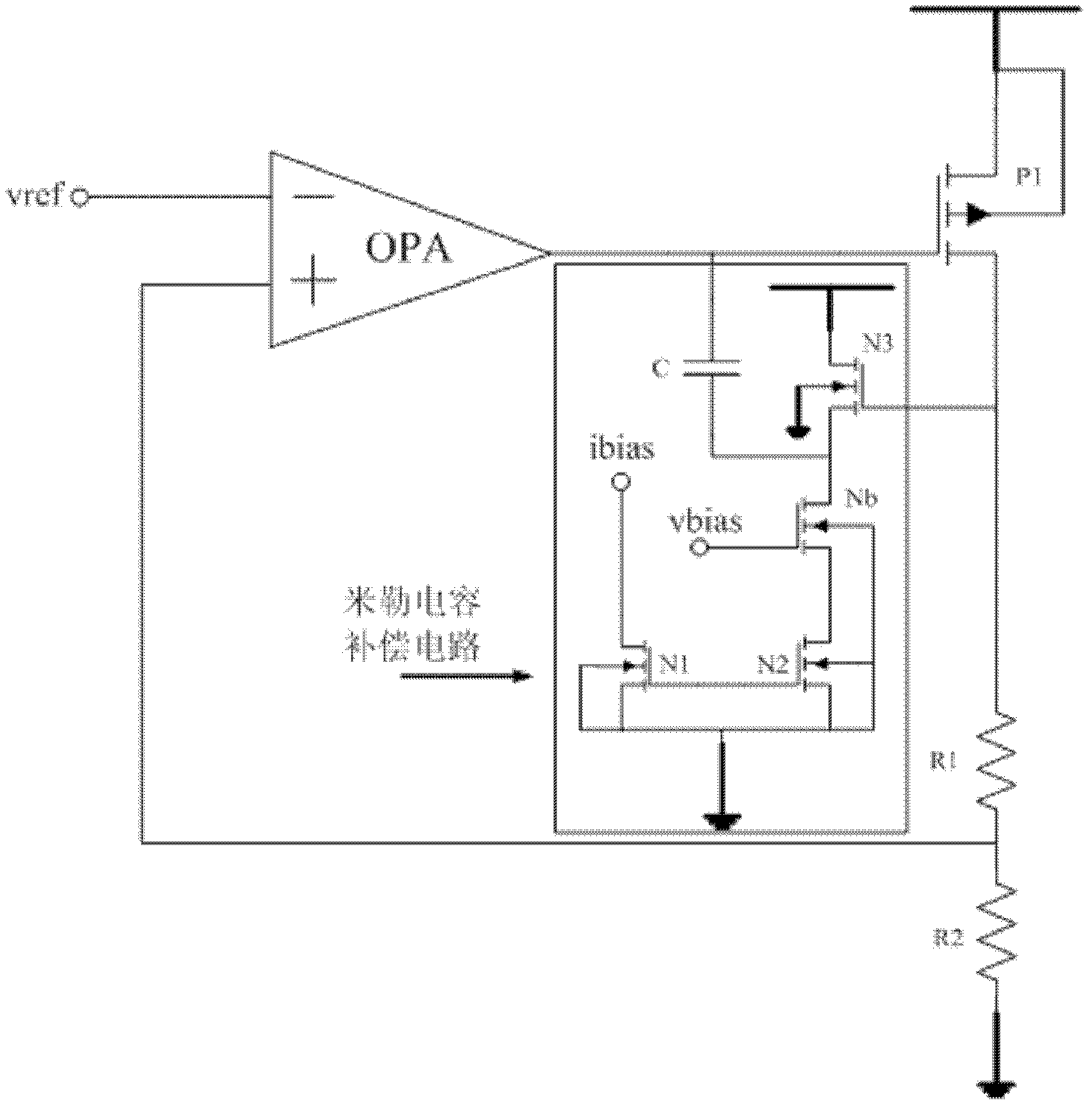

[0023] like figure 2 As shown, the loop compensation circuit of the present invention includes: an operational amplifier OPA, its negative input terminal is connected to the reference voltage, its positive input terminal is grounded through a resistor R2, and its output terminal is connected to the gate of the PMOS transistor P1;

[0024] PMOS transistor P1, its source is connected to the power supply, and its drain is grounded through resistor R1 and resistor R2;

[0025] Capacitor C, its positive terminal is connected to the gate of PMOS transistor P1, and its negative terminal is connected to the source of NMOS transistor N3;

[0026] NMOS transistor N3, its gate is connected to the drain of PMOS transistor P1, its drain is connected to the power supply, and its source is connected to the drain of NMOS transistor N2;

[0027] The source of the NMOS transistor N1 is connected to the source of the NMOS transistor N2 and then grounded, which is connected to the gate of the N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More