Network signal output circuit

An output circuit and network signal technology, applied in the field of network signal output circuit, can solve problems such as timing advance, output too fast, network card chip unable to receive 100MHZ network clock signal normally, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

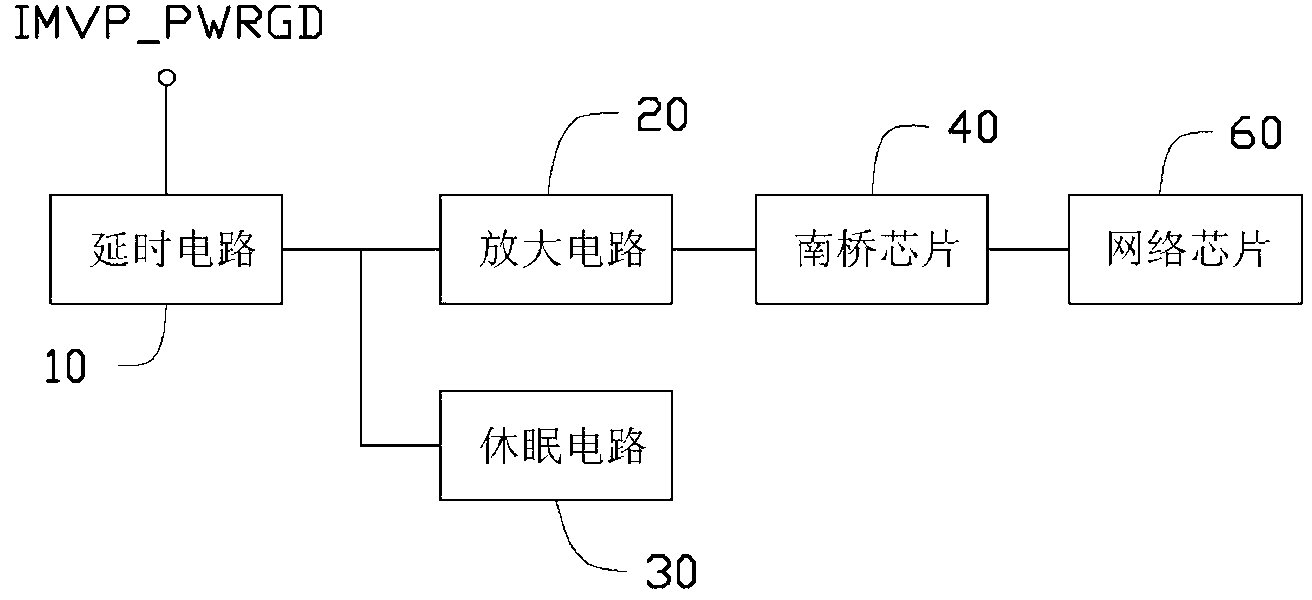

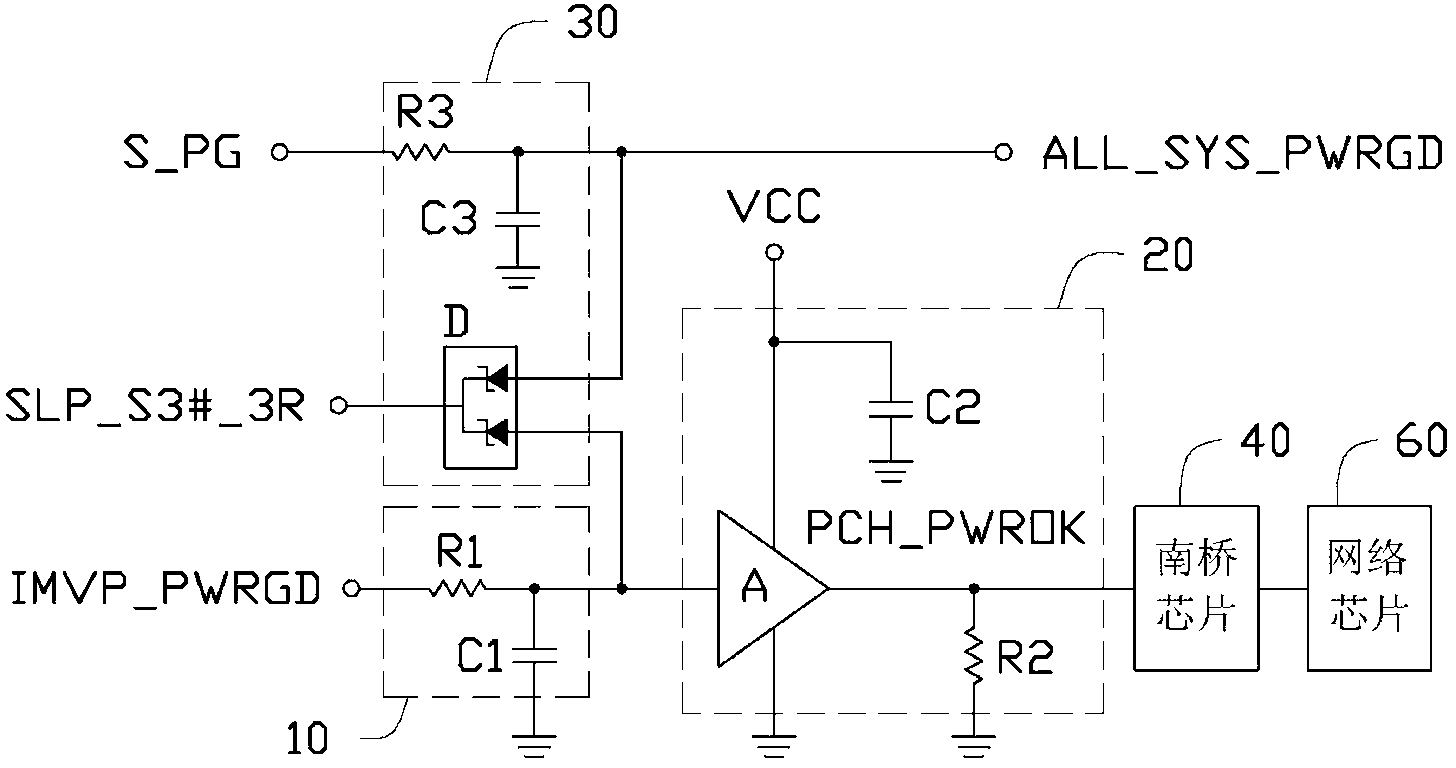

[0011] see figure 1 with figure 2 A preferred embodiment of the network signal output circuit of the present invention includes a delay circuit 10, an amplifying circuit 20 electrically connected to the delay circuit 10, and an amplifying circuit electrically connected to the delay circuit 10 and the amplifying circuit 20. Sleep circuit 30 , a south bridge chip 40 and a network chip 60 . The delay circuit 10 receives a first DC voltage signal, and outputs the first DC voltage signal after a delay. The amplifying circuit 20 receives the delayed first DC voltage signal, converts the delayed first DC voltage signal into a second DC voltage signal, and outputs it to the south bridge chip 40 . The south bridge chip 40 outputs a network clock signal to drive the network chip 60 after receiving the second DC voltage signal. The dormancy circuit 30 receives a system power supply normal signal, and outputs a system dormancy signal to the south bridge chip 40 according to the system...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More