Semiconductor wafer and semiconductor sealing structure

A semiconductor and wafer technology, applied in the field of semiconductor construction, can solve the problems of accelerating crack formation in the metal layer under the bump, reducing the bonding area, shortening the crack growth path, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the above objects, features and advantages of the present invention more comprehensible, preferred embodiments of the present invention are exemplified below and described in detail in conjunction with the accompanying drawings. Furthermore, the directional terms mentioned in the present invention, such as "up", "down", "front", "back", "left", "right", "inside", "outside", "side", etc., It is only for orientation with reference to the attached drawings. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention.

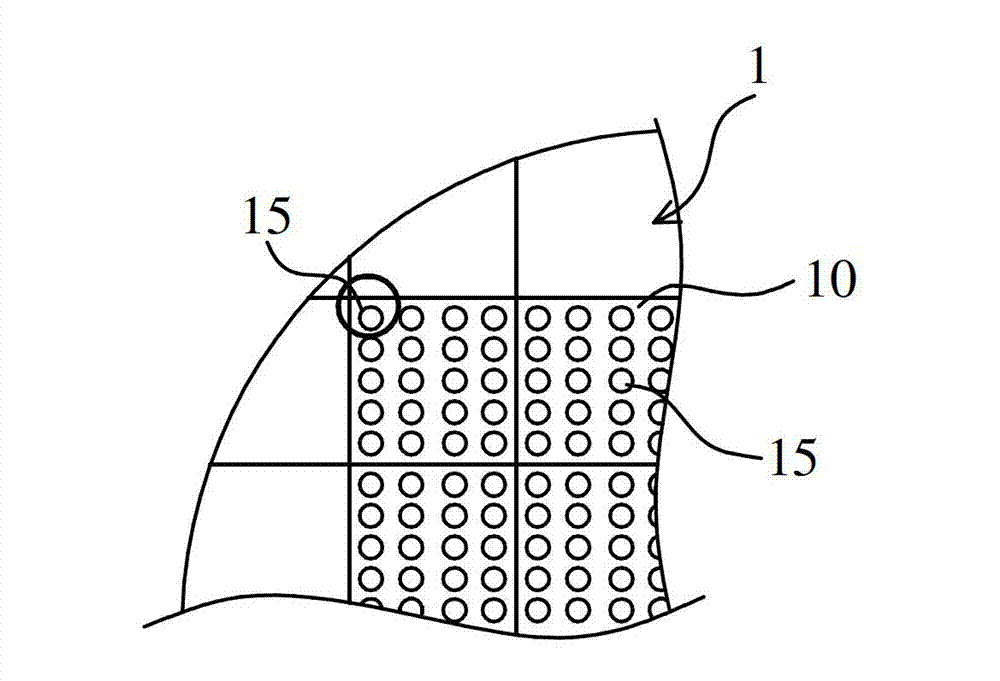

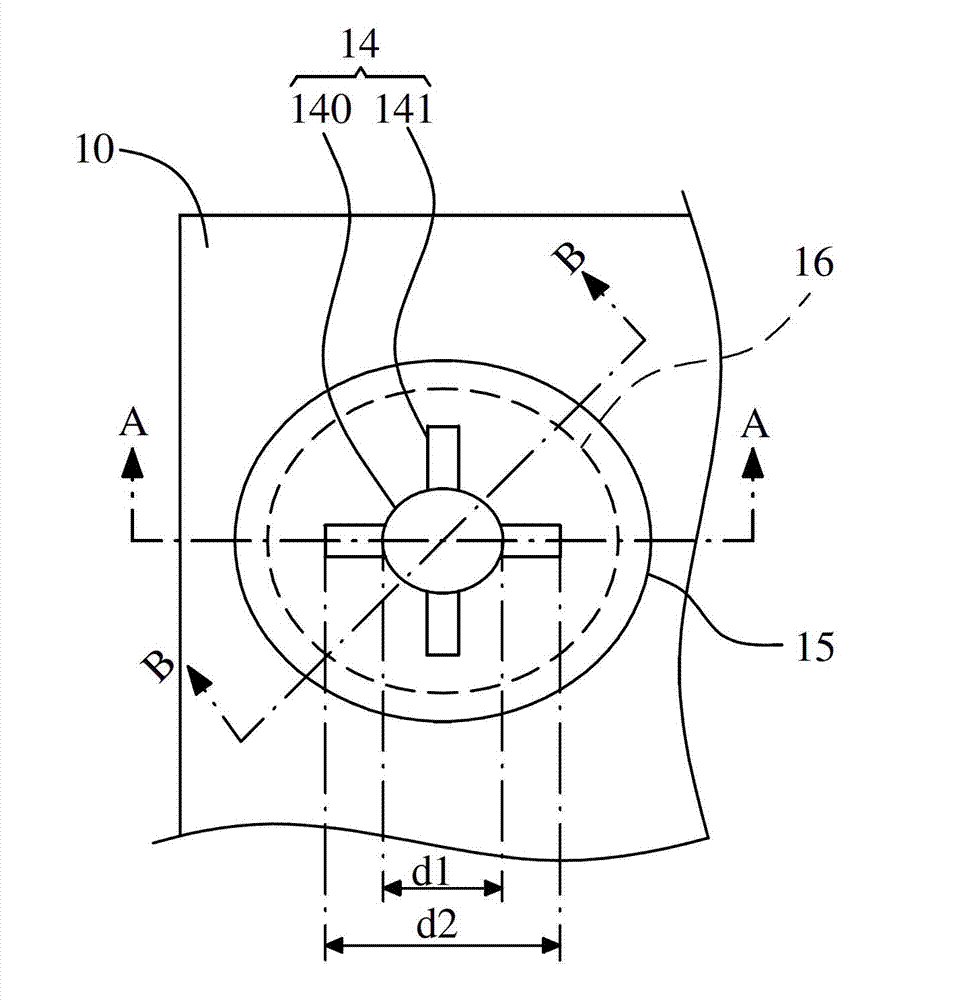

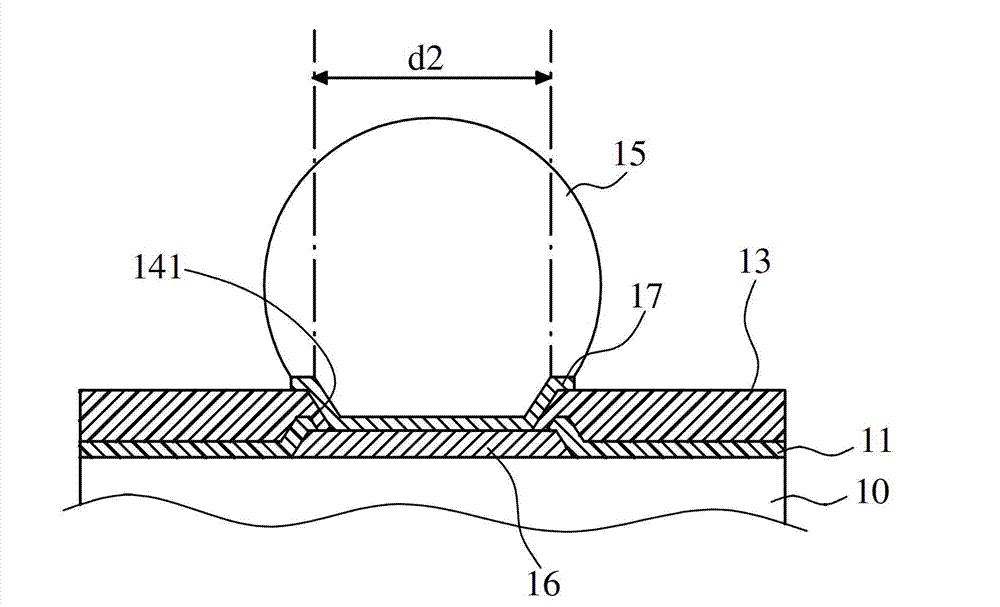

[0018] Please refer to figure 1 , figure 2 , Figure 3A and Figure 3B as shown, figure 1 is a partial top view of a semiconductor wafer according to an embodiment of the present invention; figure 2 yes figure 1 Partial enlarged schematic diagram of ; Figure 3A is along figure 2 Schematic sectional view viewed along line A-A of ; Figure 3B is along ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More