Compressive-sensing-based sparse signal under-sampling method and implementation device

A sparse signal and compressed sensing technology, applied in the direction of analog-to-digital converters, can solve the problems of wasting sensor time and storage space, without reducing the pressure of front-end ADCs, etc., to facilitate transmission, reduce sampling rate, and reduce speed the effect of the requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

[0053] The specific embodiment one, the sparse signal undersampling method based on compressed sensing, it is realized by the following steps:

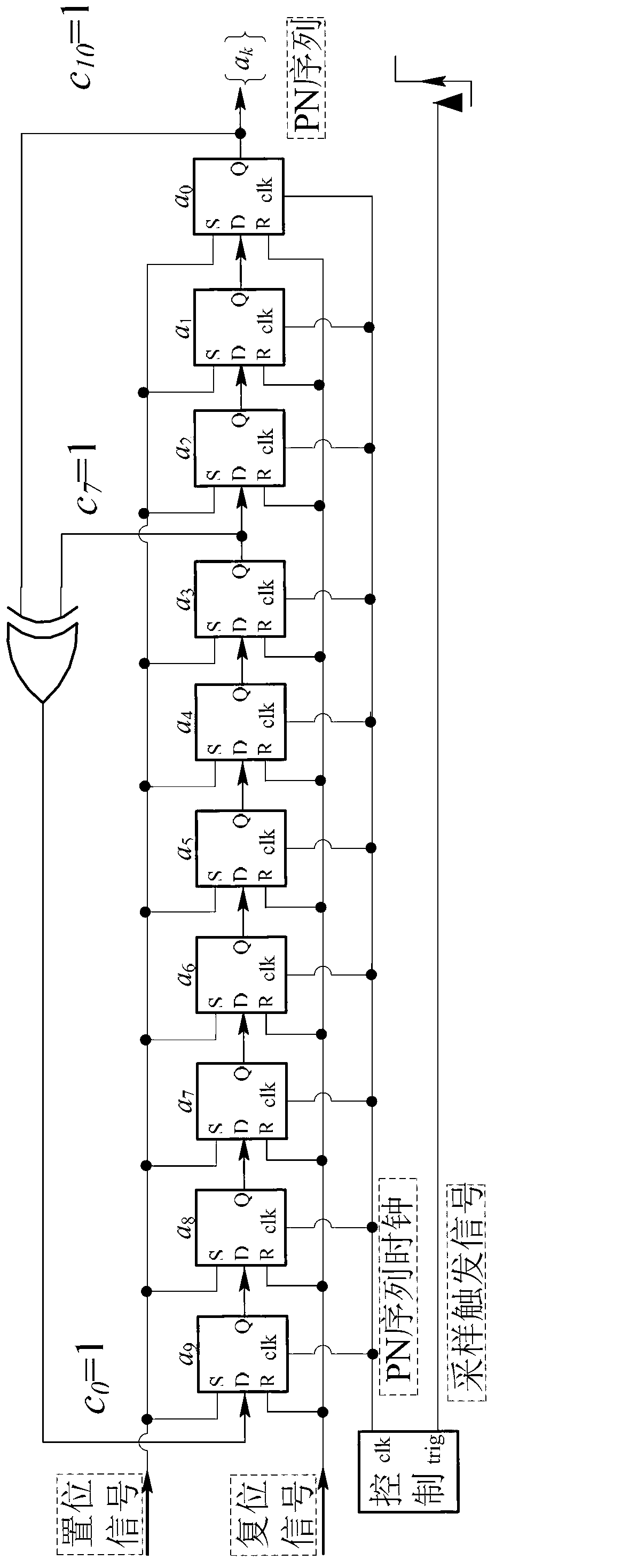

[0054] Step 1, using an m-sequence generator embedded in the FPGA to generate an m-sequence; and using the FPGA to generate a trigger signal synchronously;

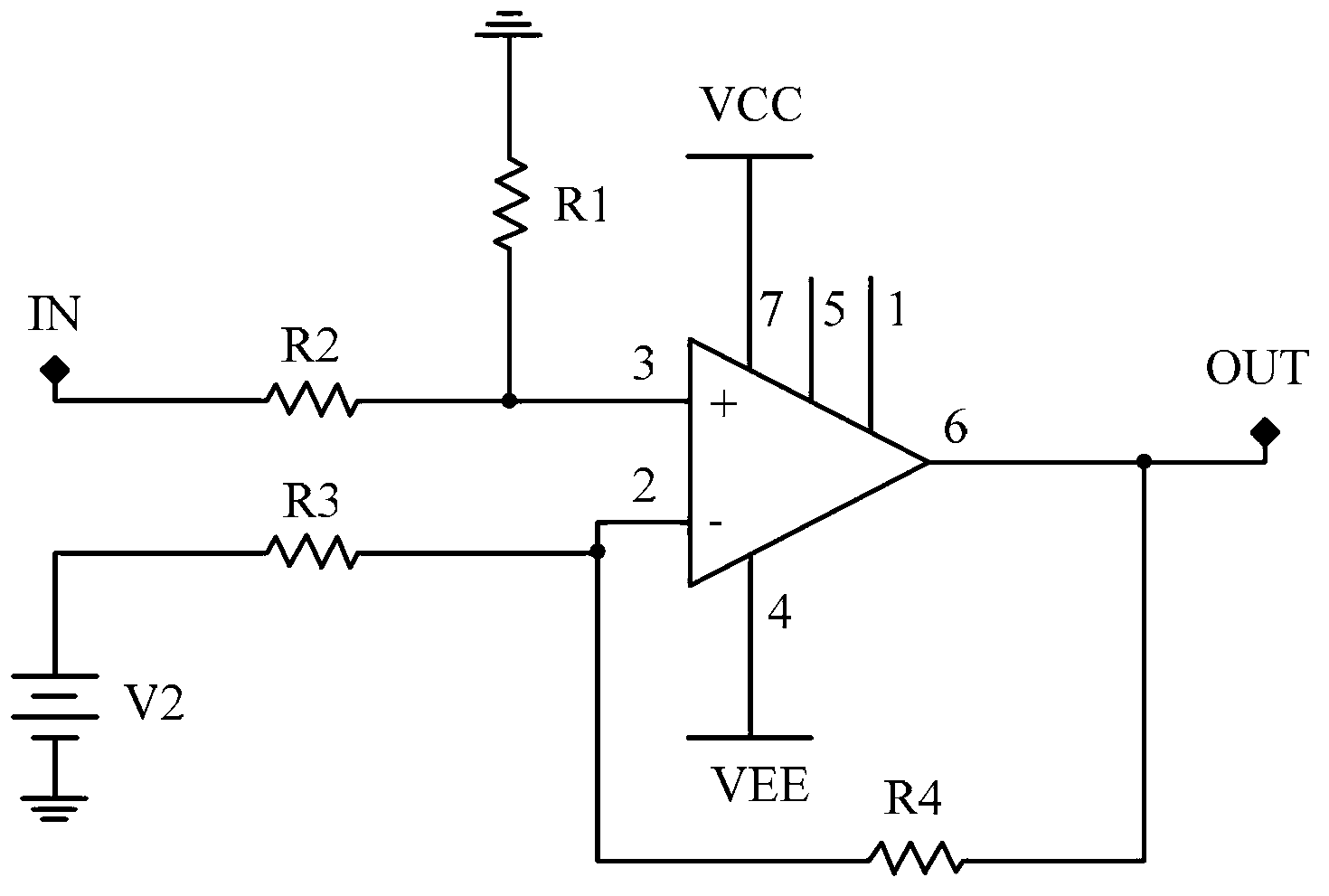

[0055] Step 2, using the signal conditioning circuit to perform signal conditioning on the m-sequence generated in step 1, to obtain the conditioned m-sequence;

[0056] Step 3, mixing the conditioned m-sequence obtained in step 2 with the measured sparse signal using a multiplier to obtain a mixed frequency signal;

[0057] Step 4, using a low-pass filter to low-pass filter the mixed frequency signal obtained in step 3 to obtain a low-pass filtered signal;

[0058] Step 5, using the trigger signal generated in step 1 to trigger the sampling circuit, and using the sampling circuit to sample the low-pass filtered signal obtained in step 4 to obtain a sampling result;

[0059] St...

specific Embodiment approach 2

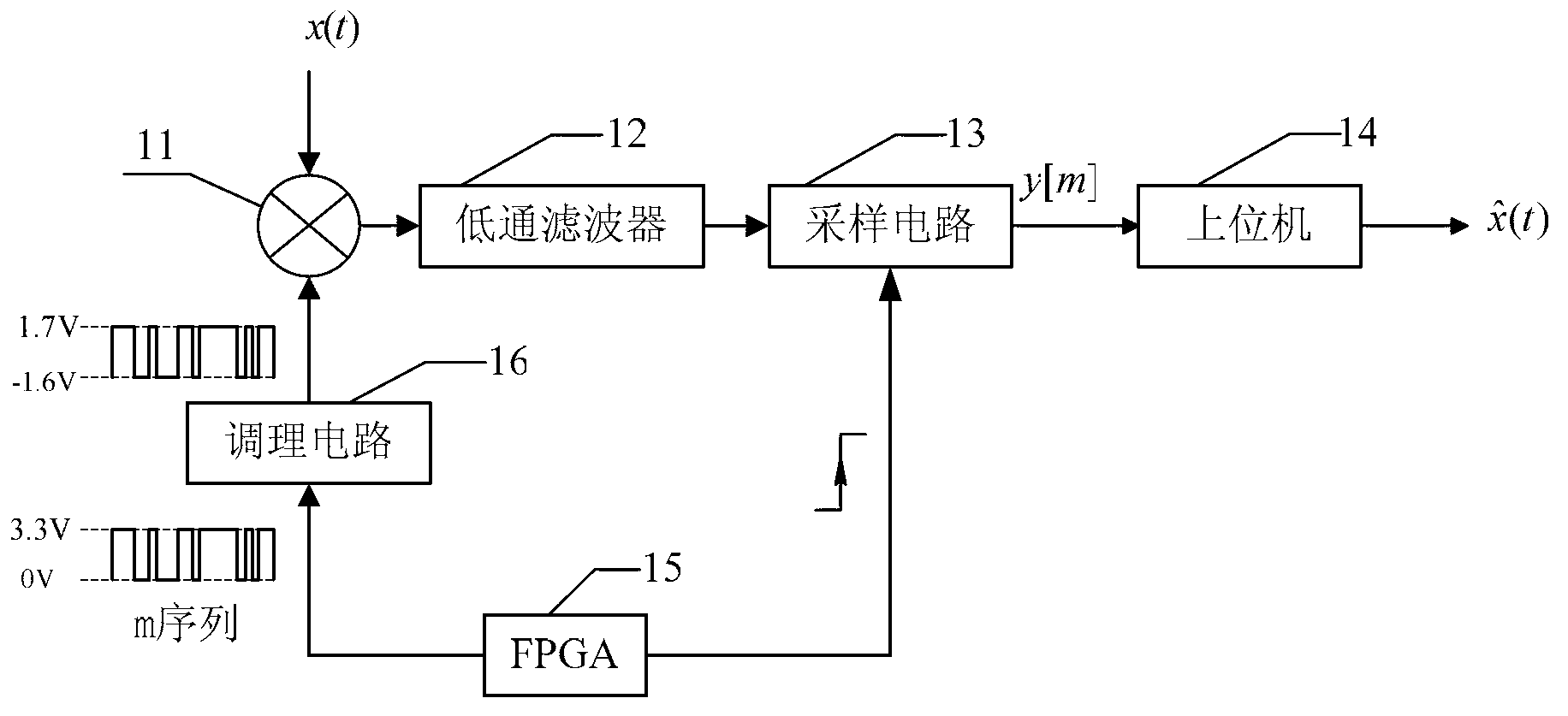

[0060] Specific embodiment two, the implementation device of sparse signal subsampling method based on compressed sensing, it comprises FPGA15, conditioning circuit 16, multiplier 11, low-pass filter 12, sampling circuit 13 and host computer 14;

[0061] Described FPGA15 is embedded with m sequence generator, and described m sequence generator is used for producing m sequence;

[0062] The m sequence output end of described FPGA15 is connected with the signal input end of signal conditioning circuit 16; The signal output end of described signal conditioning circuit 16 is connected with No. 1 signal input end of multiplier 11; No. two signal of described multiplier 11 The input end is used for receiving measured sparse signal; The signal output end of described multiplier 11 is connected with the signal input end of low-pass filter 12; The signal output end of described low-pass filter 12 is connected with the signal input end of sampling circuit 13 Connection; the signal outpu...

specific Embodiment approach 3

[0063] Specific Embodiment 3. The difference between this specific embodiment and the realization device of the compressive sensing-based sparse signal undersampling method described in specific embodiment 2 is that the model of FPGA 15 is EP2C8Q208.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More