Bandwidth adjustment method, sending chip and system

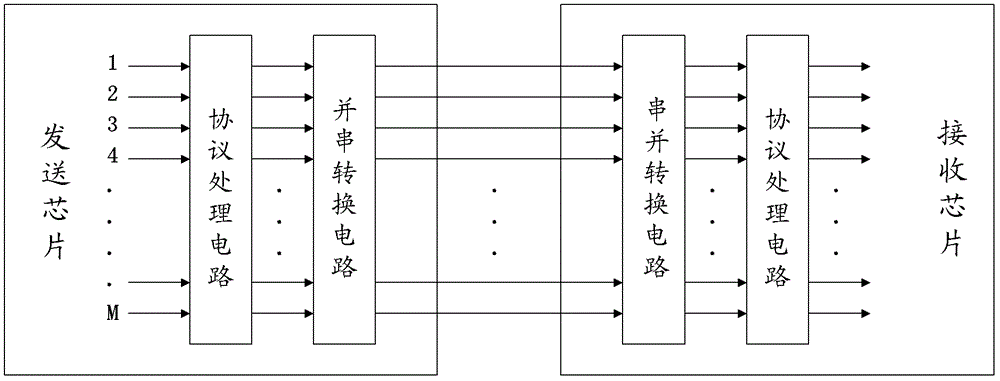

A bandwidth adjustment and chip technology, applied in the field of communications, can solve problems such as bandwidth reduction, protocol interface configuration delay, data delay, etc., to achieve the effect of reducing bandwidth and avoiding data delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

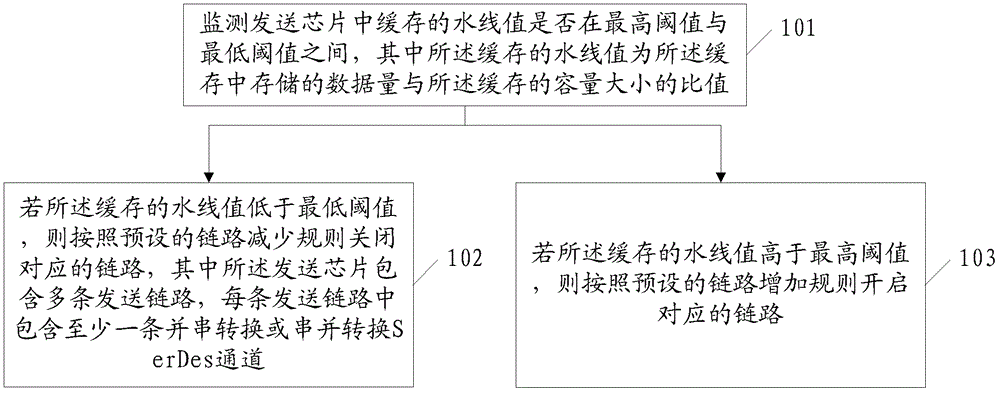

[0029] An embodiment of the present invention provides a bandwidth adjustment method, such as figure 2 shown, including:

[0030] 101. Monitor whether the waterline value of the cache in the sending chip is between the highest threshold and the lowest threshold, where the waterline value of the cache is a ratio of the amount of data stored in the cache to the capacity of the cache.

[0031] It should be noted that the waterline value of the cache can be based on the relationship between the amount of data in the current cache and the capacity of the cache itself, or the ratio of the inflow speed and outflow speed of data in the cache, or other values. The embodiment of the present invention does not limit the parameter of the expression form, as long as it can be used to reflect whether the data transmission of the sending chip is smooth, and indirectly reflect the degree of congestion of service data transmission between chips. The highest threshold and the lowest threshold...

Embodiment 2

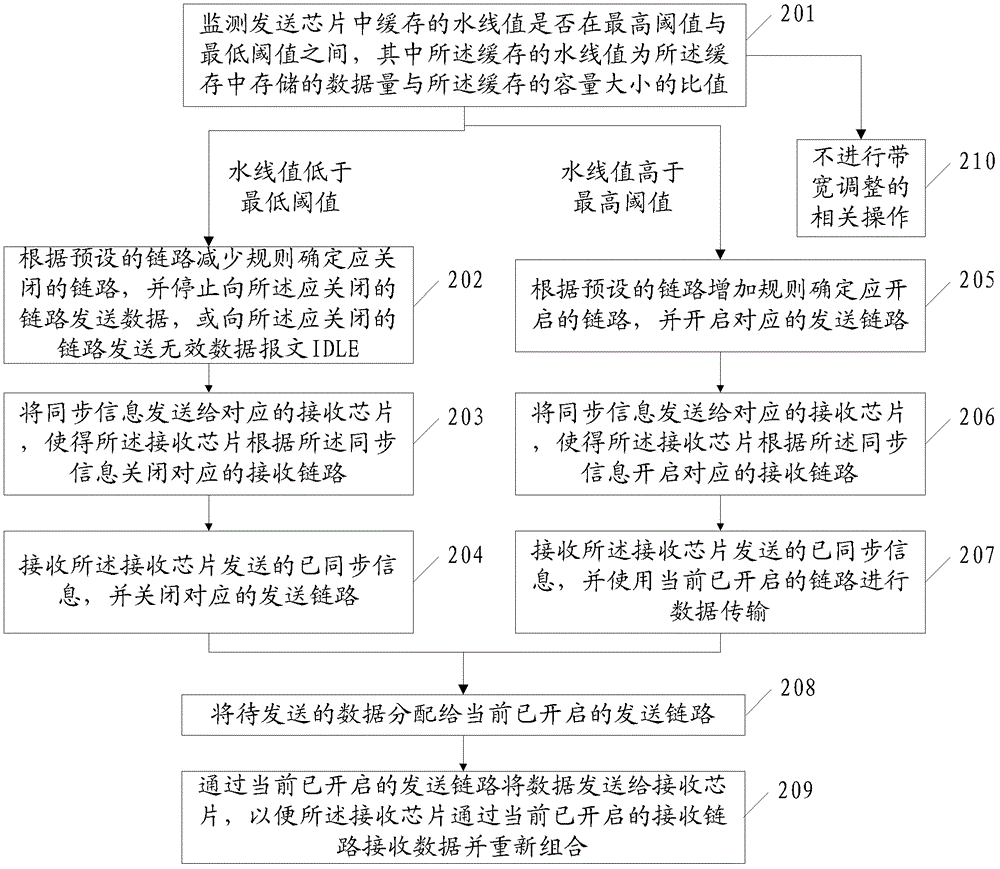

[0041] An embodiment of the present invention provides a bandwidth adjustment method, such as image 3 shown, including:

[0042] 201. Monitor whether the waterline value of the cache in the sending chip is between the highest threshold and the lowest threshold, where the waterline value of the cache is the ratio of the amount of data stored in the cache to the capacity of the cache; if the If the waterline value of the cache is lower than the lowest threshold, then perform step 202; if the waterline value of the cache is higher than the highest threshold, then perform step 205; if the waterline value of the cache is between the highest threshold and the lowest threshold , then step 210 is executed.

[0043] Among them, the data to be sent by the sending chip can be temporarily stored in the cache for sending, and the data in the cache will also be sent out through the sending link. When the sending bandwidth is low to a certain extent, the outflow speed of the data in the c...

Embodiment 3

[0072] An embodiment of the present invention provides a sending chip, such as Figure 4 As shown, it includes: a monitoring unit 31 , a closing unit 32 and an opening unit 33 .

[0073] The monitoring unit 31 is configured to monitor whether the waterline value of the cache in the sending chip is between the highest threshold and the lowest threshold, wherein the waterline value of the cache is equal to the amount of data stored in the cache and the capacity of the cache ratio.

[0074] The closing unit 32 is configured to close the corresponding link according to the preset link reduction rule when the monitoring unit 31 detects that the waterline value of the cache is lower than the minimum threshold, wherein the sending chip includes multiple sending link, and each transmit link includes at least one parallel-to-serial conversion or serial-to-parallel conversion SerDes channel.

[0075] The opening unit 33 is configured to open a corresponding link according to a preset ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More