Phase-locked loop and method and circuit for producing clock thereof

A phase-locked loop and adder technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of high switching noise, limited clock adjustment range and adjustment accuracy, and high chip power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

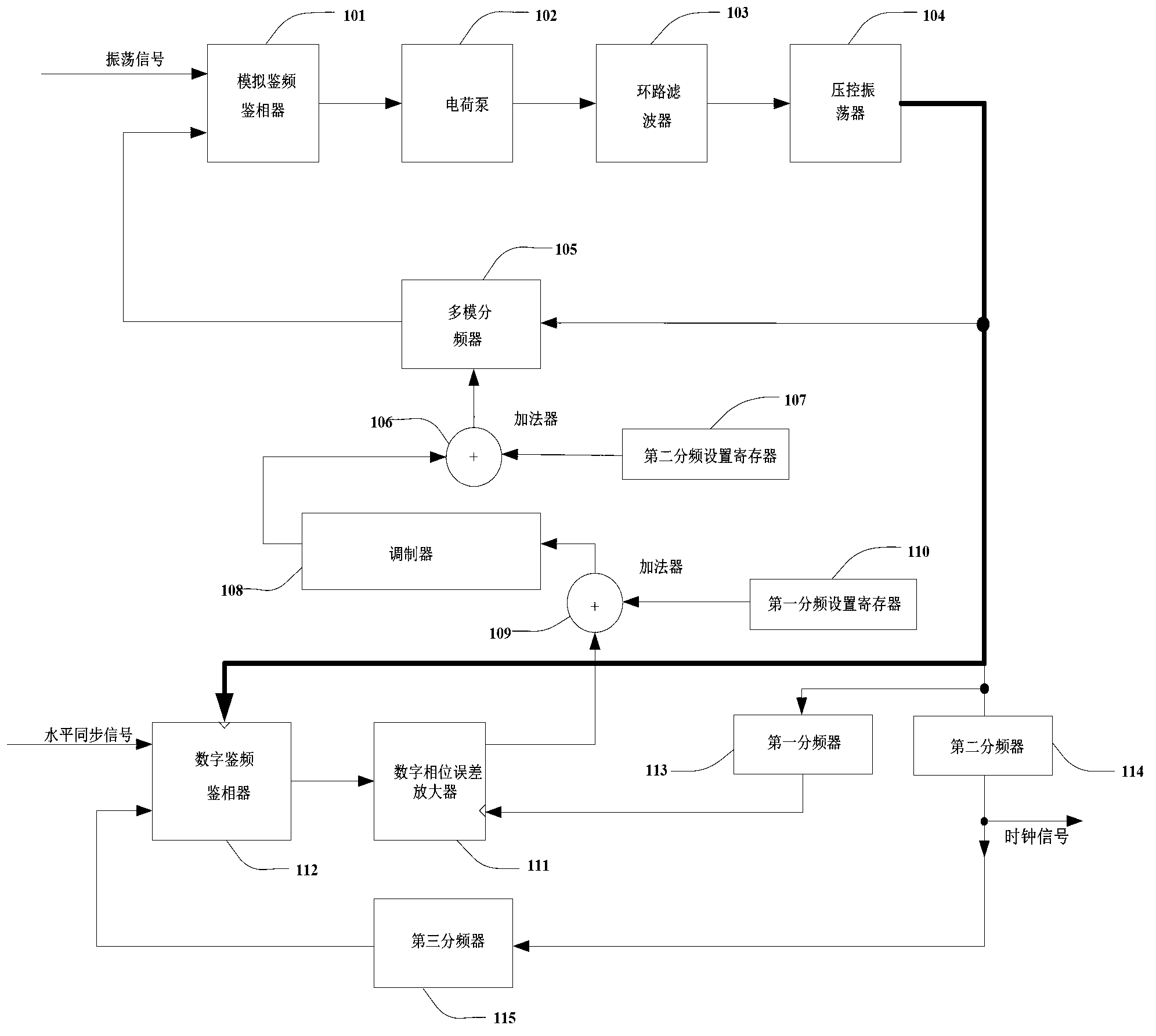

[0026] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

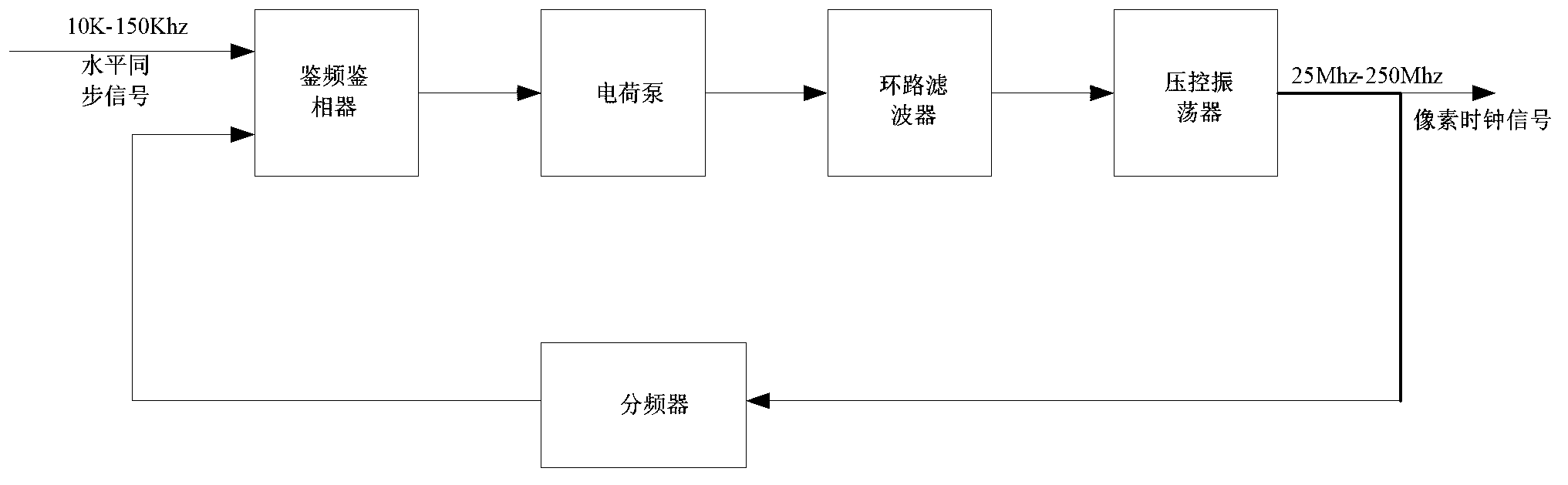

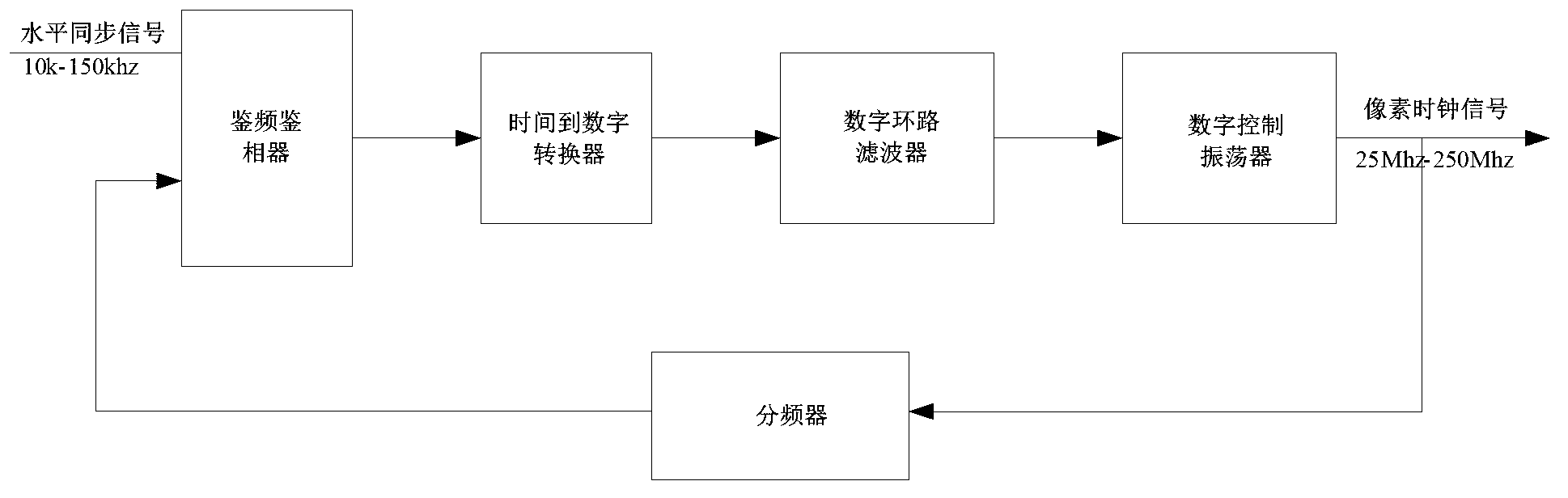

[0027] The phase-locked loop of the present invention includes an analog phase-locked loop unit and a digital control unit, and the analog phase-locked loop unit includes a modulator, a multi-mode frequency divider, an analog frequency and phase detector and a voltage-controlled oscillator.

[0028] image 3 It is a schematic structural diagram of a phase-locked loop circuit system according to an embodiment of the present invention. Such as image 3 As shown, the phase-locked loop circuit system includes an analog phase-locked loop unit, and the analog phase-locked loop unit includes an analog frequency and phase detector 101, a voltage-controlled oscillator 104, a multi-mode frequency divider 105 and an adder 106; digital control unit, the digital control unit includes a digital frequency detector 112 and a digital...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More