SRAM timing sequence test circuit and test method

A technology for timing testing and testing circuits, applied in static memory, instruments, etc., can solve the problems of uncontrollable accuracy, time-consuming, and uncertainty of Tcq measurement, saving time for selection and adjustment, simple measurement, and small error. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The technical solutions of the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings of the present invention.

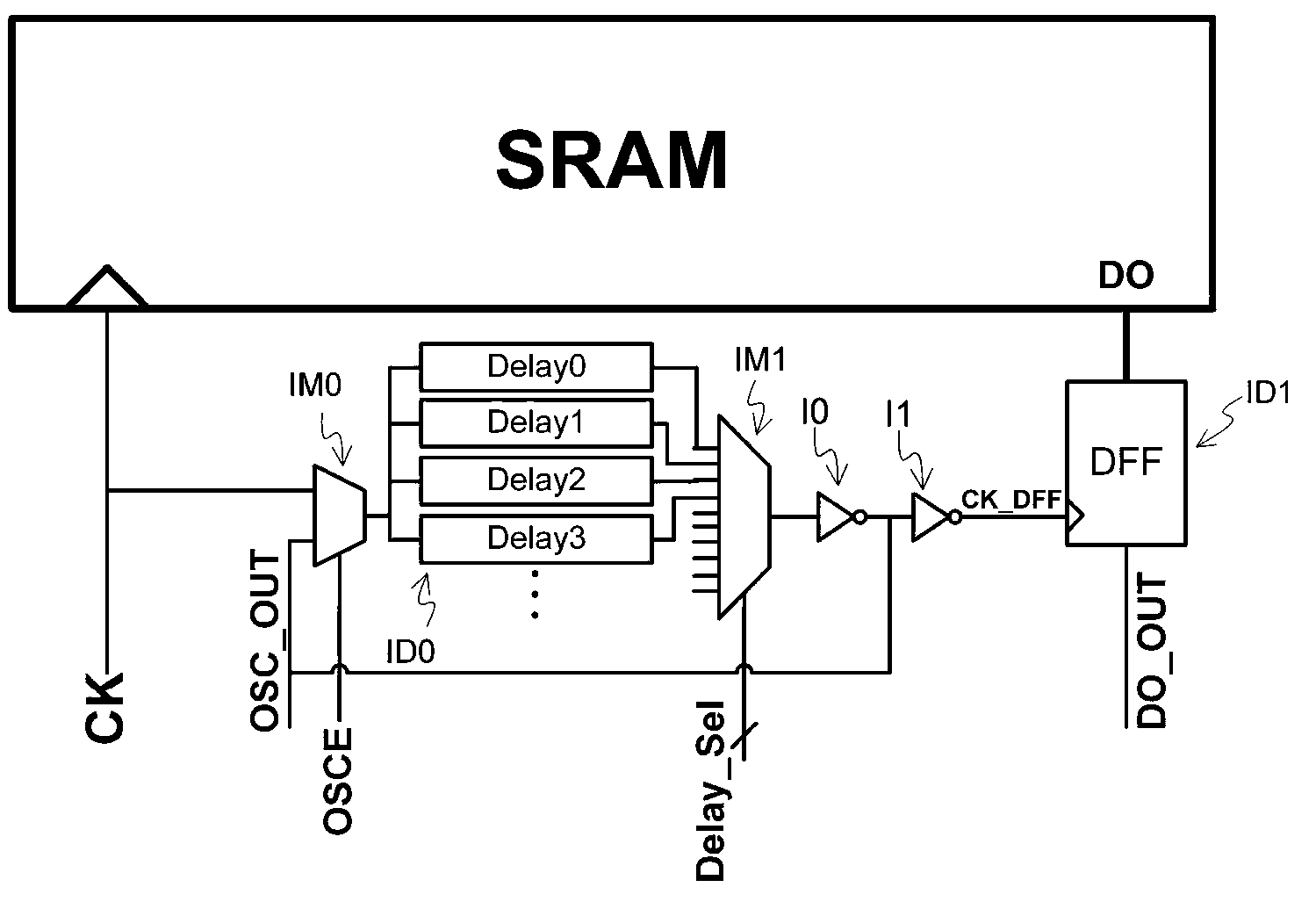

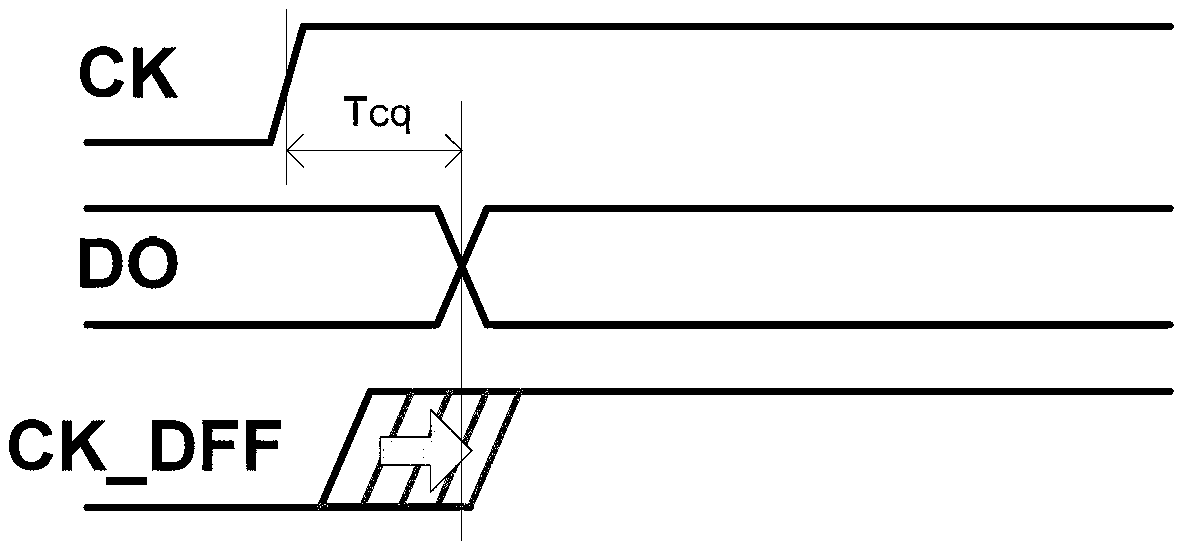

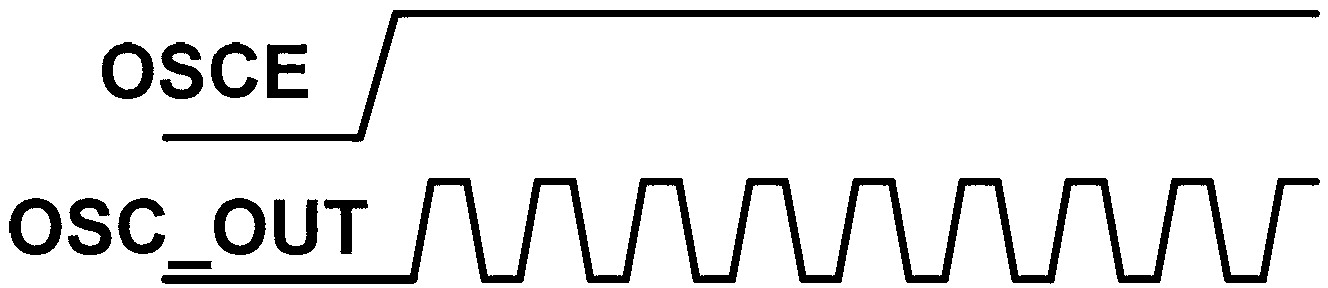

[0037] A SRAM timing test circuit disclosed by the present invention, by forming two ring oscillation circuits, respectively measuring the output oscillation periods of the two ring oscillation circuits, thereby accurately obtaining the time value of the SRAM storage unit reading data, to overcome the existing Tcq The measurement method has the problems of low measurement accuracy, cumbersome process, time-consuming and low efficiency.

[0038] Such as Figure 4 As shown, a SRAM timing test circuit disclosed in the present invention includes: SRAM storage unit I10, a first mode switching circuit I5, an edge signal trigger circuit, a second mode switching circuit I8, an address generating circuit I9 and a third mode switching circuit I11, the SRAM storage unit I10 is a clock synchroniza...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More