Method for Detecting Via Underetch and Via Missing Defects

An etching and semiconductor technology, used in semiconductor/solid-state device testing/measurement, electrical components, semiconductor/solid-state device manufacturing, etc., can solve problems such as providing effective reference, restricting yield improvement, and low accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

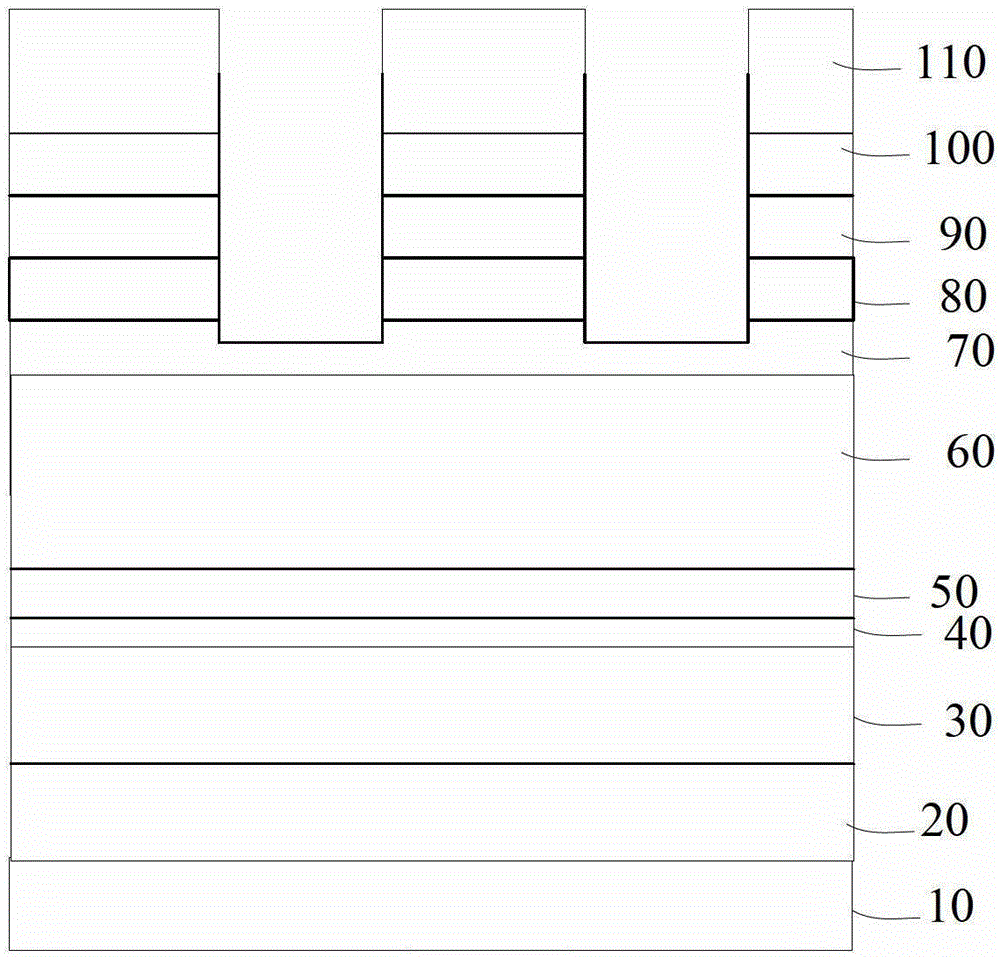

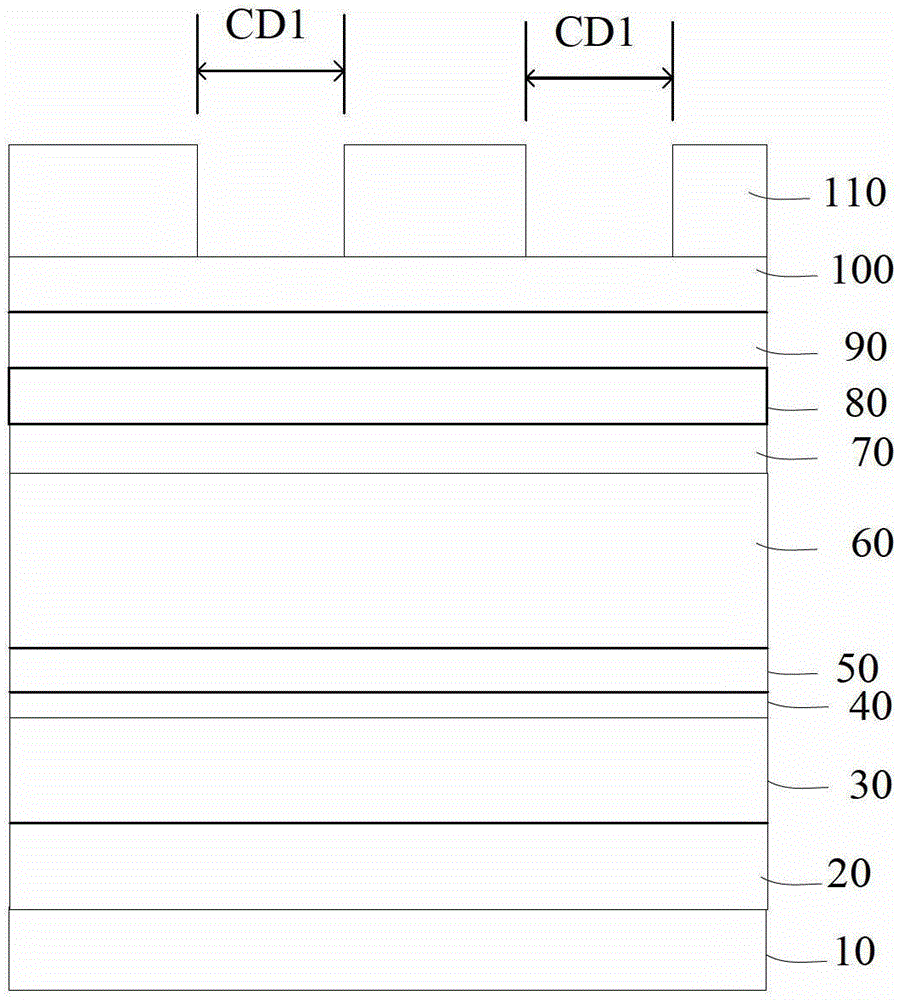

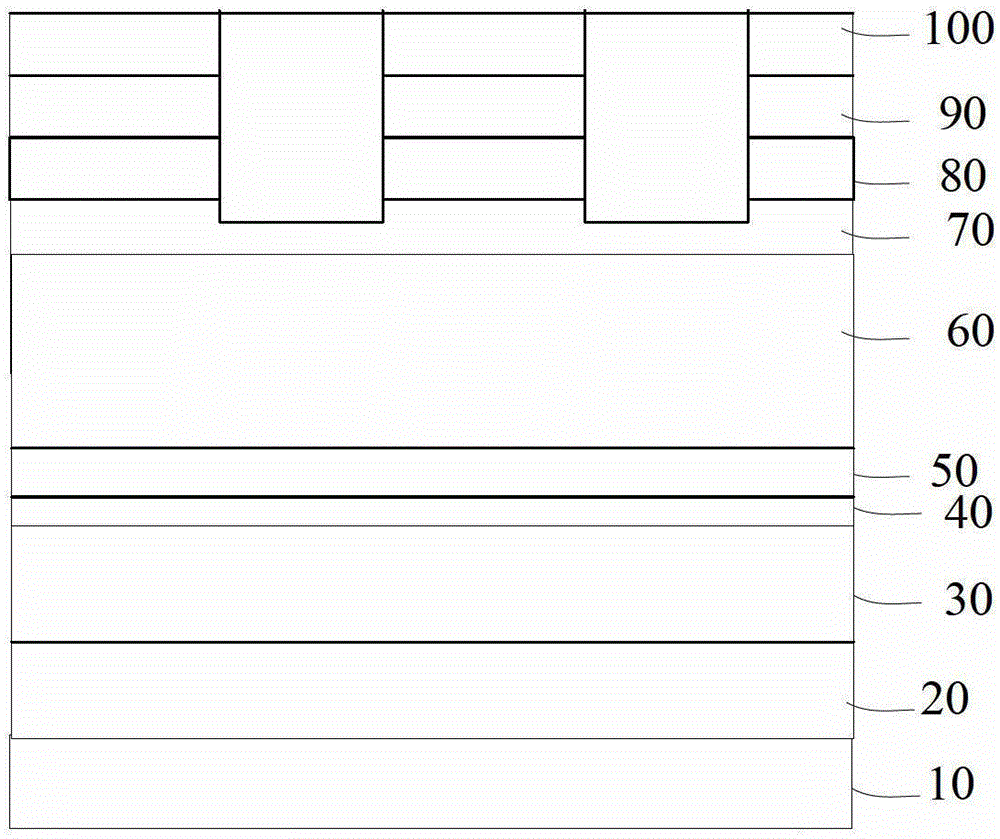

[0028] The present invention is aimed at etching the hard mask (HardMaskEtch) and then etching the through hole (AllinOneEtch). The following technical principles are applied to grow a metal silicide on a wafer with a PMOS structure on the substrate, and grow an etching process to etch the through hole. The thickness of the dielectric layer that needs to be consumed during the hole, the same mask is used for the hard mask etching and the through hole etching, and the electron beam defect scanner is used for inspection after copper filling and planarization. The specific implementation steps are as follows:

[0029] Firstly, the surface of the wafer is implanted with N-type well region ions and P-type source-drain ions by non-photoresist ion impl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More