Trench preparation method

A trench and barrier layer technology, applied in the field of trench preparation, can solve the problems of integrated circuit damage, influence on integrated circuit performance, poor coverage, etc., and achieve the effect of avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

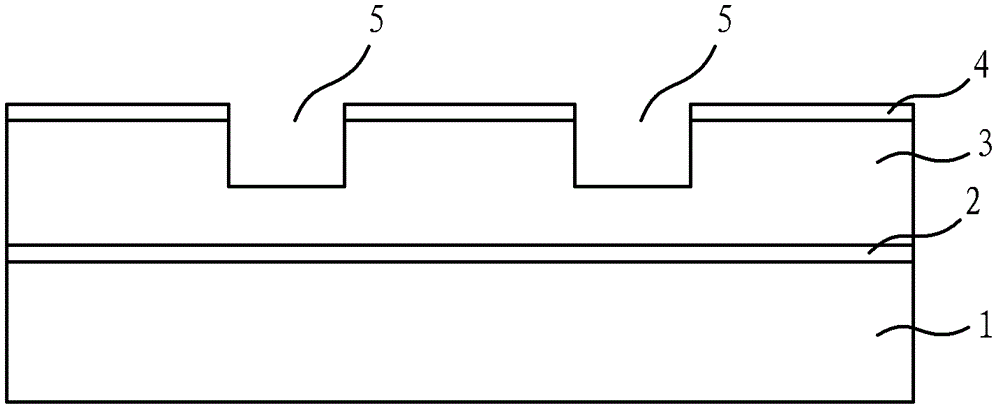

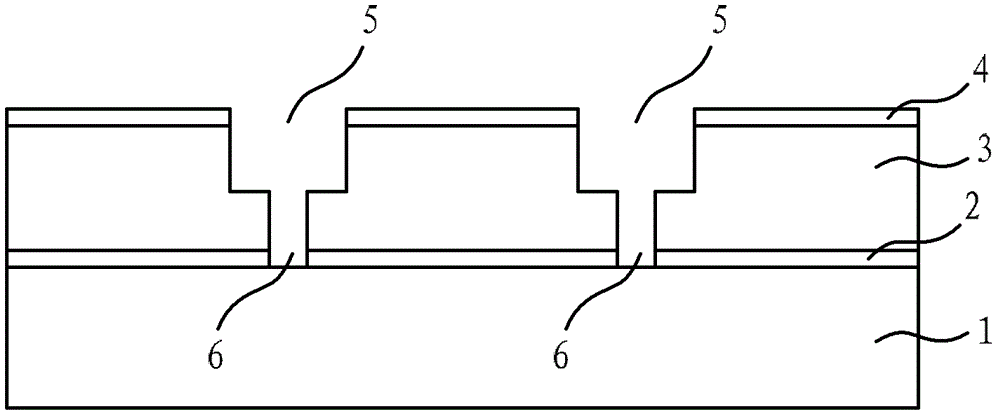

[0042] Such as Image 6 Shown is the flow chart of the steps of the groove preparation method of the present invention, Figure 7 to Figure 12 for corresponding to Image 6 The evolution diagram of the device structure at each step in the process, the following combination Image 6 as well as Figure 7 to Figure 12 The trench preparation method of the present invention is introduced in detail, including the preparation of through holes. The method mainly includes:

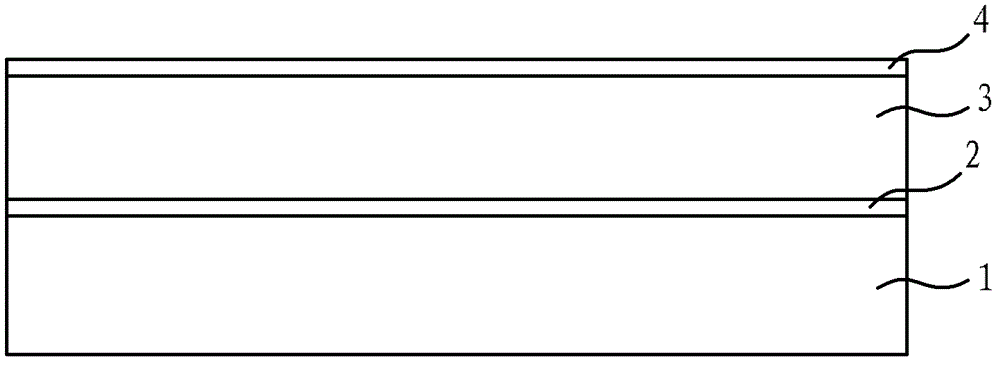

[0043] Step 1: A semiconductor device 1 is provided, and a first barrier layer 2, an interlayer dielectric layer 3, a second barrier layer 4 and a metal mask layer 9 are sequentially deposited on the semiconductor device 1, referring to Figure 7 shown.

[0044] Among them, the semicon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com