Method of Shrinking Critical Dimensions in Dry Etching of Polysilicon Gate

A critical dimension and dry etching technology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as impact on subsequent processes, PR collapse, wafer surface defects, etc., and achieve enhanced etching resistance , control the degree of shrinkage, and meet the effect of process requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

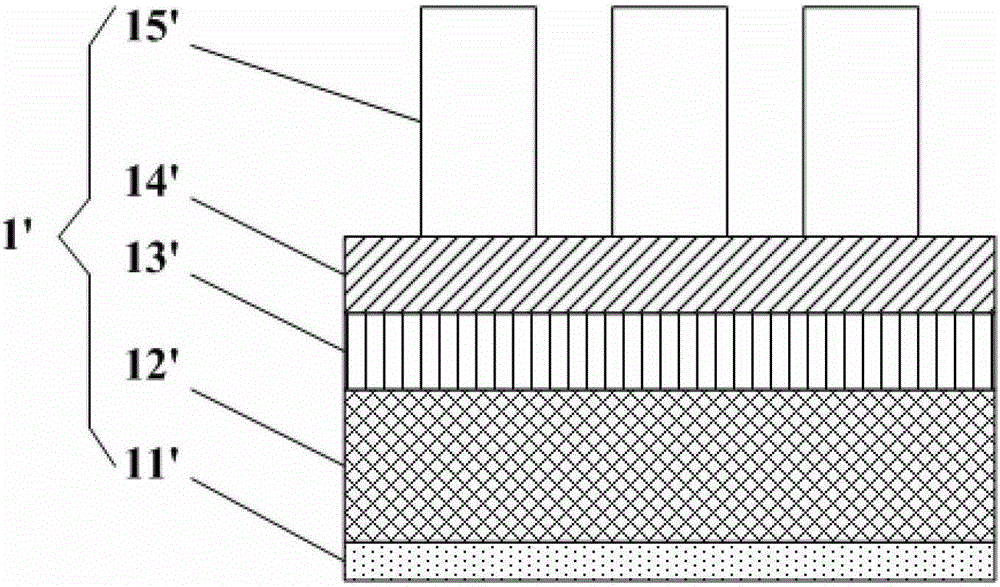

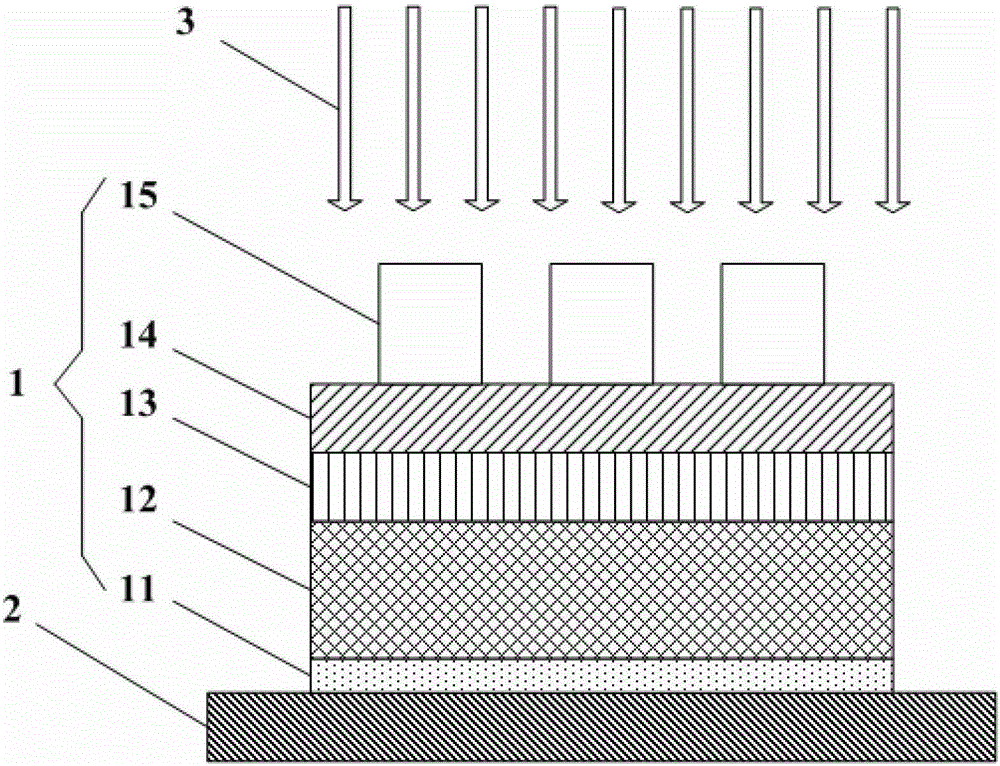

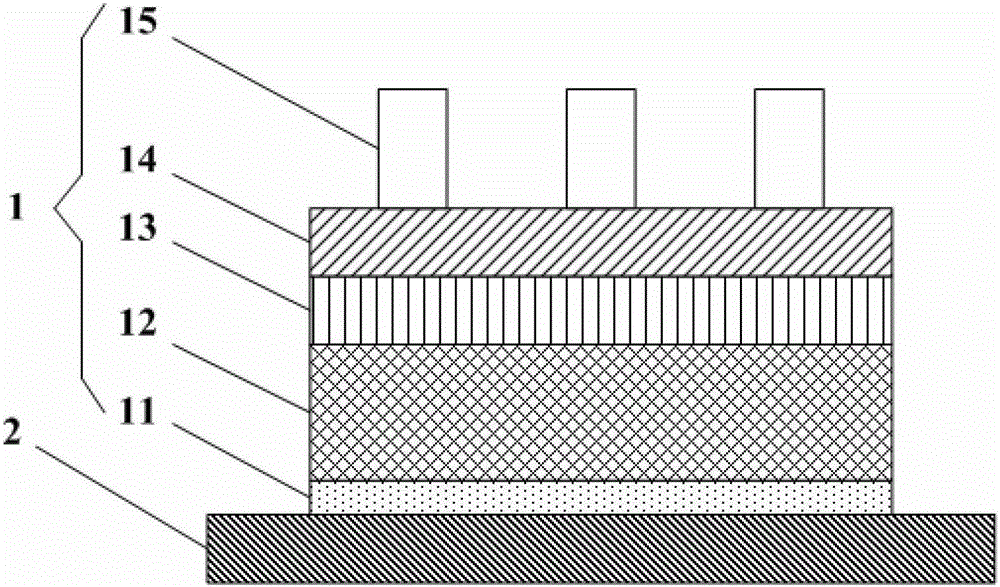

[0025] As an embodiment of the present invention, this embodiment relates to a method for shrinking critical dimensions in polysilicon gate dry etching, which includes the following steps: placing the exposed and developed wafer on the bottom plate of a back-baking device; At the same time, carry out back-baking and electron beam bombardment on the above-mentioned exposed and developed wafers, and control the photoresist shrinkage rate according to the process requirements; after the photoresist shrinkage rate meets the process requirements, stop the back-baking and electron beam bombardment of the above-mentioned exposed and developed wafers Electron beam bombardment: cooling the wafer after the exposure and development of the above stop back baking and electron beam bombardment to normal temper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More