Method for Improving Gap Filling Ability of Pre-Metal Dielectric Layer

A technology of pre-metal dielectric layer and filling capability, applied in electrical components, electric solid-state devices, semiconductor/solid-state device manufacturing, etc., can solve problems such as uneven filling of materials and failure of semiconductor devices, reduce void defects, and improve filling capability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

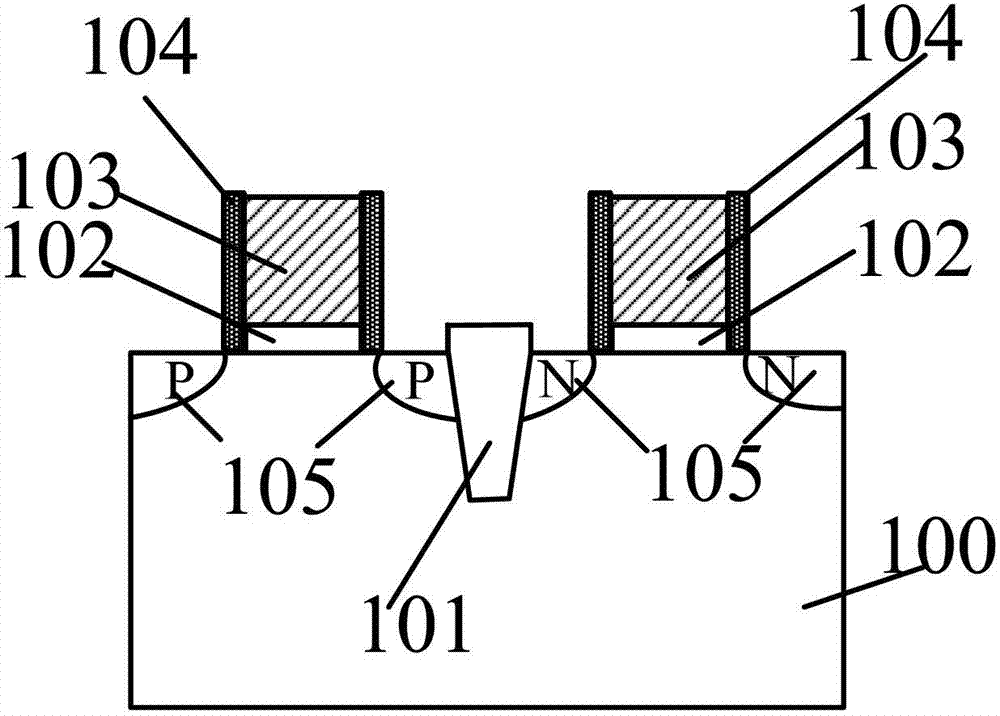

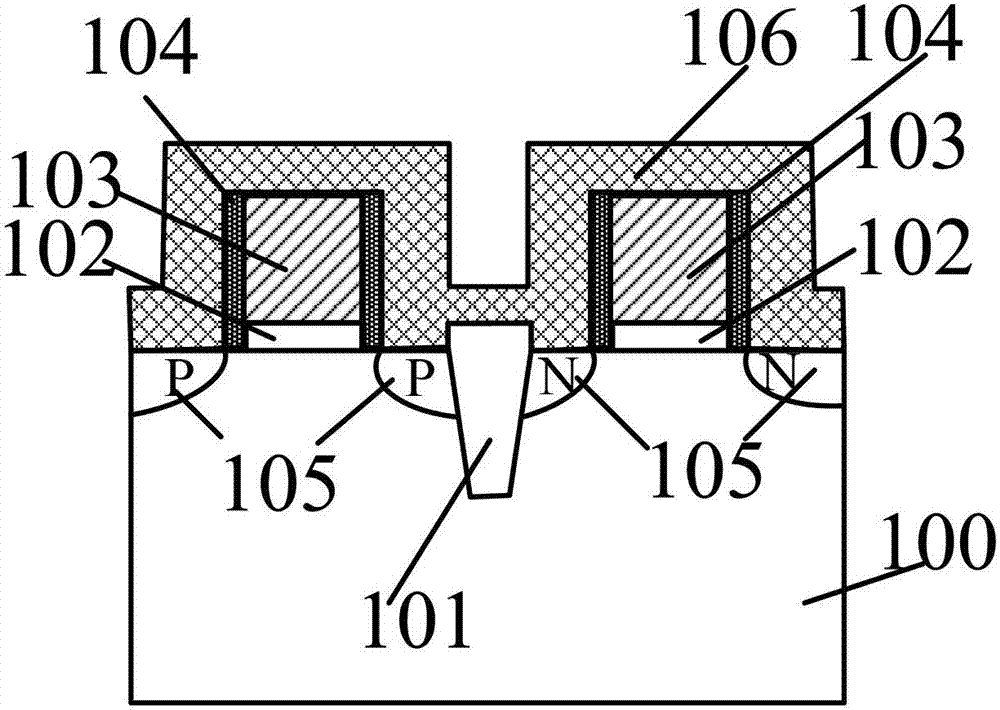

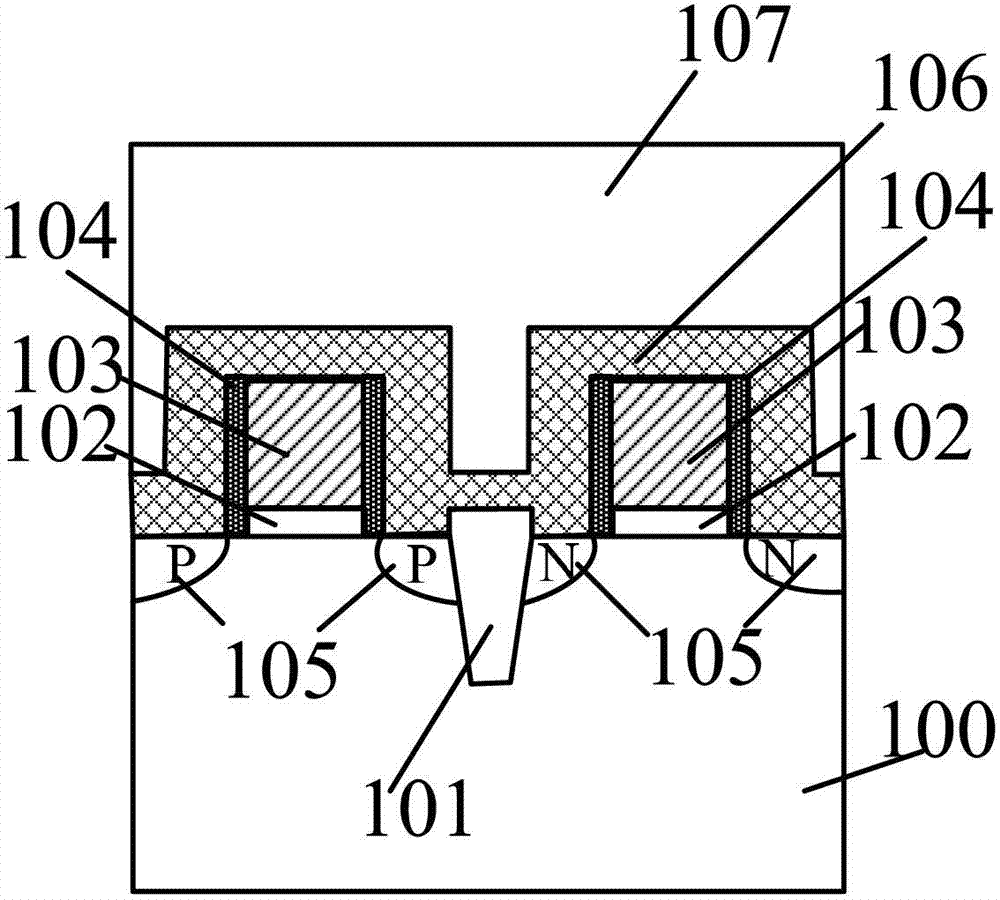

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0026] Studies have shown that under normal circumstances, the growth rate of the pre-metal dielectric layer on the surface of the silicon oxide layer is faster than that on the surface of the stressed silicon nitride layer, but after fluorine treatment on the surface of the stressed silicon nitride layer and the surface of the silicon oxide layer, the pre-metal layer The dielectric layer grows faster on the surface of the stressed silicon nitride layer than on the surface of the silicon oxide layer, so the present invention uses fluorine treatment to improve the growth selectivity ratio of the dielectric layer before the metal on the surface of the stressed silicon nitride layer and the surface of the silicon oxide layer, thereby Reach the object of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More