Preparation method of transistor with stressed channel and transistor with stressed channel

A technology of strained channels and transistors, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of high cost, complicated process, difficult strain state of strained materials, etc., and achieve the effect of stable strain and not easy to disappear

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

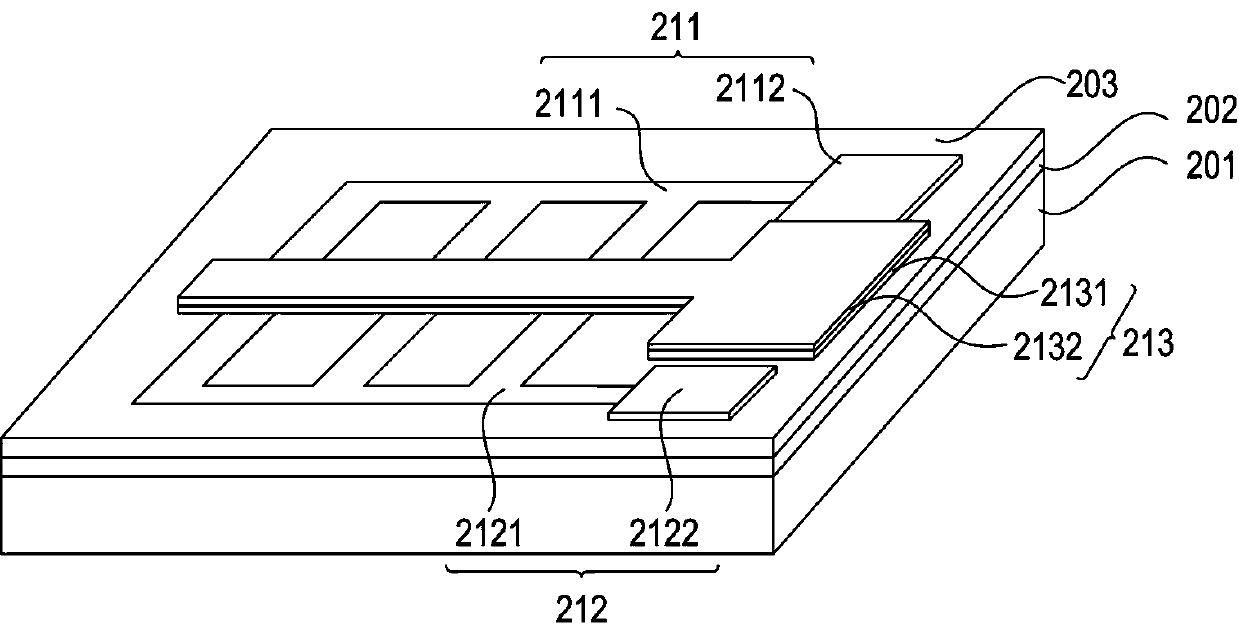

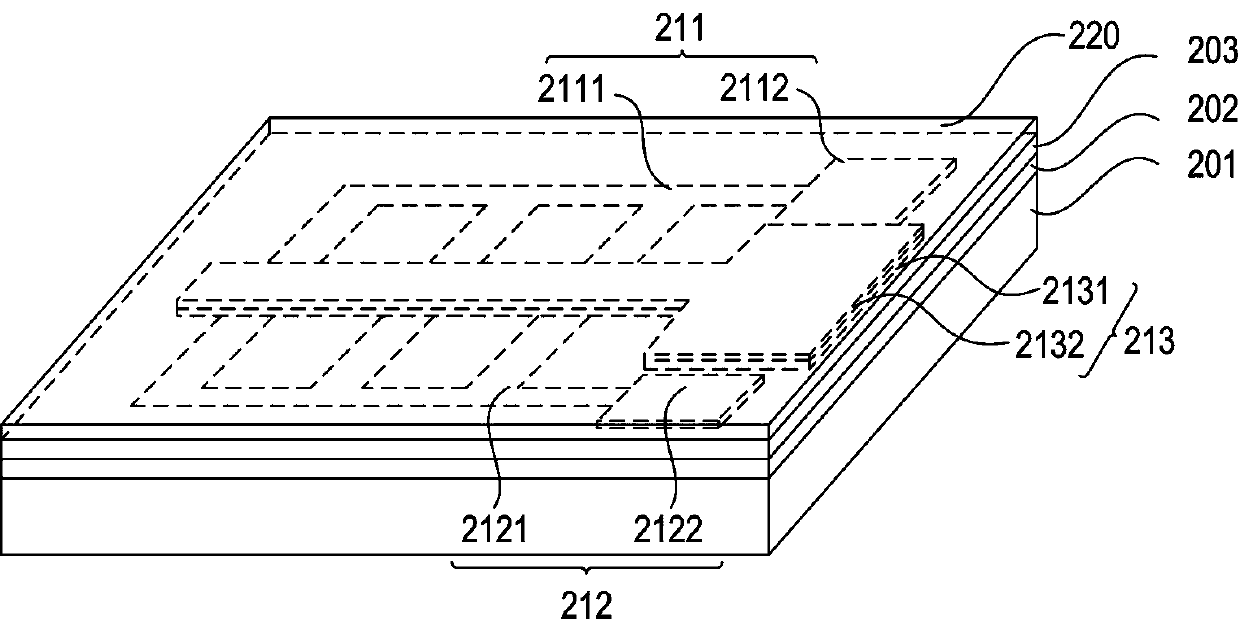

[0018] The method for manufacturing a transistor with a strained channel provided by the present invention and the specific implementation of the transistor with a strained channel will be described in detail below in conjunction with the accompanying drawings.

[0019] attached figure 1 Shown is a schematic diagram of the implementation steps of the specific embodiment of the present invention, including: step S10, providing a substrate, the substrate including a support layer, a buried layer on the surface of the support layer, and a device layer on the surface of the buried layer; step S11, forming a transistor, Including forming a source and a drain in the device layer, and forming a gate on the surface of the device layer; Step S12, forming an insulating protection layer on the surface of the device layer, and the insulating protection layer also covers the gate; Step S13, in the A stress layer is formed on the surface of the insulating protection layer, and the stress la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More