Parasitic extraction in an integrated circuit with multi-patterning requirements

An integrated circuit and multi-pattern technology, applied in electrical digital data processing, instruments, calculations, etc., can solve problems such as mask misalignment, affecting net total capacitance and coupling, and changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

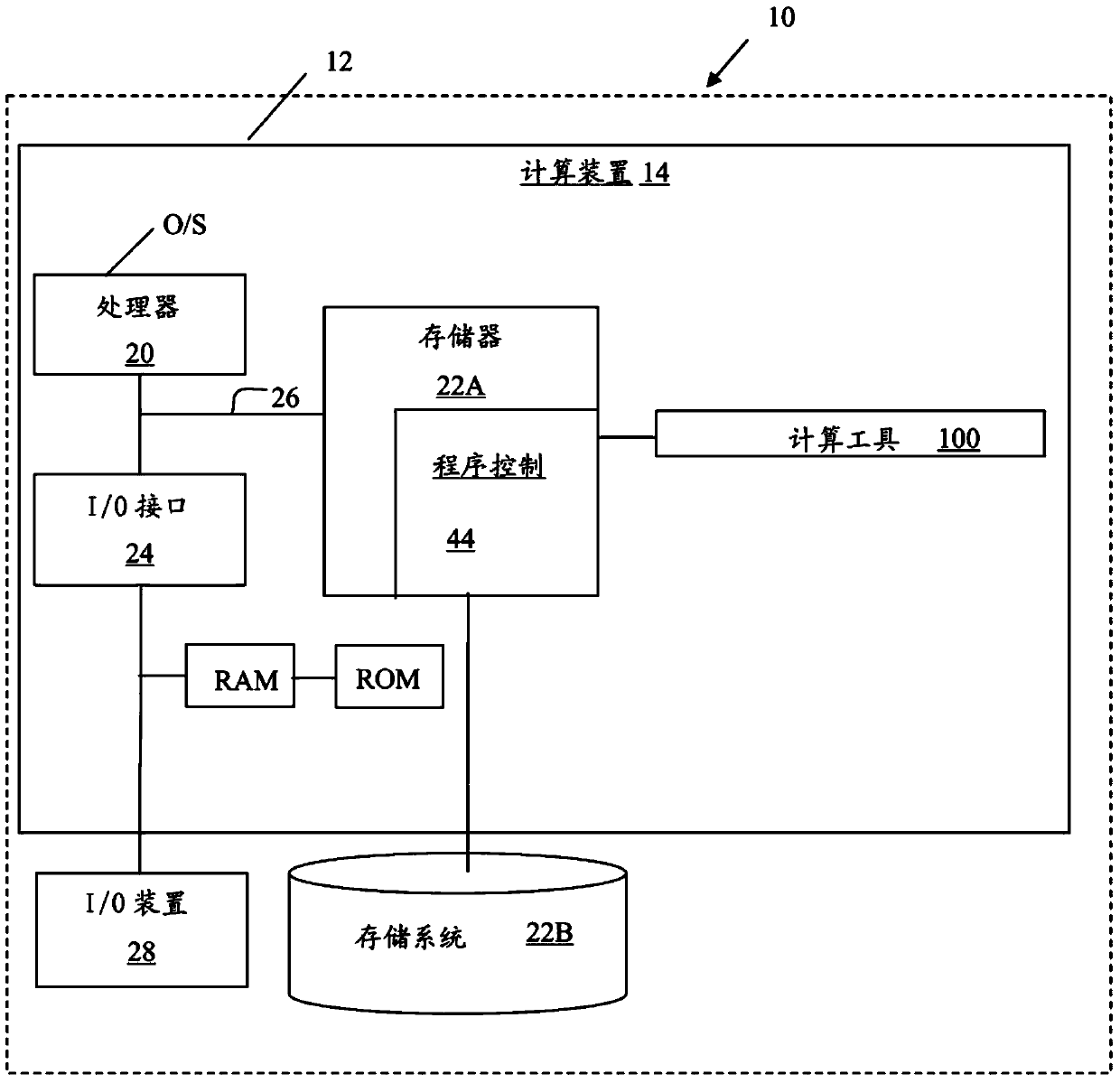

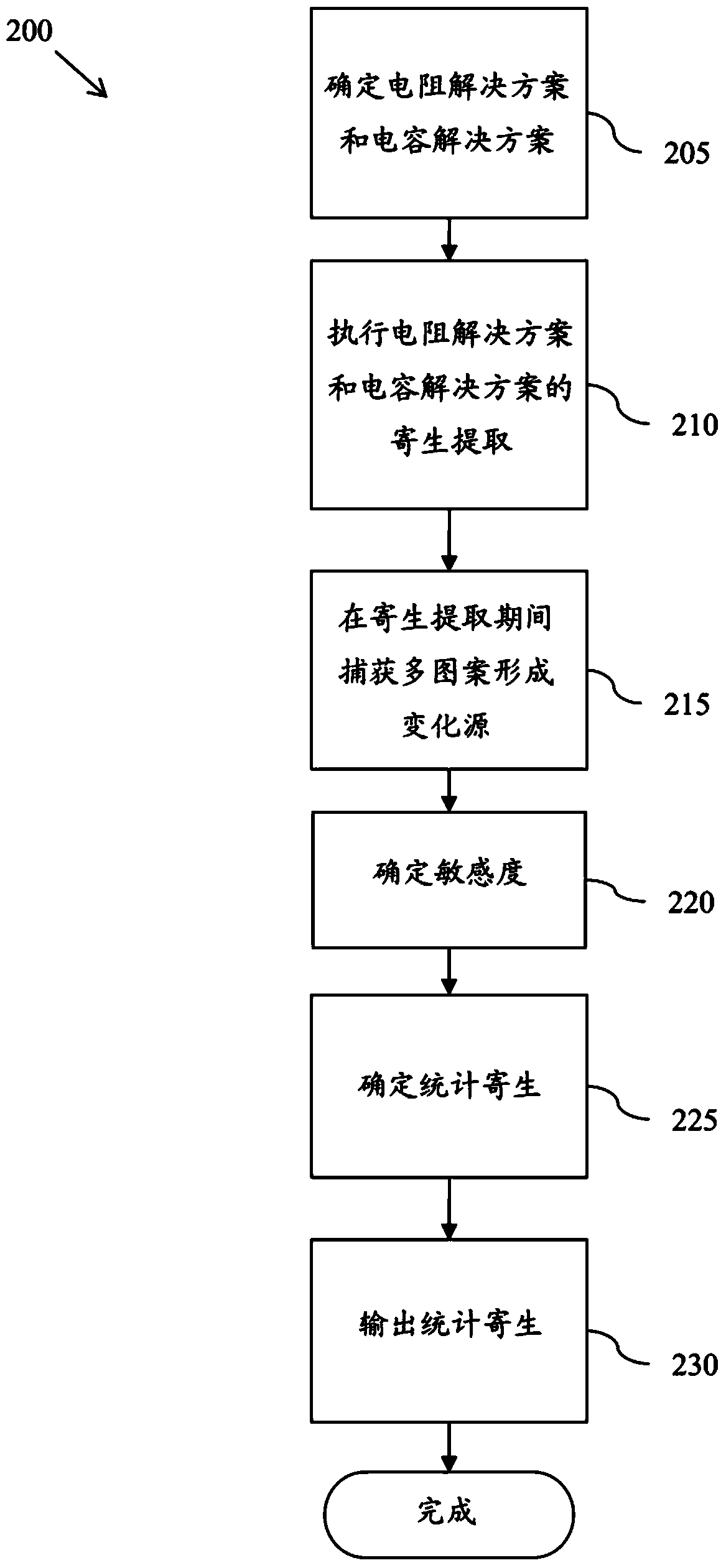

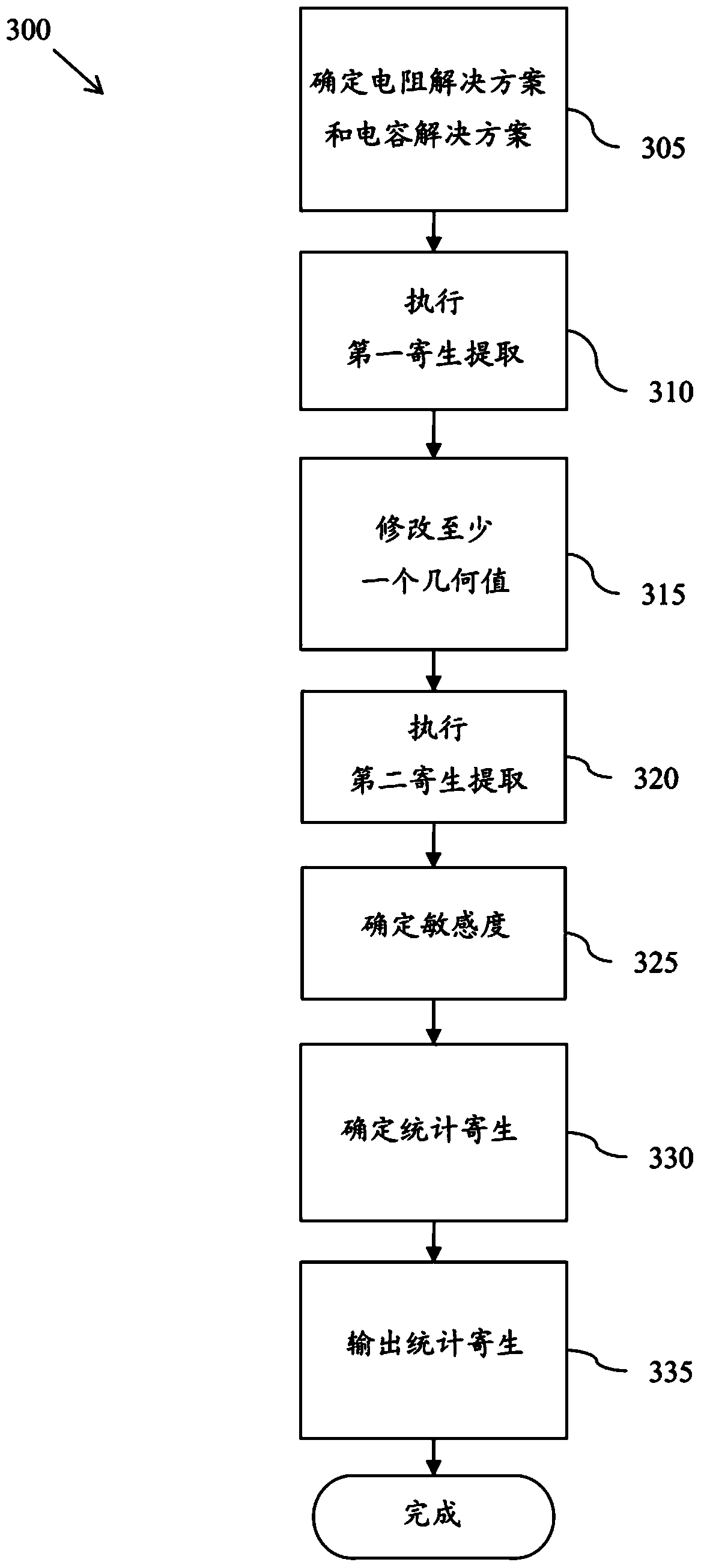

[0015] The present invention relates to systems and methods for extracting parasitics in the design of ICs with multiple patterning requirements. More specifically, implementations of the present invention provide systems and methods for modeling parasitics of multi-patterning (or color) perception to account for timing effects and handle multi-patterning in physical implementation and signoff design flows. In some embodiments, multiple patterning sources of each of the resistive and capacitive solutions may be captured during parasitic extraction. In additional or alternative embodiments, at least one geometric value may be modified to each vector of parameters identified in the IC design based on an offset of values that facilitate multi-patterning for a given layer of the IC design. new value. Advantageously, the systems and methods of the present invention take into account a simple model of the parasitics of statistical color perception in vector form or collapsed vect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More