Fin field effect transistor and method of forming the same

A technology of fin field effect transistors and fins, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficult control of the threshold voltage of fin field effect transistors, and improve electrical isolation performance and process The effect of simplicity and simple process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] It is difficult to control the threshold voltage of the field effect transistor of the fin field effect transistor formed in the prior art.

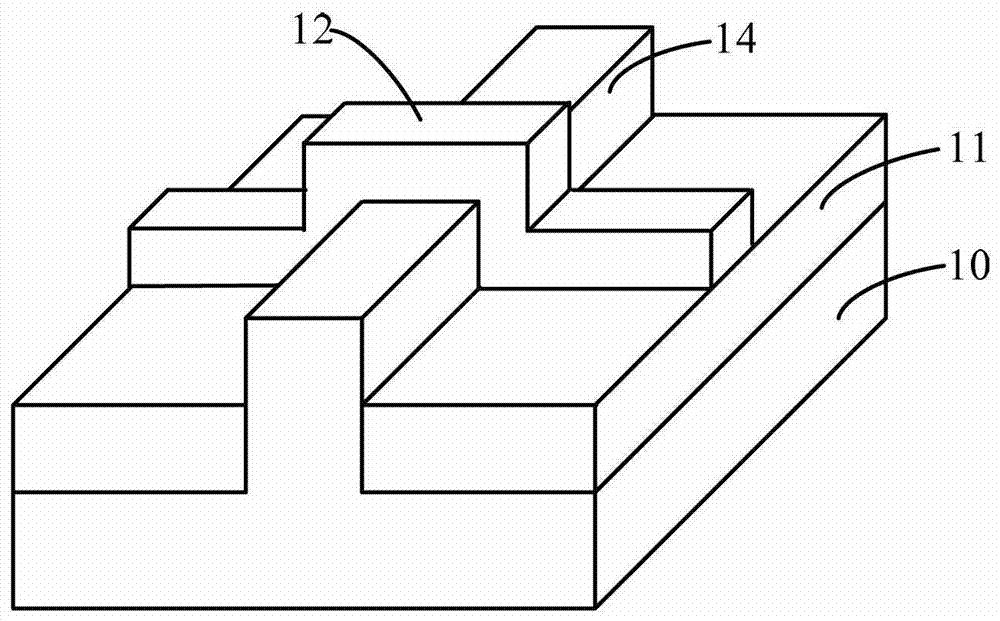

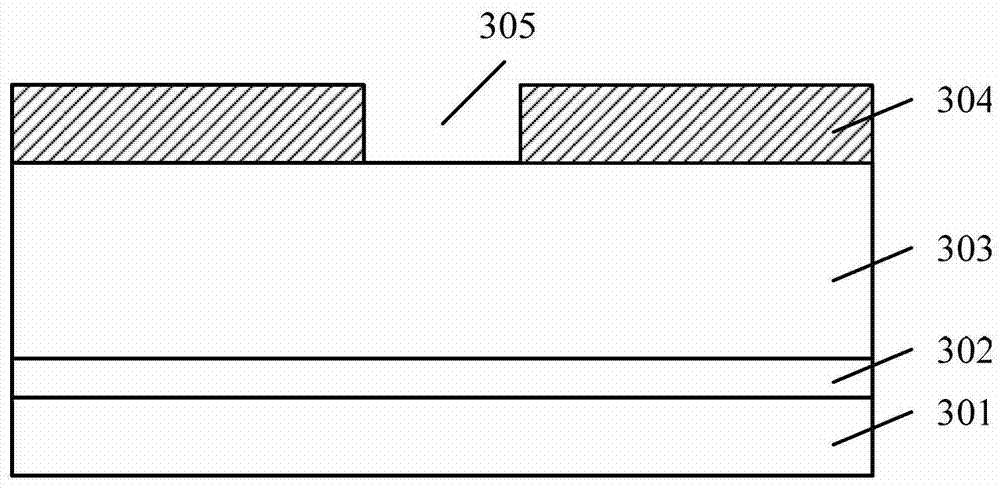

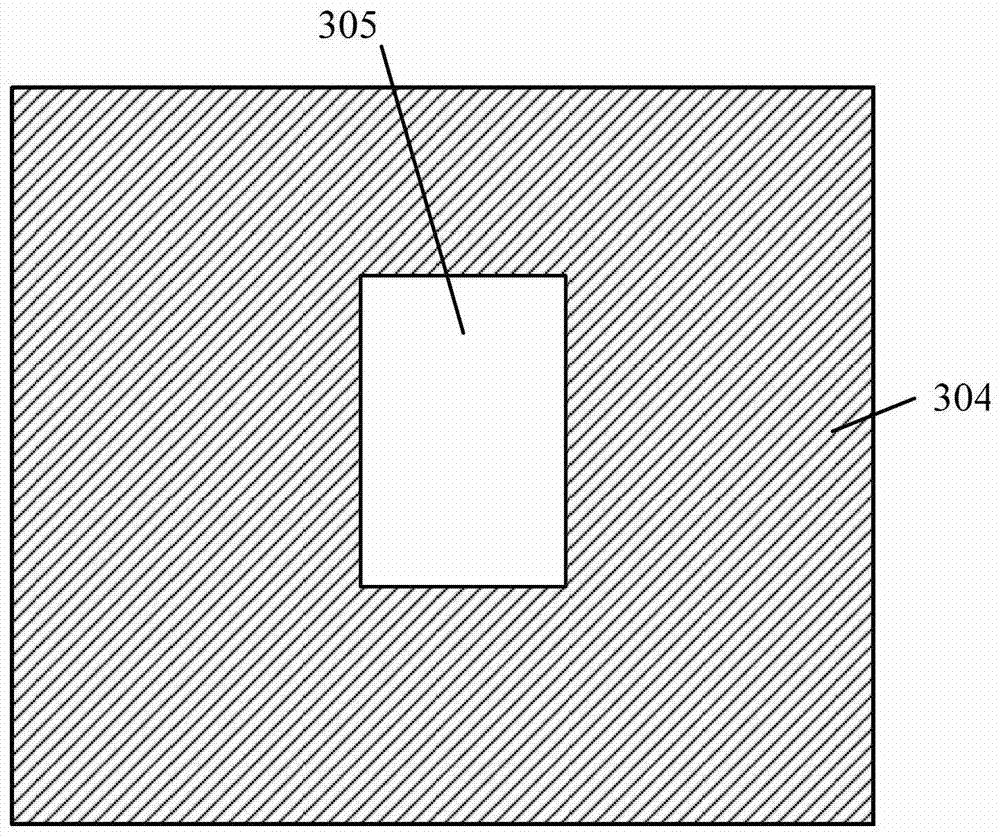

[0027] To this end, the inventor proposes a fin field effect transistor, the top silicon layer and the buried layer of the silicon-on-insulator substrate have a second opening and a third opening exposing the surface of the bottom silicon layer, and in the second opening and the third opening The epitaxial silicon layer is filled, the epitaxial silicon layer and the bottom silicon layer constitute the back gate, and the remaining part of the top silicon layer is used as a fin, and the fin surrounds the epitaxial silicon layer, and there is a first isolation layer and a buried gate between the fin and the back gate. Layer, due to the existence of the back gate, by applying a certain voltage on the back gate, when a certain voltage is applied on the back gate, the voltage applied on the back gate will affect the formation of the inve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More