Array substrate, manufacturing method of array substrate and display device

An array substrate and display area technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, instruments, etc., can solve the problems of waste of company interests, irreparability, and bad influence on the company's quality image, so as to improve the utilization rate Low, reduced risk of injury effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

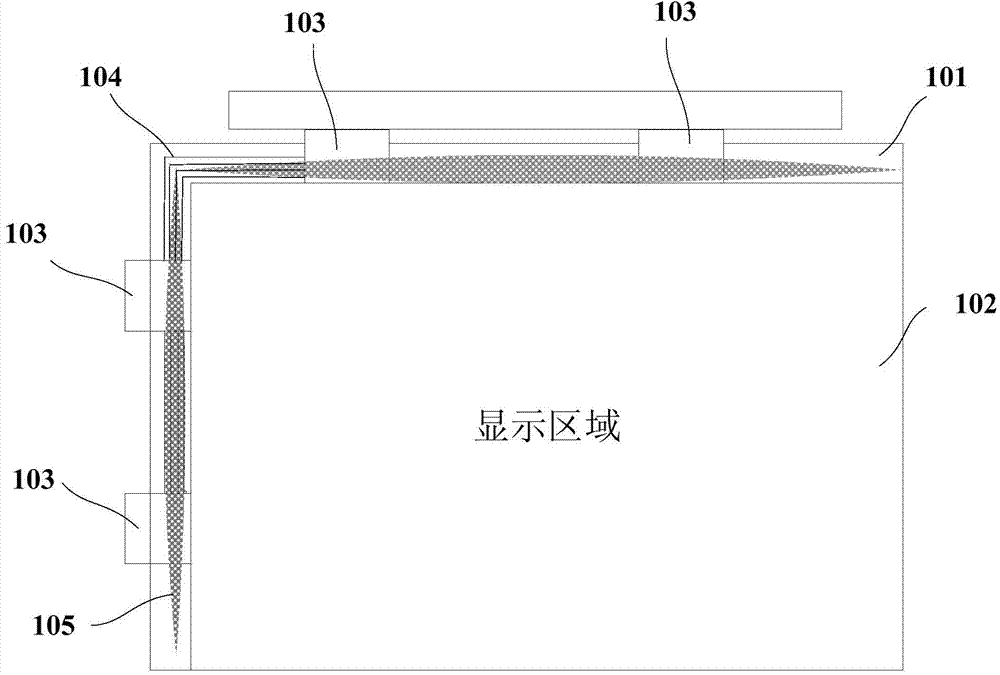

[0050] Please refer to Figure 4 , Figure 4 It is a schematic diagram of the arrangement structure of the signal connection line in Embodiment 1 of the present invention.

[0051]In this embodiment, the signal connection line includes a first connection line (not shown in the figure) and a second connection line 201, wherein the second connection line 201 is divided into two layers, and an insulating layer is arranged between the two layers of the second connection line 201 202. The area of the array substrate occupied by the second connecting wires 201 on the upper layer is A1, the area of the array substrate occupied by the second connecting wires 201 on the lower layer is A2, and the area A1 and the area A2 have an overlapping area A3.

[0052] Due to the overlapping area A3, when the number, width, and spacing of the second connecting lines are the same, the width of the non-display area of the array substrate occupied by the second connecting lines distributed on ...

Embodiment 2

[0054] Please refer to Figure 5 , Figure 5 It is a schematic diagram of the arrangement structure of the signal connection line in Embodiment 2 of the present invention.

[0055] In this embodiment, the signal connection line includes a first connection line (not shown in the figure) and a second connection line 201, wherein the second connection line 201 is divided into two layers, and an insulating layer is arranged between the two layers of the second connection line 201 202, the area of the array substrate occupied by the second connecting wires 201 on the upper layer is A1, the area of the array substrate occupied by the second connecting wires 201 on the lower layer is A2, and the area A1 and the area A2 have an overlapping area A4.

[0056] Due to the overlapping area A4, when the number, width, and spacing of the second connecting lines are the same, the width of the non-display area of the array substrate occupied by the second connecting lines distributed on...

Embodiment 3

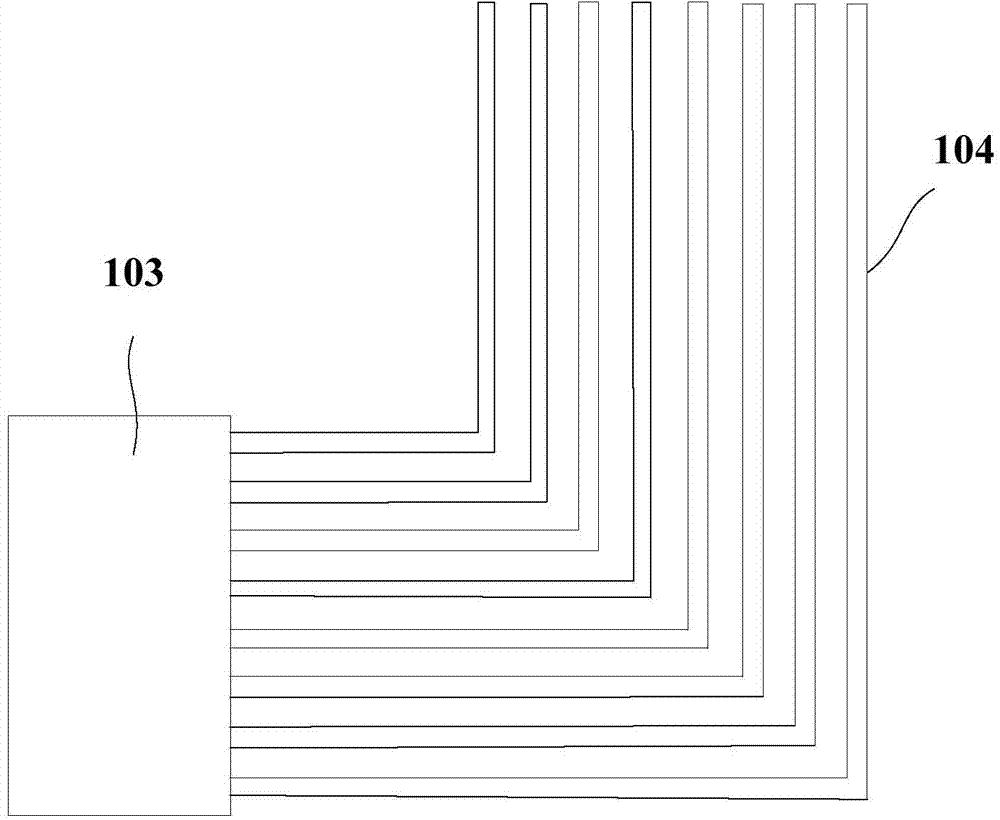

[0058] Please refer to Image 6 , Image 6 It is a schematic diagram of the arrangement structure of the signal connection line according to the third embodiment of the present invention.

[0059] In this embodiment, the signal connection line includes a first connection line (not shown in the figure) and a second connection line 201, wherein the second connection line 201 is divided into two layers, and an insulating layer is provided between the two layers of the second connection line 201 Layer 202, the area of the array substrate occupied by the second connecting wire 201 located on the upper layer is A1, the area of the array substrate occupied by the second connecting wire 201 located on the lower layer is A2, the area A1 and the area A2 completely overlap, and the upper and lower sides The second connection lines 201 of the layers are overlapped.

[0060] Due to the completely overlapping area, when the number, width, and spacing of the second connecting lines are...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More