Video decoder of dual-buffer-memory structure and control method

A video decoder and memory technology, applied in the field of video decoding, can solve the problems of chip area expansion, memory inconsistency, and high manufacturing costs, and achieve the effect of improving memory access efficiency and reducing bandwidth requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

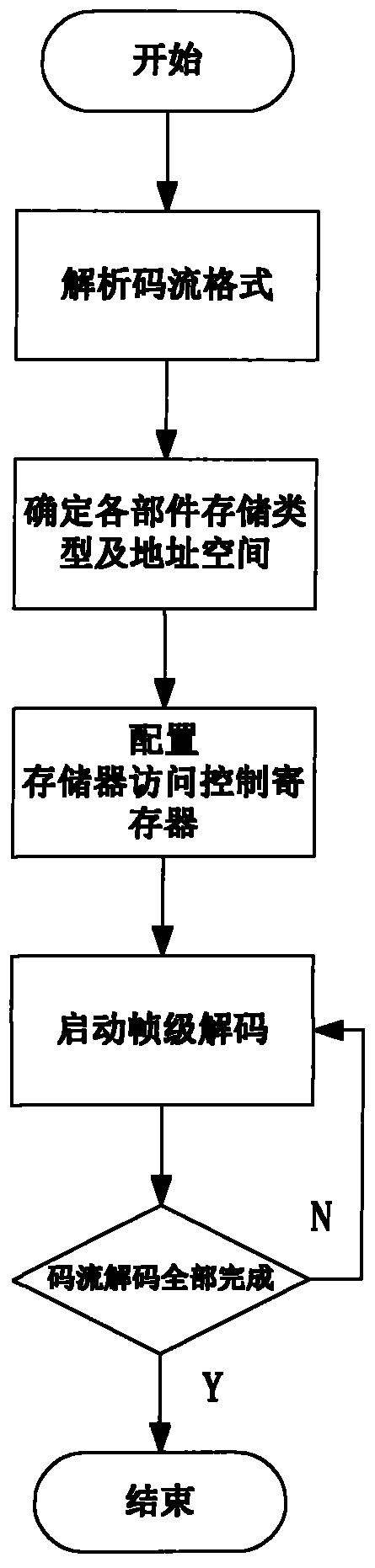

[0033] In order to describe the technical solution of the present invention more clearly, the present invention will be described in detail below in conjunction with the drawings and specific embodiments.

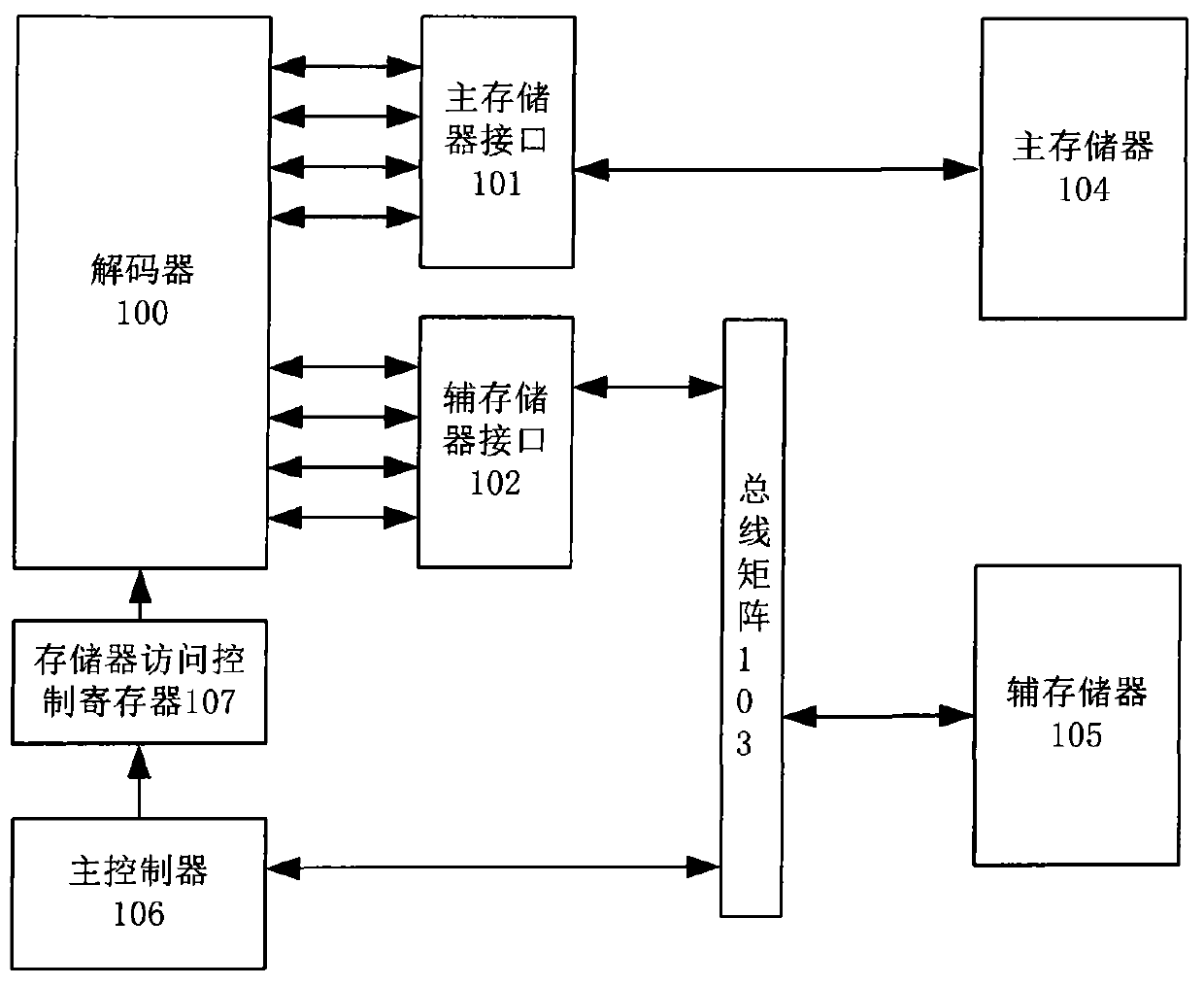

[0034] like figure 2 As shown, the video decoder of the present invention is connected with the main controller of the system. The video decoder includes memory access control registers, main memory interface, auxiliary storage interface, bus matrix, main memory, auxiliary memory and decoder. The memory access control register is connected with the main controller and the decoder, and the main controller configures the hardware function module of the decoder through the memory access control register whether to use the auxiliary memory to save intermediate data and the corresponding memory access address space. The decoder is connected with the memory access control register, the main memory interface, and the auxiliary memory interface. After receiving the decoding start...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More