Data transmission method and device and direct memory access

A data transmission method and memory technology, applied in the field of direct memory access, data transmission method, and device, can solve the problem of low resource utilization and achieve the effect of improving data transmission efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

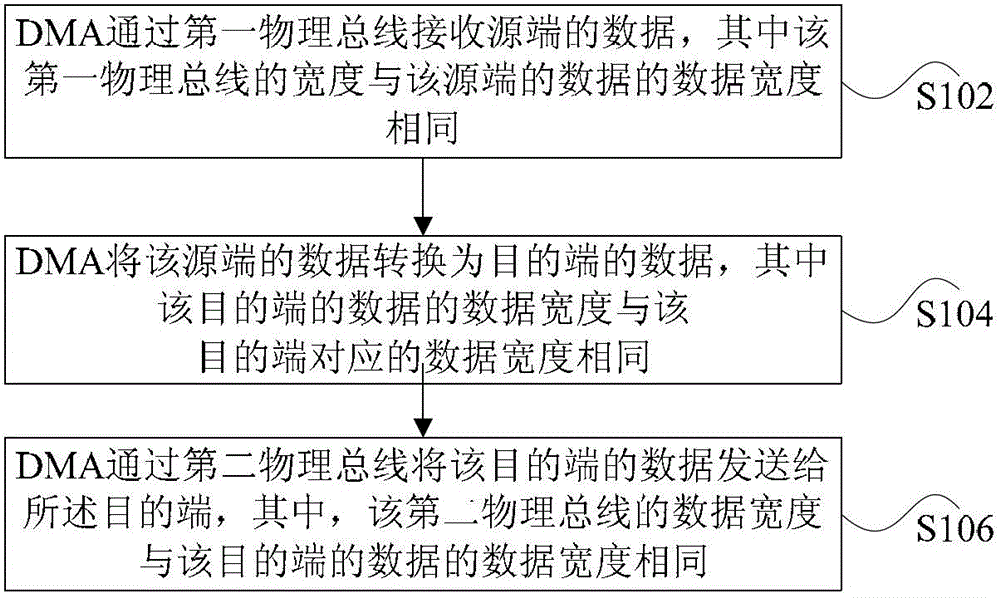

[0068] This preferred embodiment provides an improved DMA method for data transmission. According to the characteristics of time separation of different transmission modes, only one transmission channel is used to realize different transmission functions; the DMA physical bus width is designed to be consistent with the data width (for example: the data width between DMA and SM is 64bit, DMA and PM The data width between DMA and DM is 128bit, and the data width between DMA and DM is 256bit), and multi-band FIFO is used to buffer the inconsistency of the source and destination bus widths.

[0069] In this embodiment, the functions executable by the DMA include: command data transfer from SM to PM, data transfer from SM to DM, and data transfer from DM to SM. This DMA can be configured and accessed by the ARM or DSP core.

[0070] Preferably, DMA includes the following:

[0071] (1) Eight 32-bit wide bidirectional synchronous FIFOs are used to buffer the inconsistency of the da...

Embodiment 2

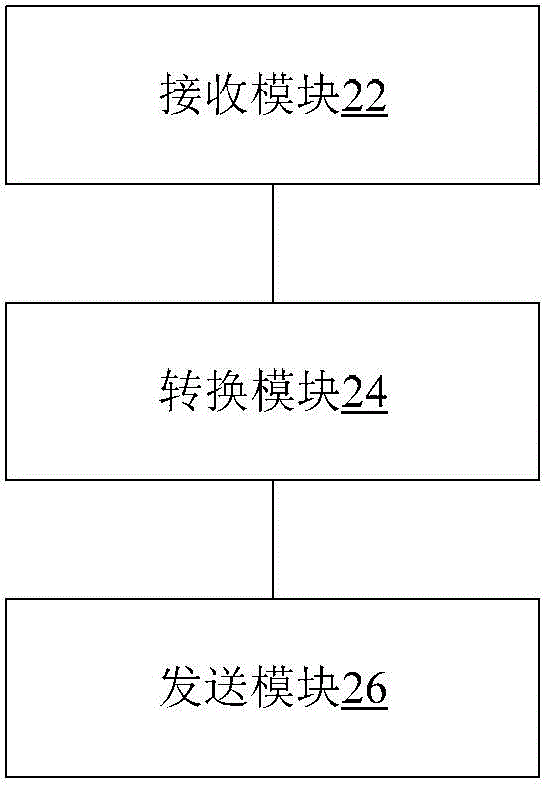

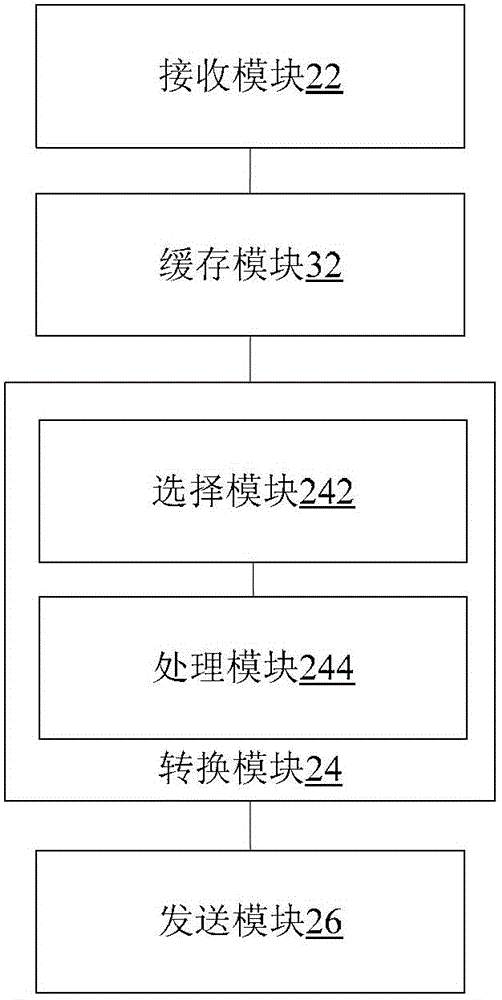

[0083] This preferred embodiment provides a DMA, such as Figure 5 The DMA is shown, and the composition of the DMA is described in detail in this embodiment.

[0084] In order to achieve DM non-aligned address data access, DMAFIFO is divided into 8 groups (bank), each group (bank) is 32bit wide. Figure 6 is a schematic diagram of the realization of a 5×32-bit bidirectional FIFO according to an embodiment of the present invention, such as Figure 6Implementation of each 32bit FIFO shown. The FIFO depth is 5, which is slightly larger than a burst-16 data volume (when the depth is 4, the DMAFIFO size is 32×4×8bit=64×16bit=1024bit). The FIFO can realize two-way transmission, and five 32-bit registers are multiplexed during two-way transmission. The transmission direction is controlled by the dir signal, mem distinguishes between PM and DM, and the dir and mem signals jointly determine the transmission mode (SM2PM, SM2DM, DM2SM). The "_d" suffix in the figure indicates the do...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com