Array substrate, manufacturing method thereof and display device

A technology of an array substrate and a manufacturing method, which is applied in the field of liquid crystal display, can solve the problems affecting the light efficiency of the display panel, the display effect of the display panel, and the transmittance of the display panel, etc., so as to achieve the effect of improving the display quality and eliminating the phenomenon of dark areas.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

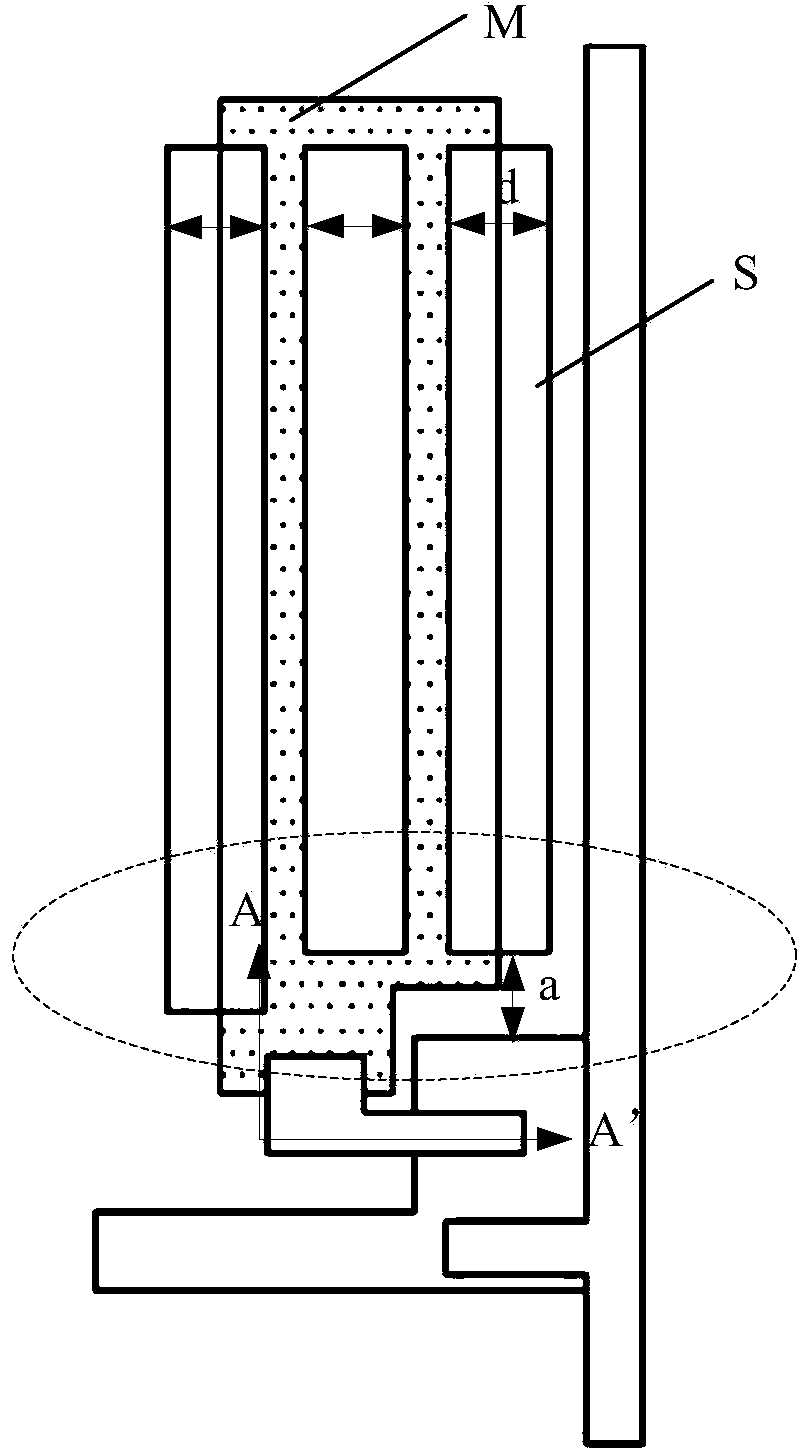

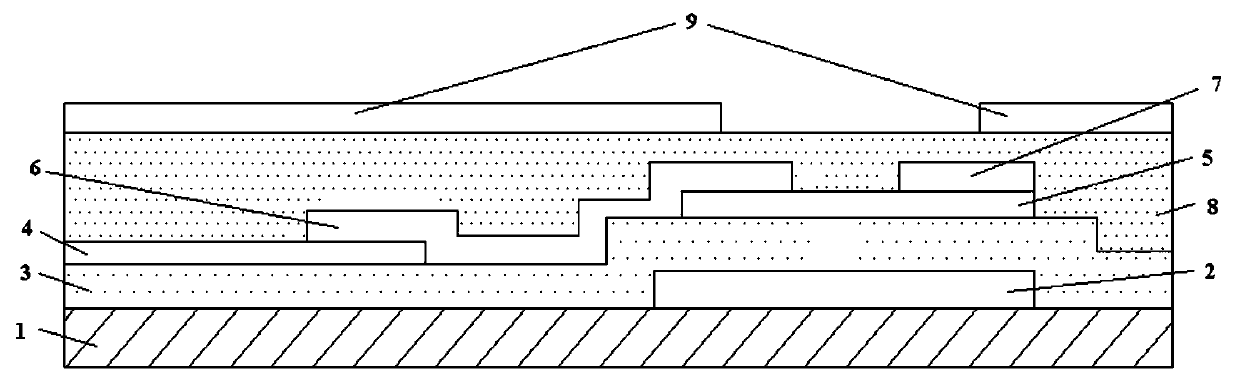

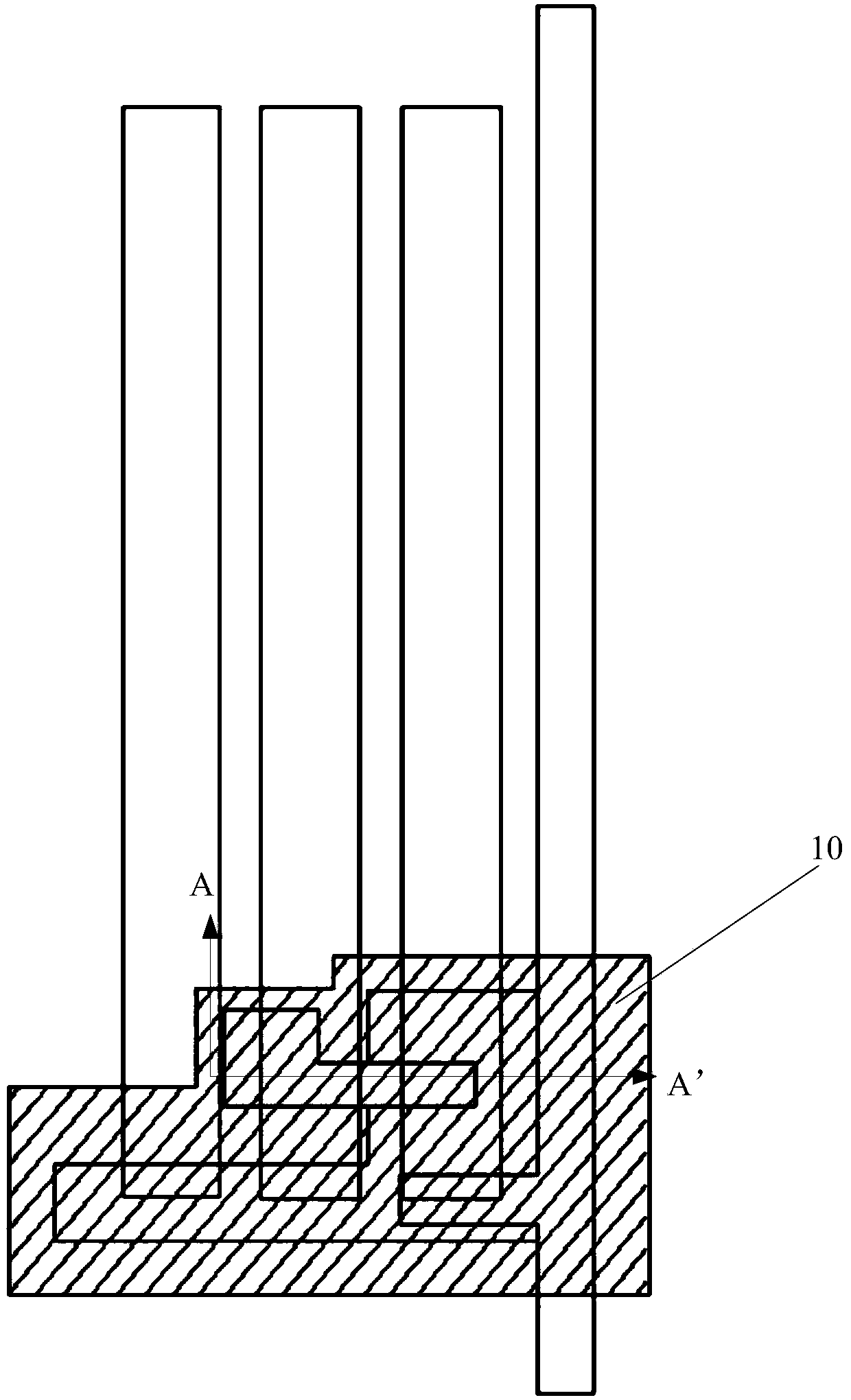

[0066] In this embodiment, a conductive pattern is formed above the gate electrode, so that the projection of the gate electrode in a direction perpendicular to the base substrate falls into the conductive pattern. Specifically, the manufacturing method of the array substrate of this embodiment includes the following steps:

[0067] In step a1: provide a base substrate 1, and form patterns of gate electrodes 2 and gate lines on the base substrate 1;

[0068] A base substrate 1 is provided, on which a pattern consisting of a gate metal layer including a gate electrode 2 and a gate line connected to the gate electrode 2 is formed. Wherein, the base substrate 1 may be a glass substrate or a quartz substrate.

[0069] Specifically, sputtering or thermal evaporation can be used to deposit a layer with a thickness of The gate metal layer, the gate metal layer can be Cu, Al, Ag, Mo, Cr, Nd, Ni, Mn, Ti, Ta, W and other metals and alloys of these metals, the gate metal layer can be s...

Embodiment 2

[0090] In this embodiment, a conductive pattern is formed above the gate electrode, so that the projection of the gate electrode in a direction perpendicular to the substrate falls into the conductive pattern, and the conductive pattern is connected to the source electrode or the drain electrode through a via hole. Specifically, the manufacturing method of the array substrate of this embodiment includes the following steps:

[0091] In step b1: provide a base substrate 1, and form patterns of gate electrodes 2 and gate lines on the base substrate 1;

[0092] A base substrate 1 is provided, on which a pattern consisting of a gate metal layer including a gate electrode 2 and a gate line connected to the gate electrode 2 is formed. Wherein, the base substrate 1 may be a glass substrate or a quartz substrate.

[0093] Specifically, sputtering or thermal evaporation can be used to deposit a layer with a thickness of The gate metal layer, the gate metal layer can be Cu, Al, Ag, M...

Embodiment 3

[0114] In this embodiment, a conductive pattern is formed above the gate electrode, so that the projection of the gate electrode in a direction perpendicular to the base substrate falls into the conductive pattern. Specifically, the manufacturing method of the array substrate of this embodiment includes the following steps:

[0115] In step c1: provide a base substrate 1, and form patterns of gate electrodes 2 and gate lines on the base substrate 1;

[0116] A base substrate 1 is provided, on which a pattern consisting of a gate metal layer including a gate electrode 2 and a gate line connected to the gate electrode 2 is formed. Wherein, the base substrate 1 may be a glass substrate or a quartz substrate.

[0117] Specifically, sputtering or thermal evaporation can be used to deposit a layer with a thickness of The gate metal layer, the gate metal layer can be Cu, Al, Ag, Mo, Cr, Nd, Ni, Mn, Ti, Ta, W and other metals and alloys of these metals, the gate metal layer can be s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More