Patents

Literature

1082results about How to "Reduce light leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Liquid crystal display with mirror mode having top reflective polarizer

InactiveUS7057681B2Improve seismic performanceQuality improvementPolarising elementsIlluminated signsLiquid-crystal displayDisplay device

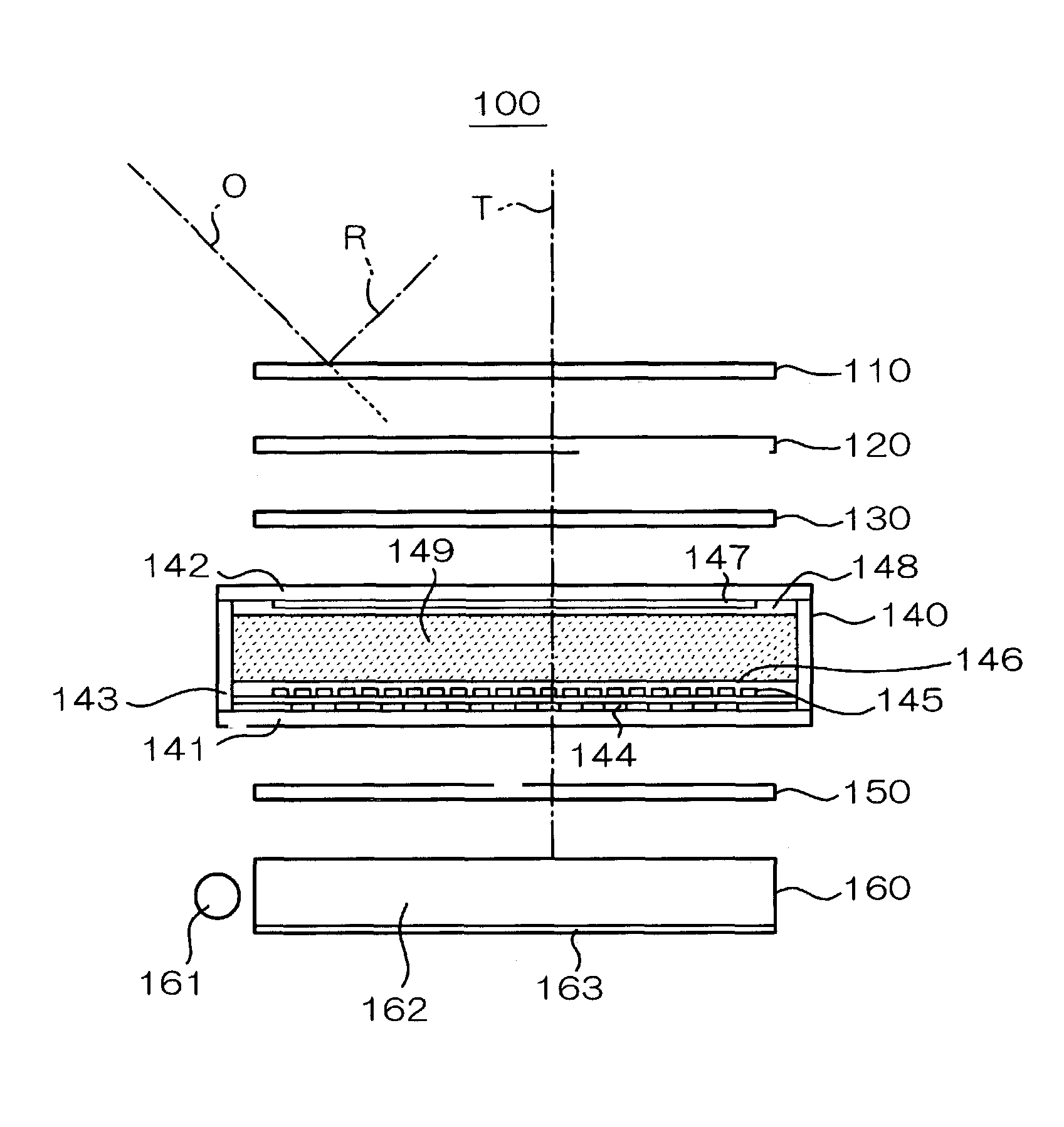

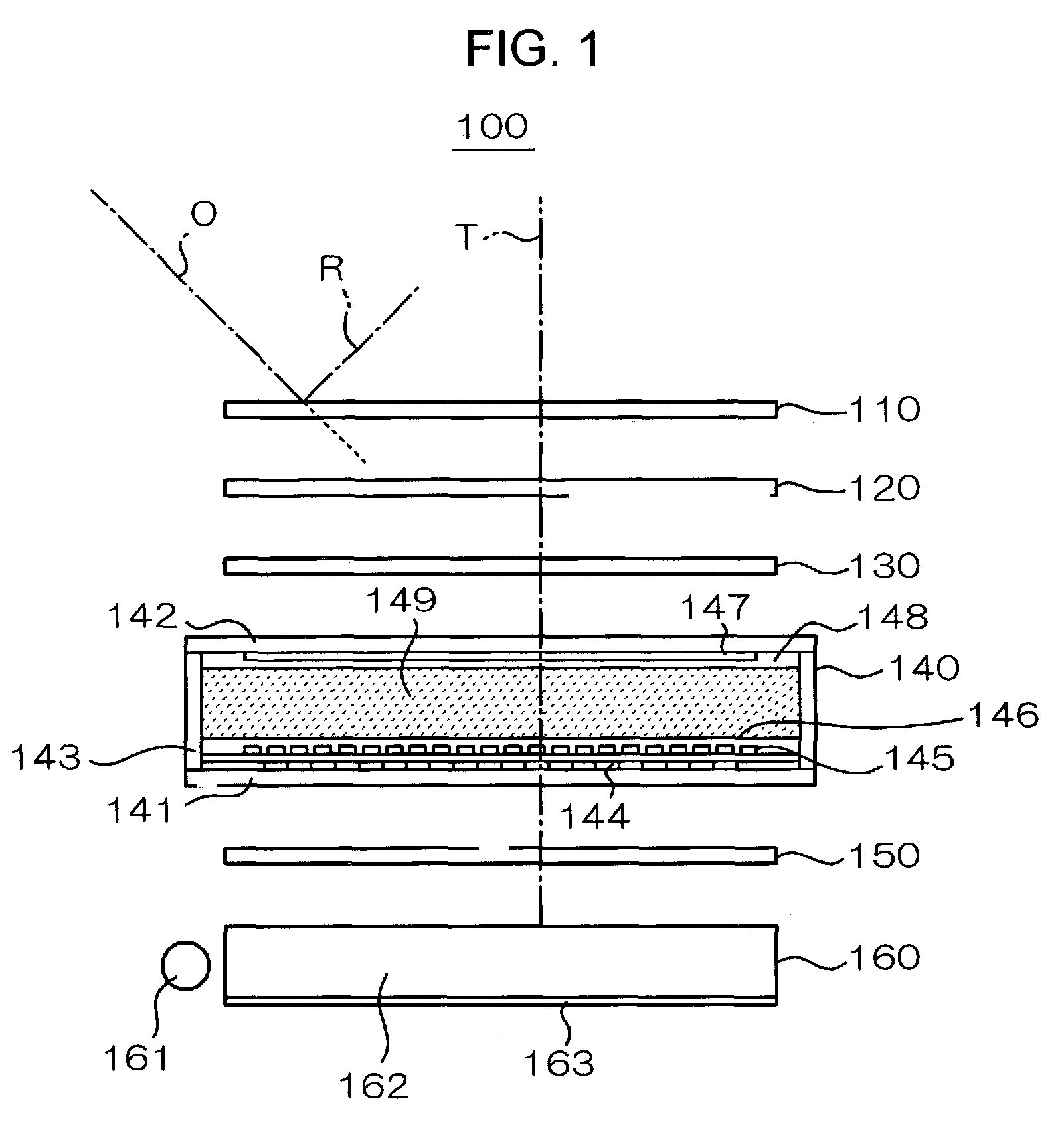

In a display device 100, a reflective polarizer 110, a polarizer 120, a retarder 130, a liquid crystal panel 140, a polarizer 150, and a backlight 160 are disposed sequentially from the viewing side. When the liquid crystal panel 140 is set in a light blocking state or the backlight 160 is set in an unlit state, the reflection of an outside light “O” turns the display screen into a mirror state. When the backlight 160 is set in a lit state to drive the liquid crystal panel 140, a transmitted light “T” allows a particular display screen to be visually recognized.

Owner:BOE TECH GRP CO LTD

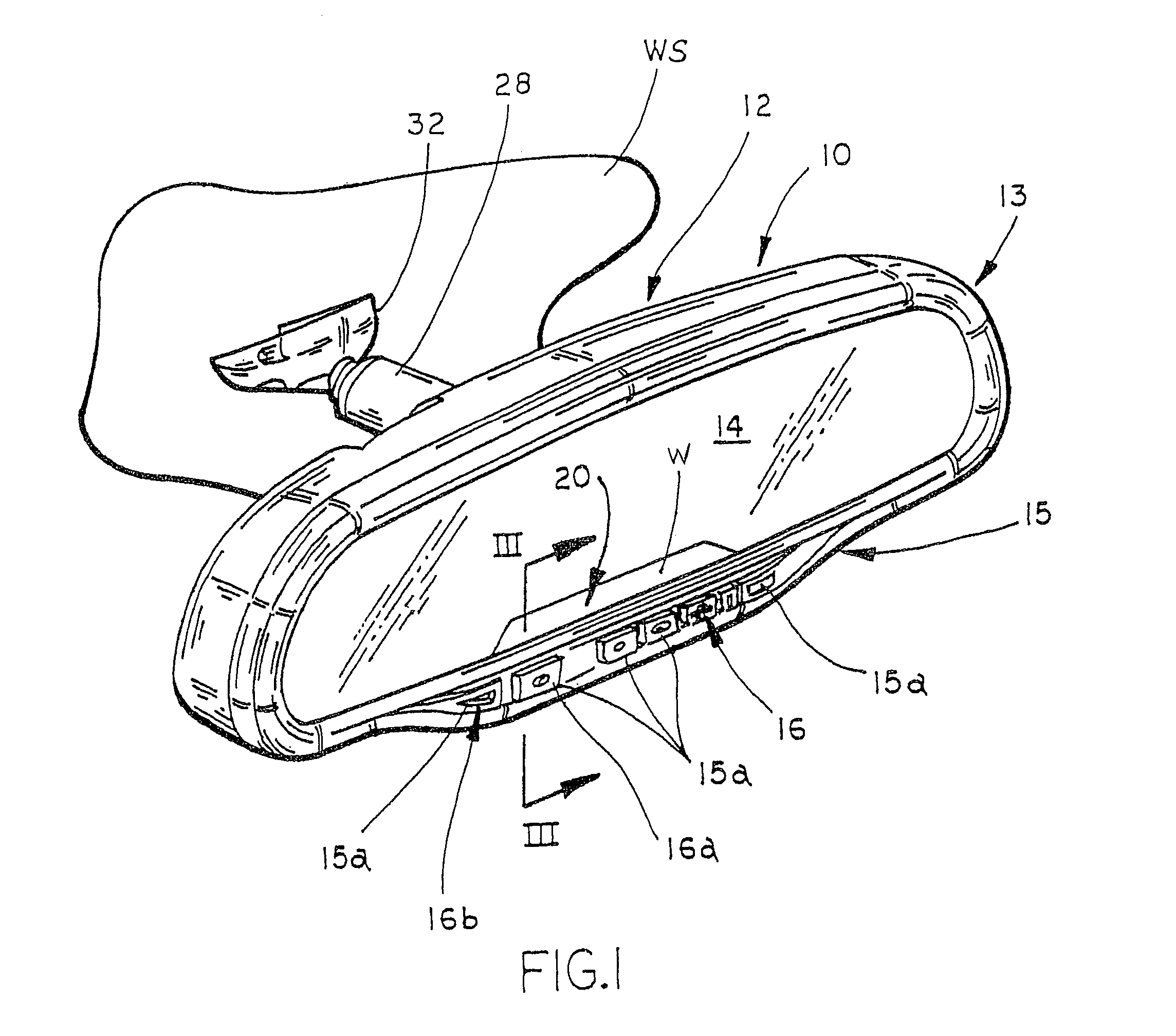

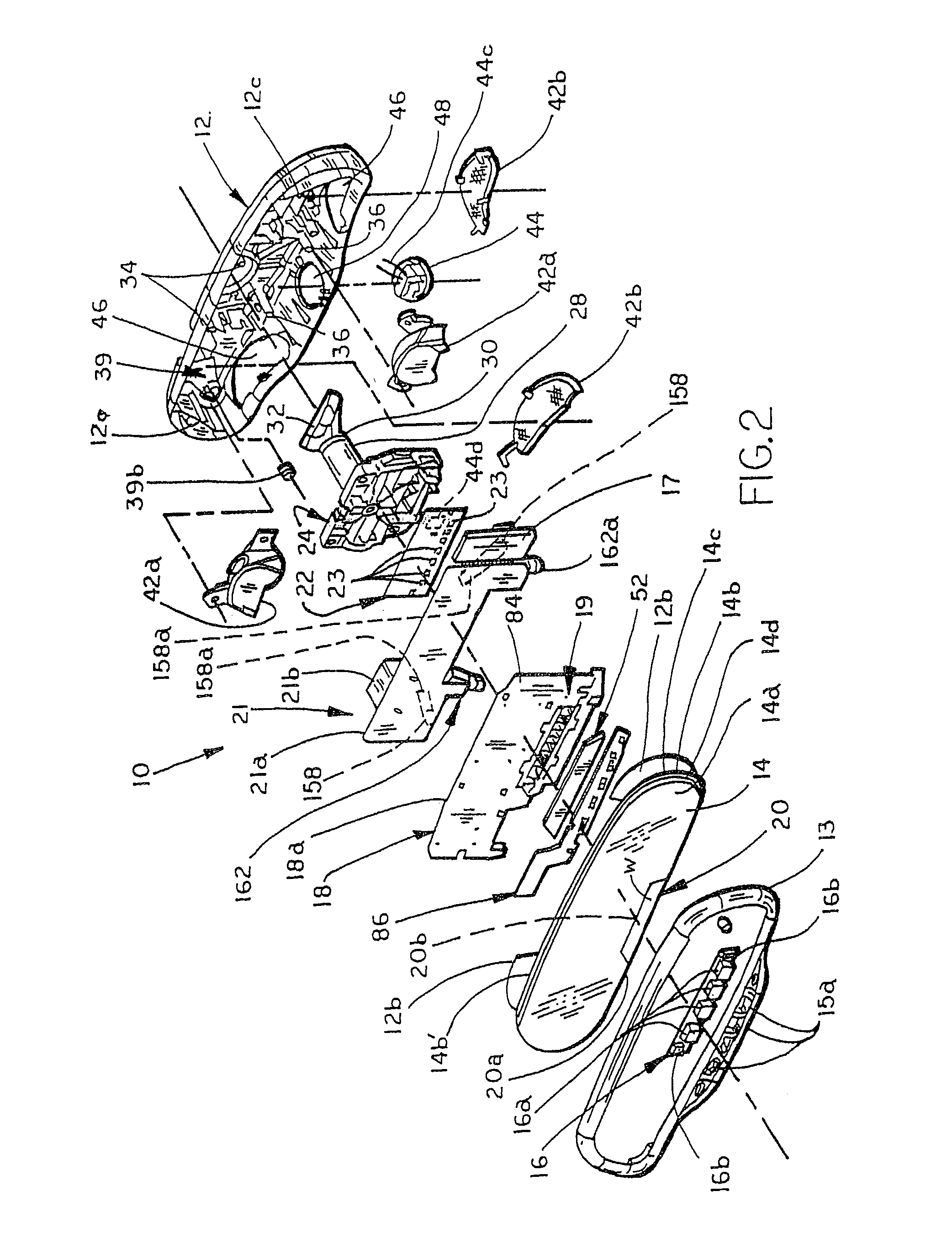

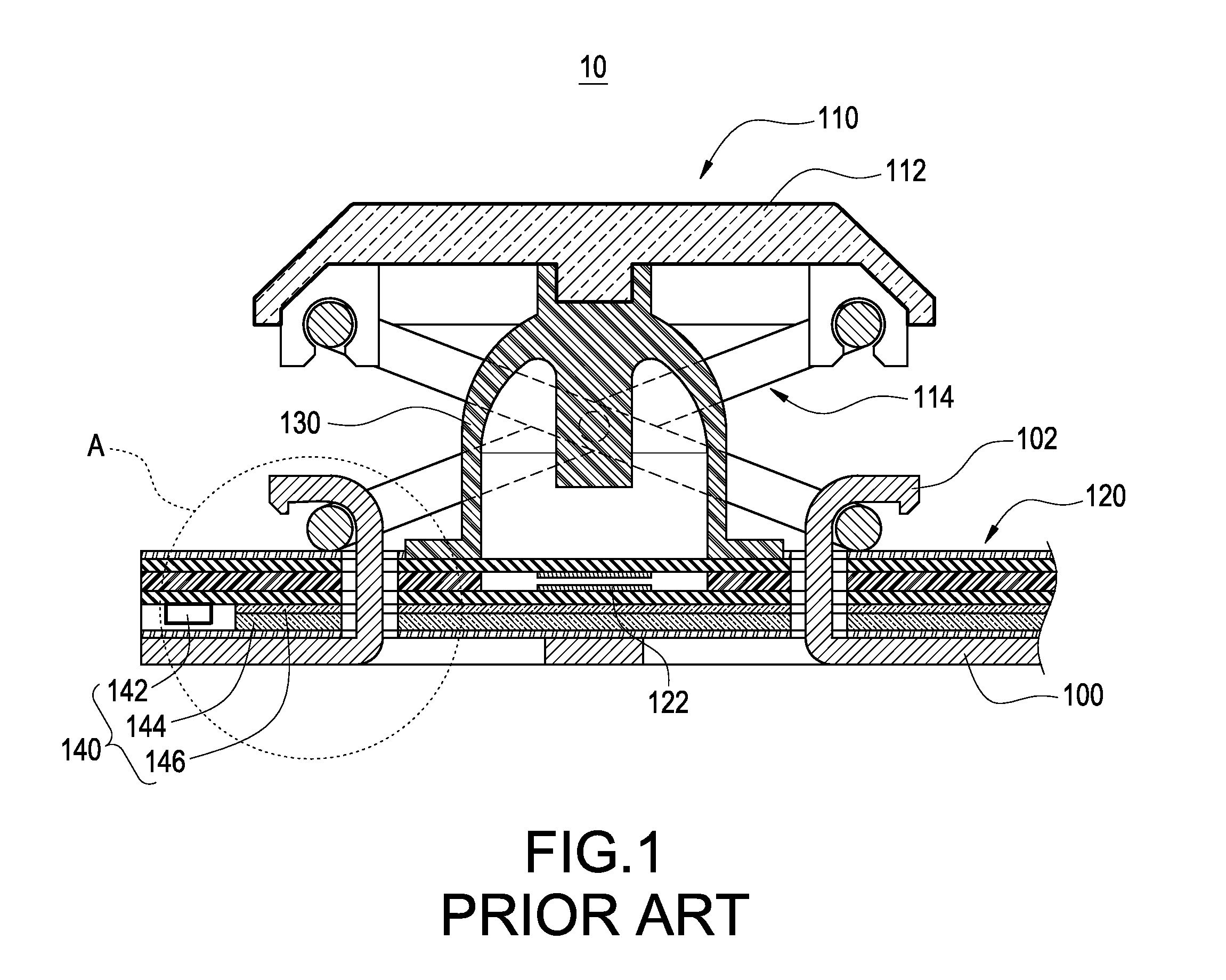

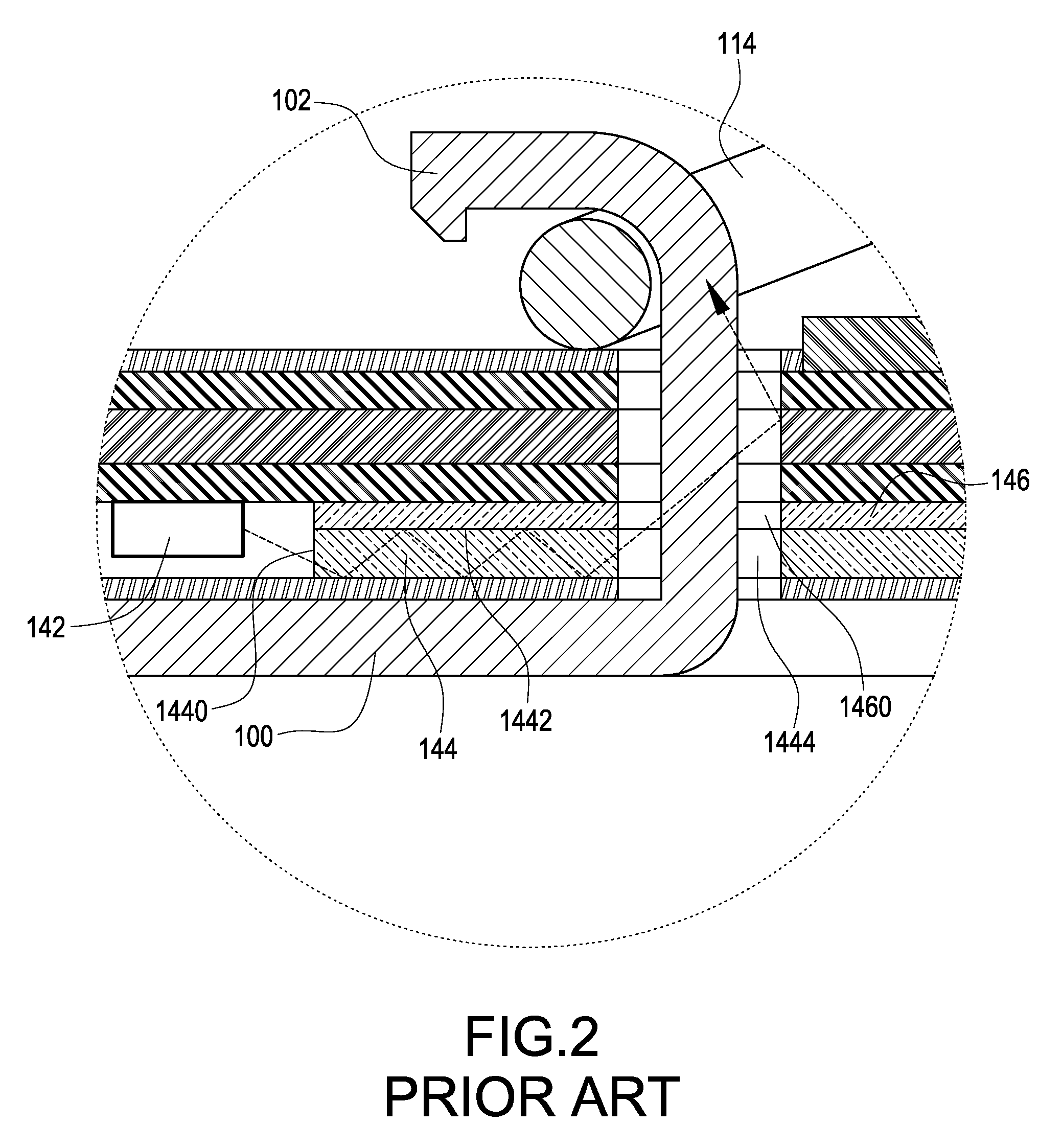

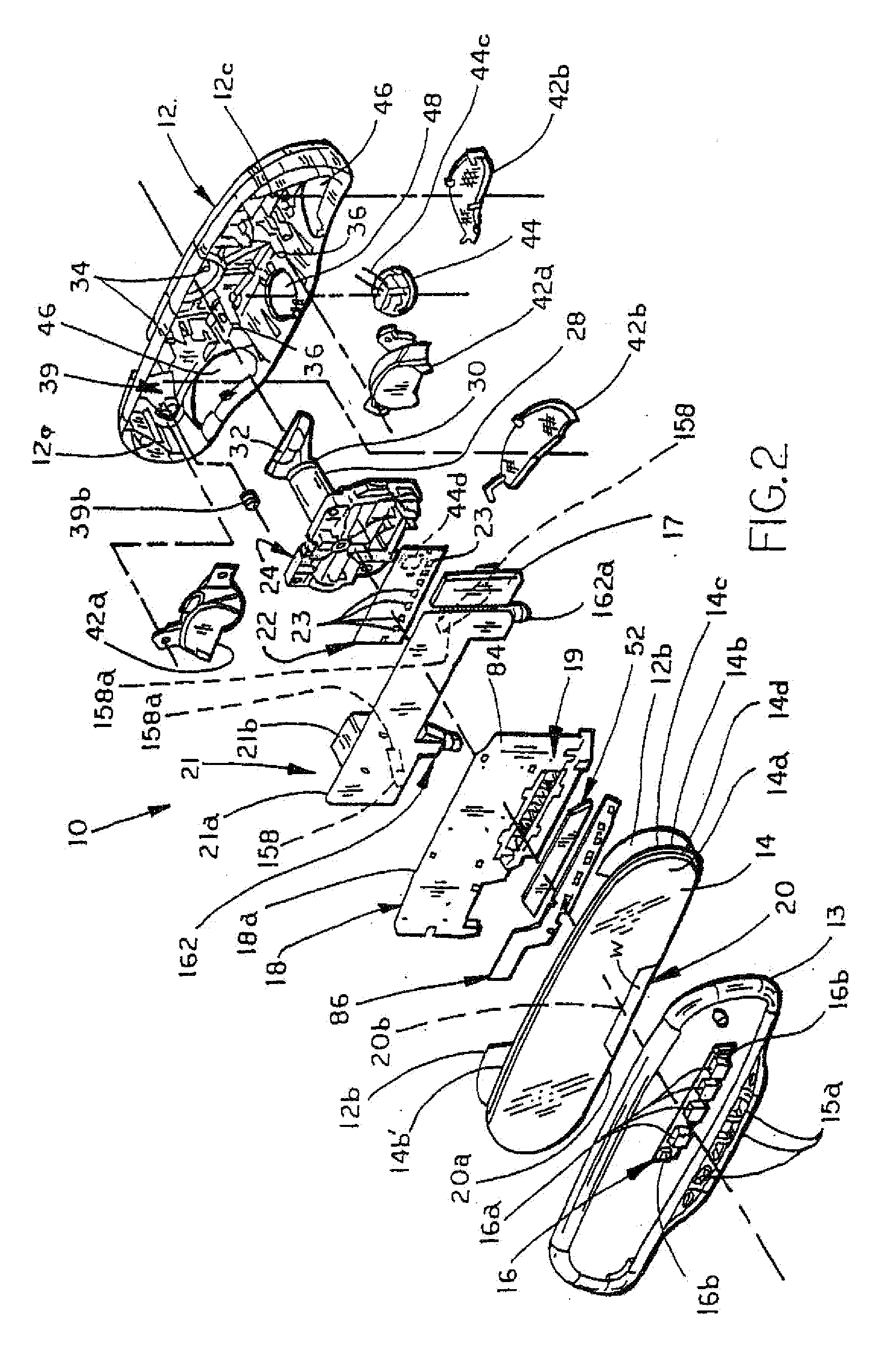

Information display system for a vehicle

InactiveUS7488080B2Easy to install and arrangeReduce light leakageMirrorsElectrical apparatusInformation display systemsLuminous intensity

An interior rearview mirror assembly suitable for use in a vehicle includes a variable reflectance reflective element, which includes an electrochromic medium, a first information display positioned to the rear of the variable reflectance reflective element, and a second information display. The mirror assembly further includes a single control for adjusting the luminous intensity of the first information display and the second information display and at least one light sensor, with the output of the control being generated responsive to a light level sensed by the at least one light sensor. In addition, the luminous intensity of the first information display and of the second information display increases responsive to the output of the control to compensate for any decrease in transmission of the electrochromic medium.

Owner:DONNELLY CORP

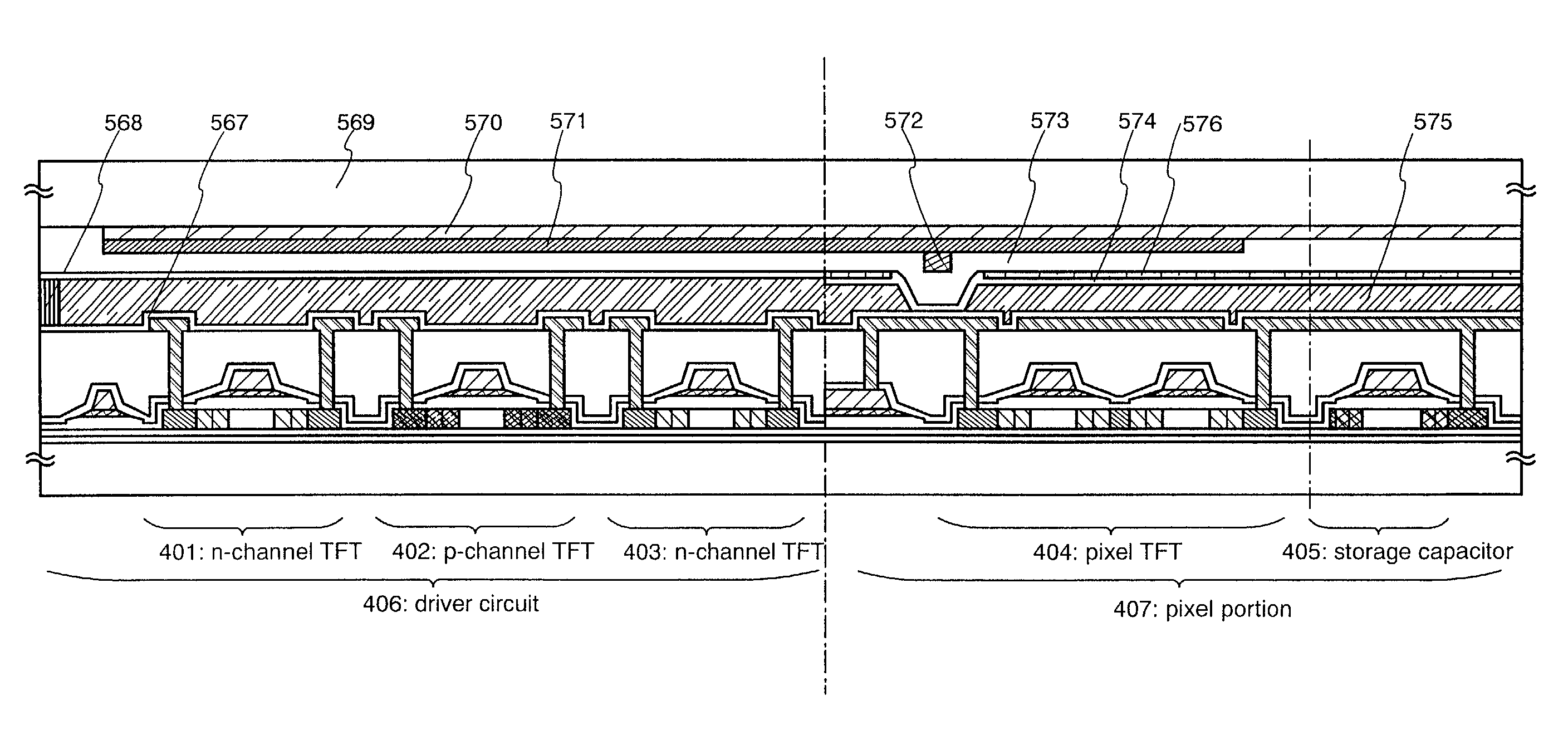

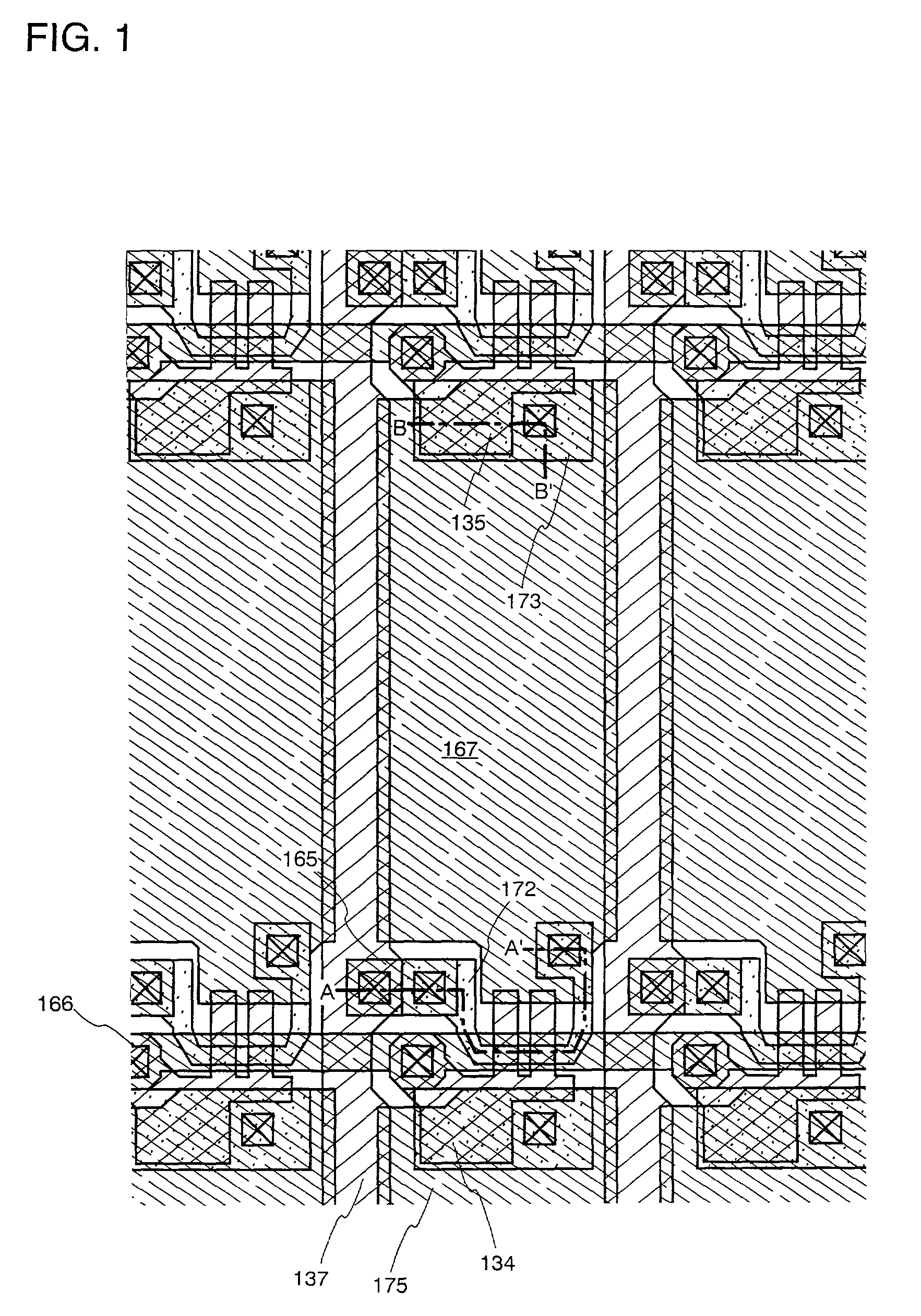

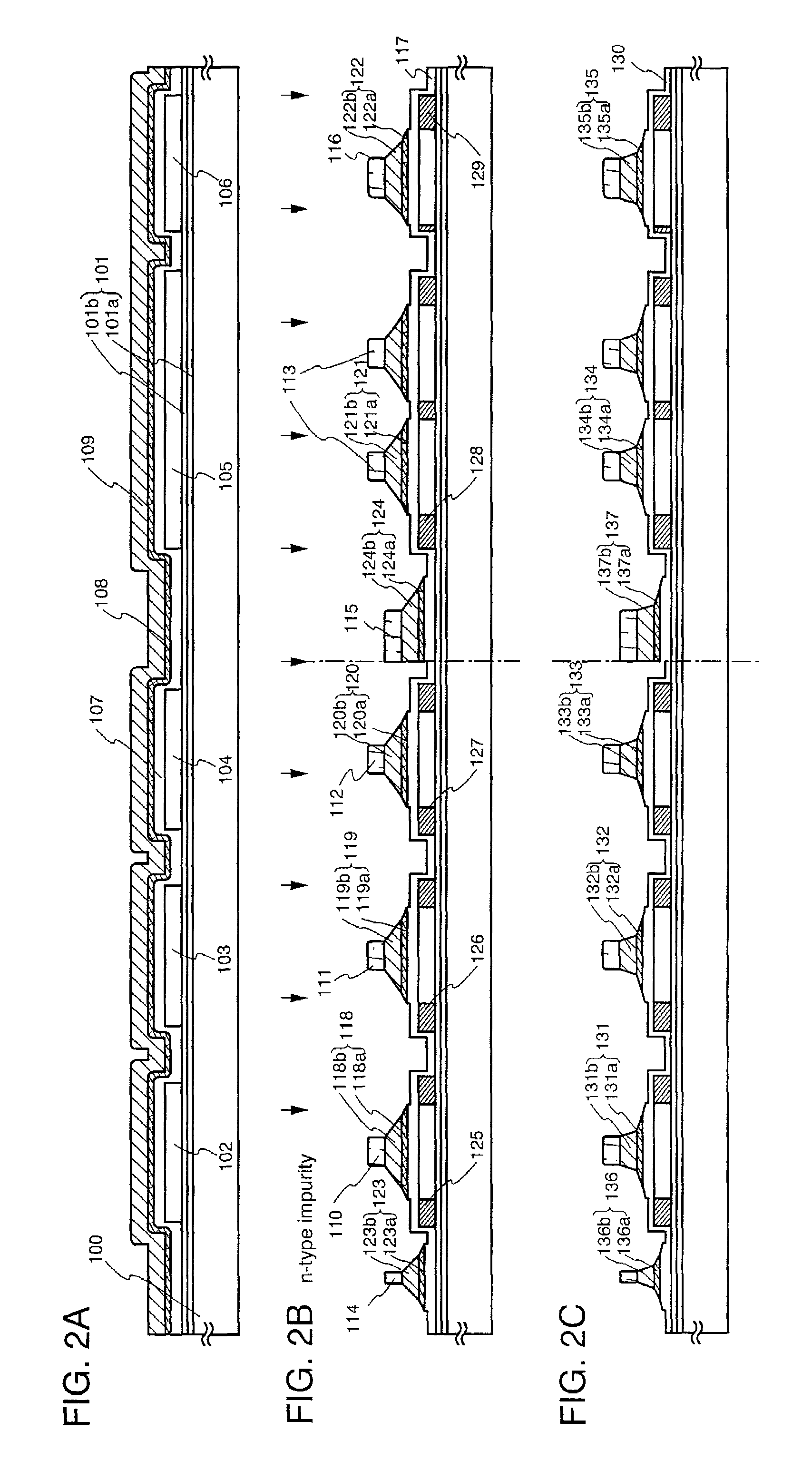

Semiconductor device and method of manufacturing the same

The present invention improves the aperture ratio of a pixel of a reflection-type display device or a reflection type display device without increasing the number of masks and without using a blackmask. A pixel electrode (167) is arranged so as to partially overlap a source wiring (137) for shielding the gap between pixels from light, and a thin film transistor is arranged so as to partially overlap a gate wiring (166) for shielding a channel region of the thin film transistor from light, thereby realizing a high pixel aperture ratio.

Owner:SEMICON ENERGY LAB CO LTD

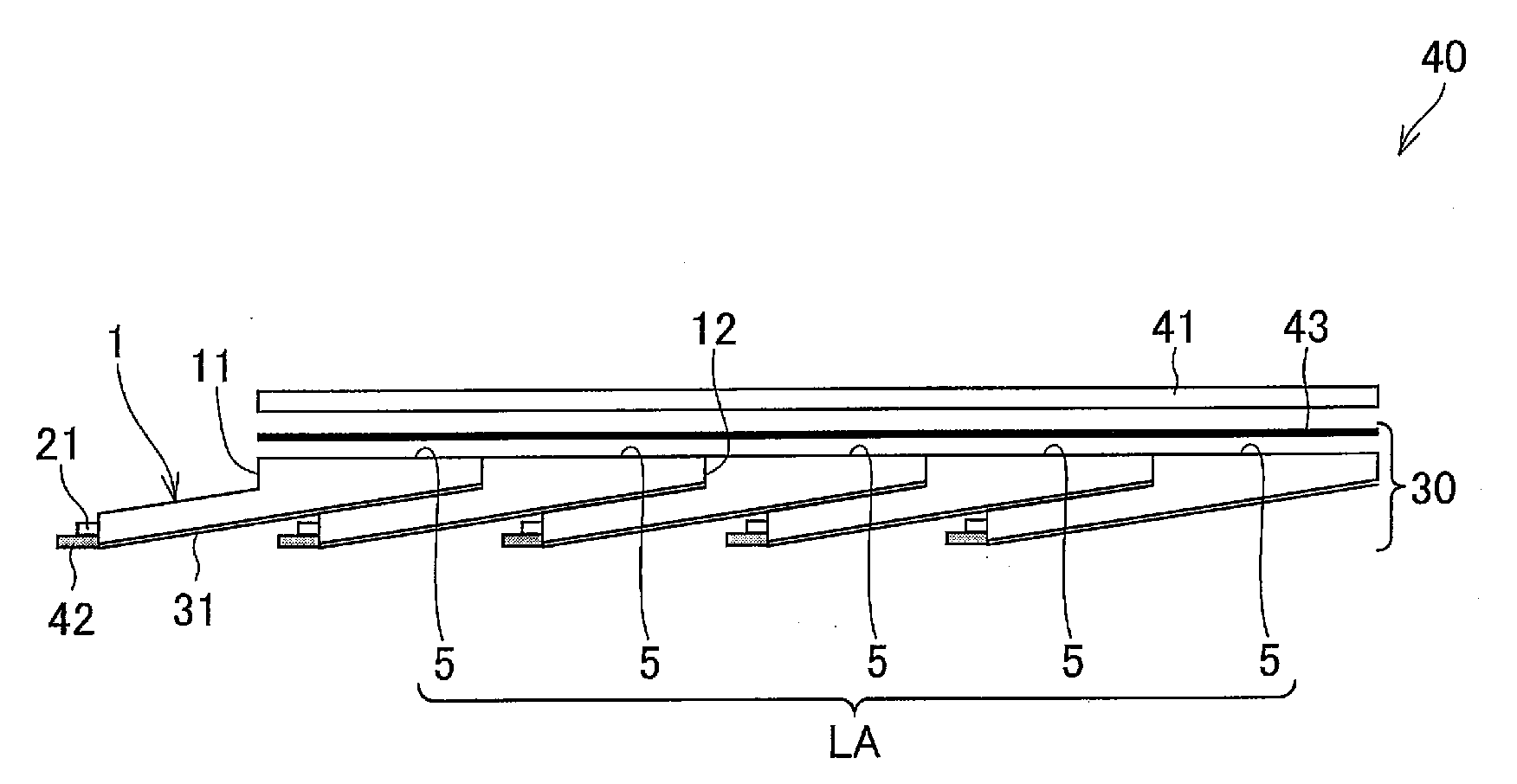

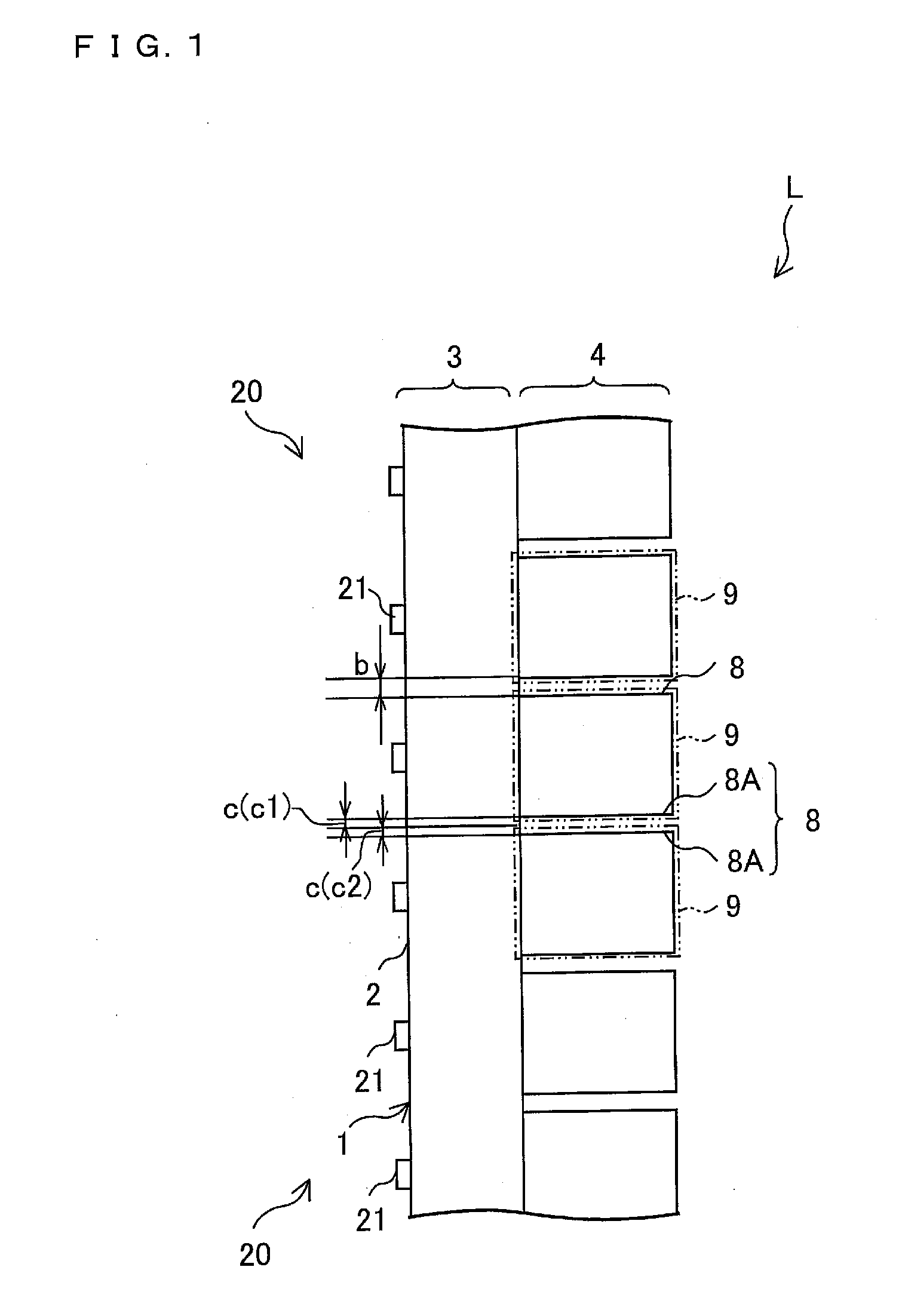

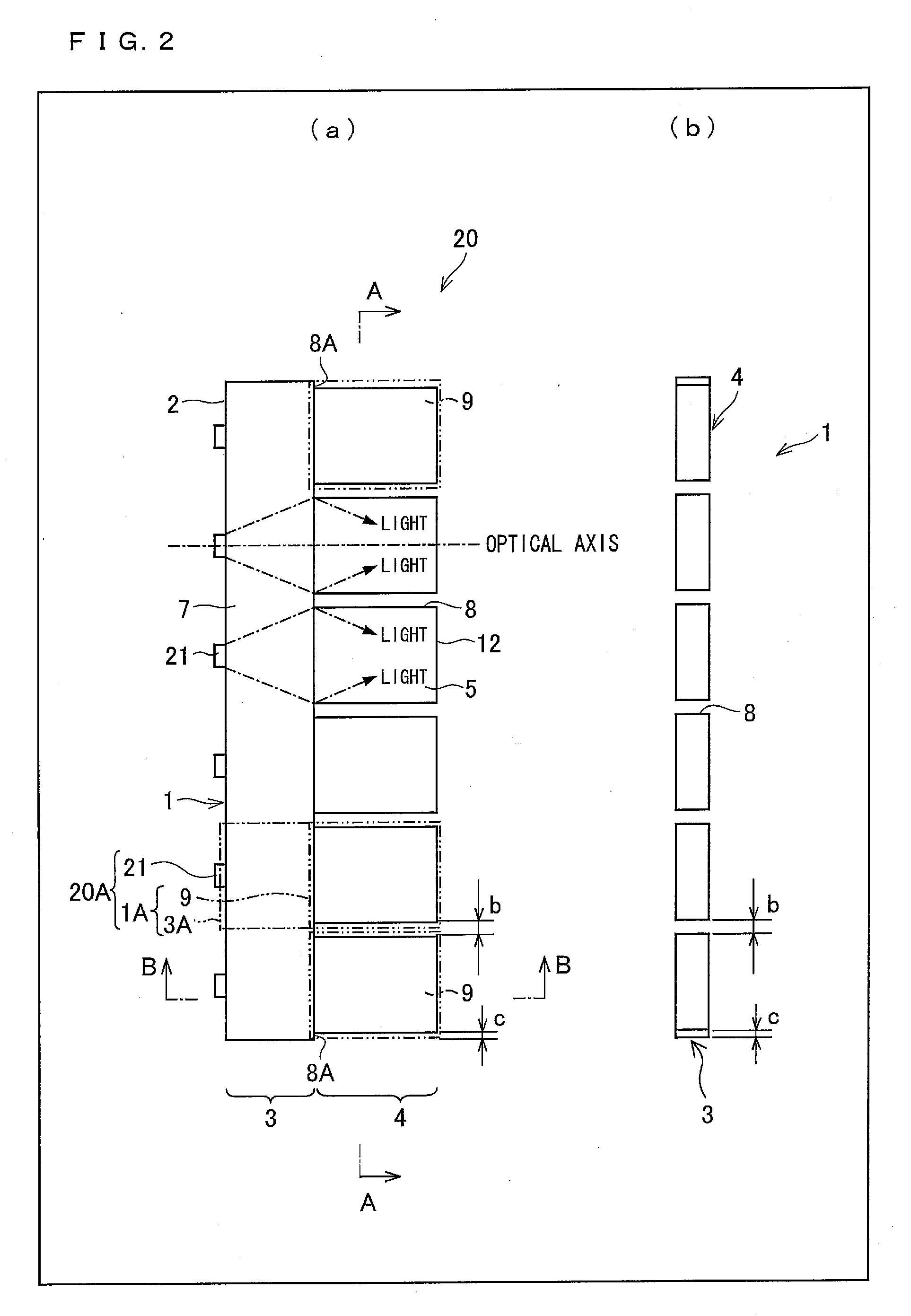

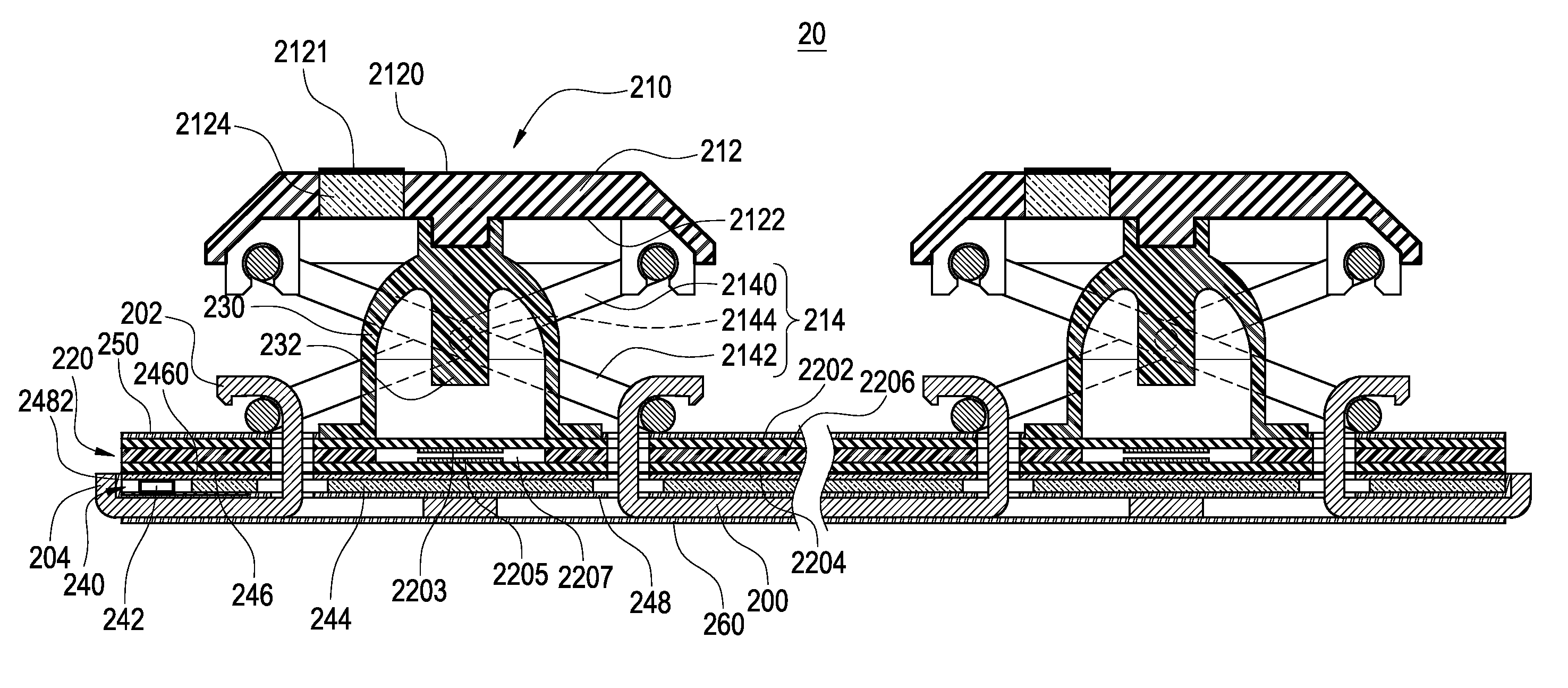

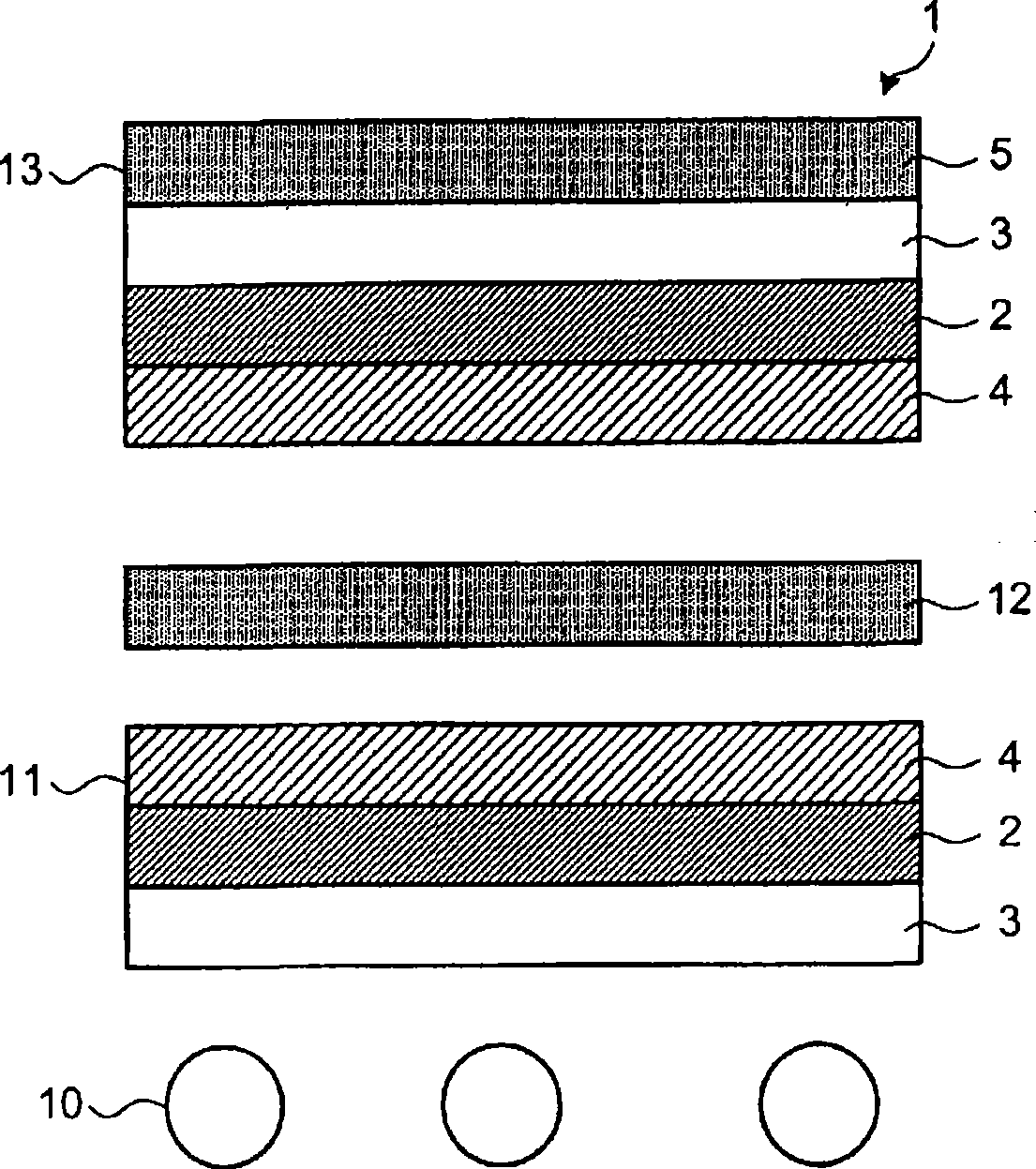

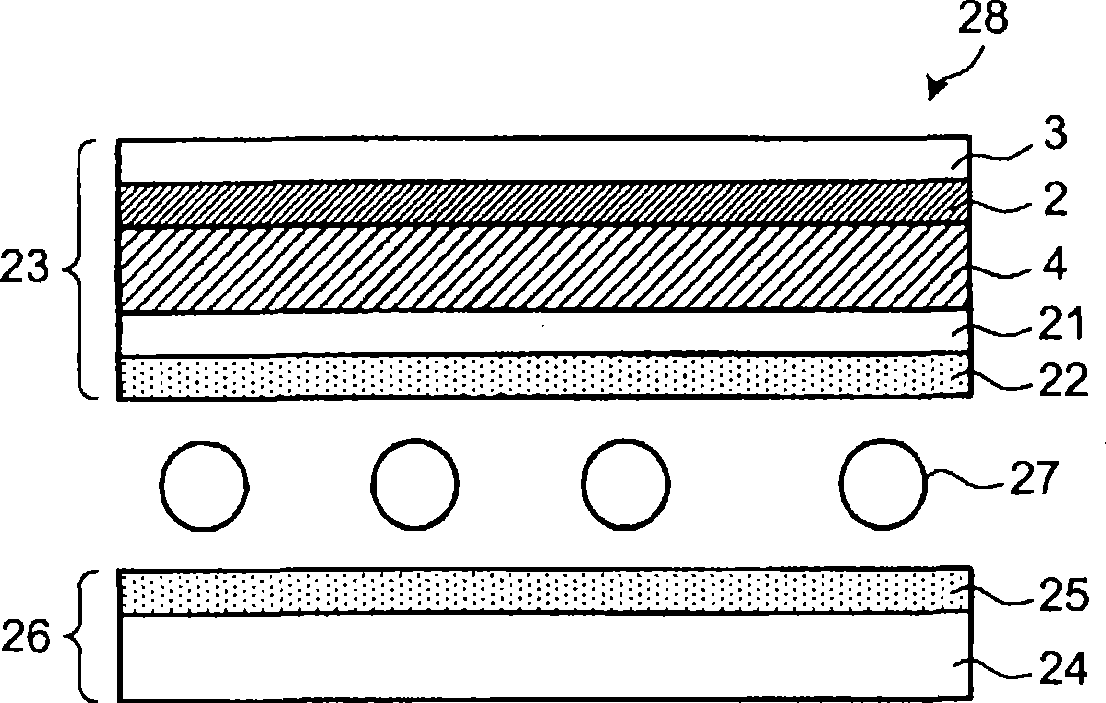

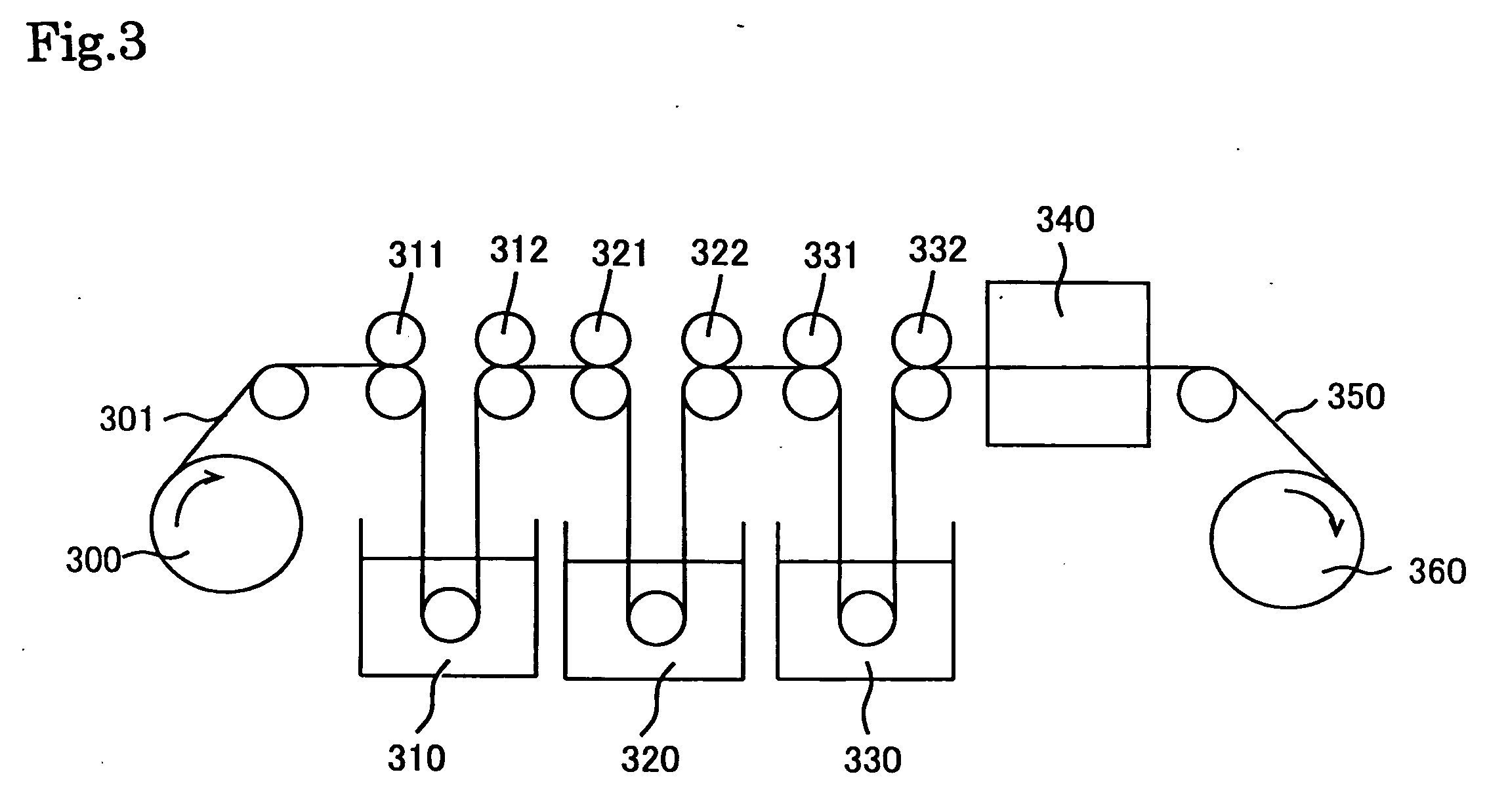

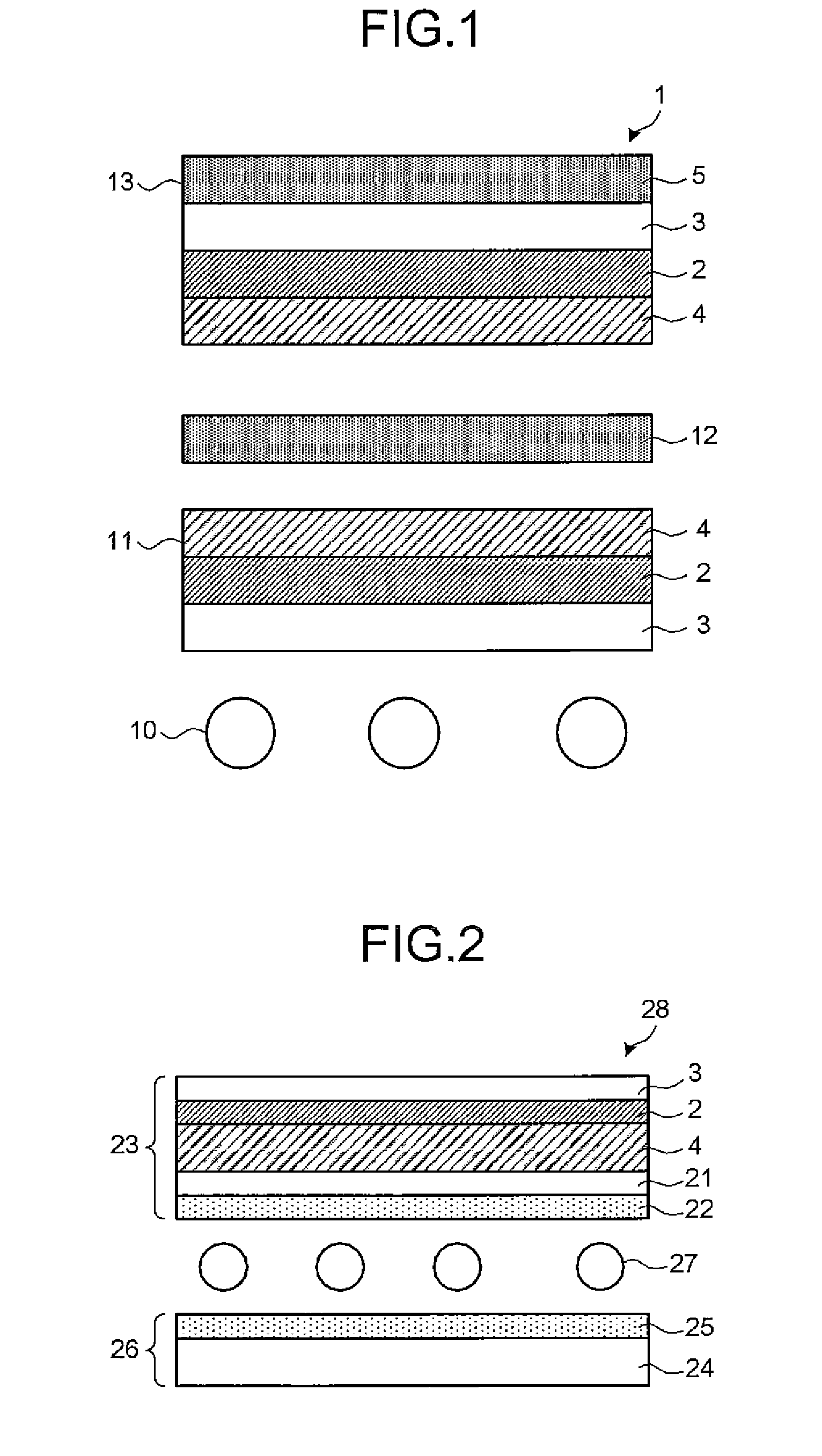

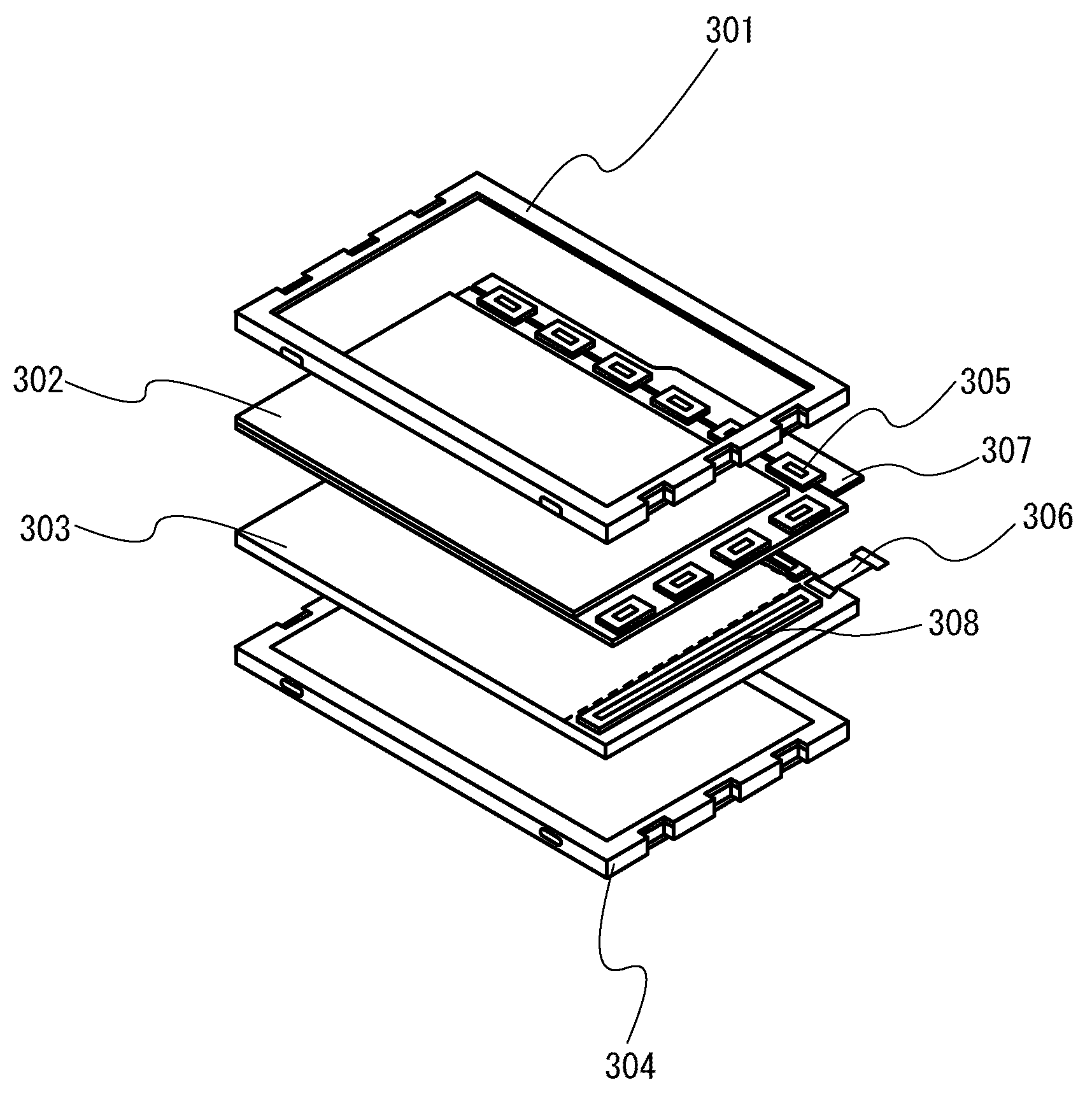

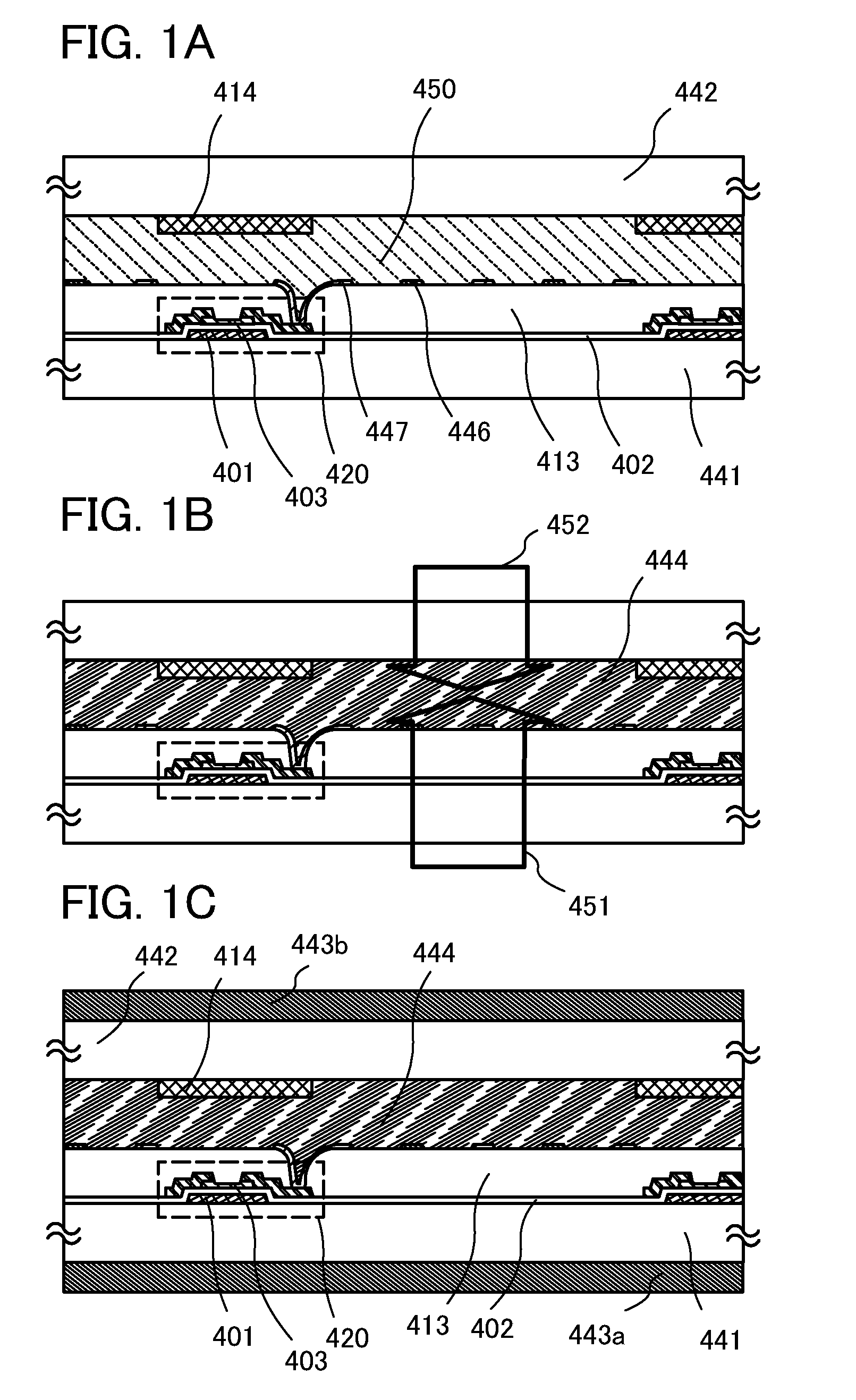

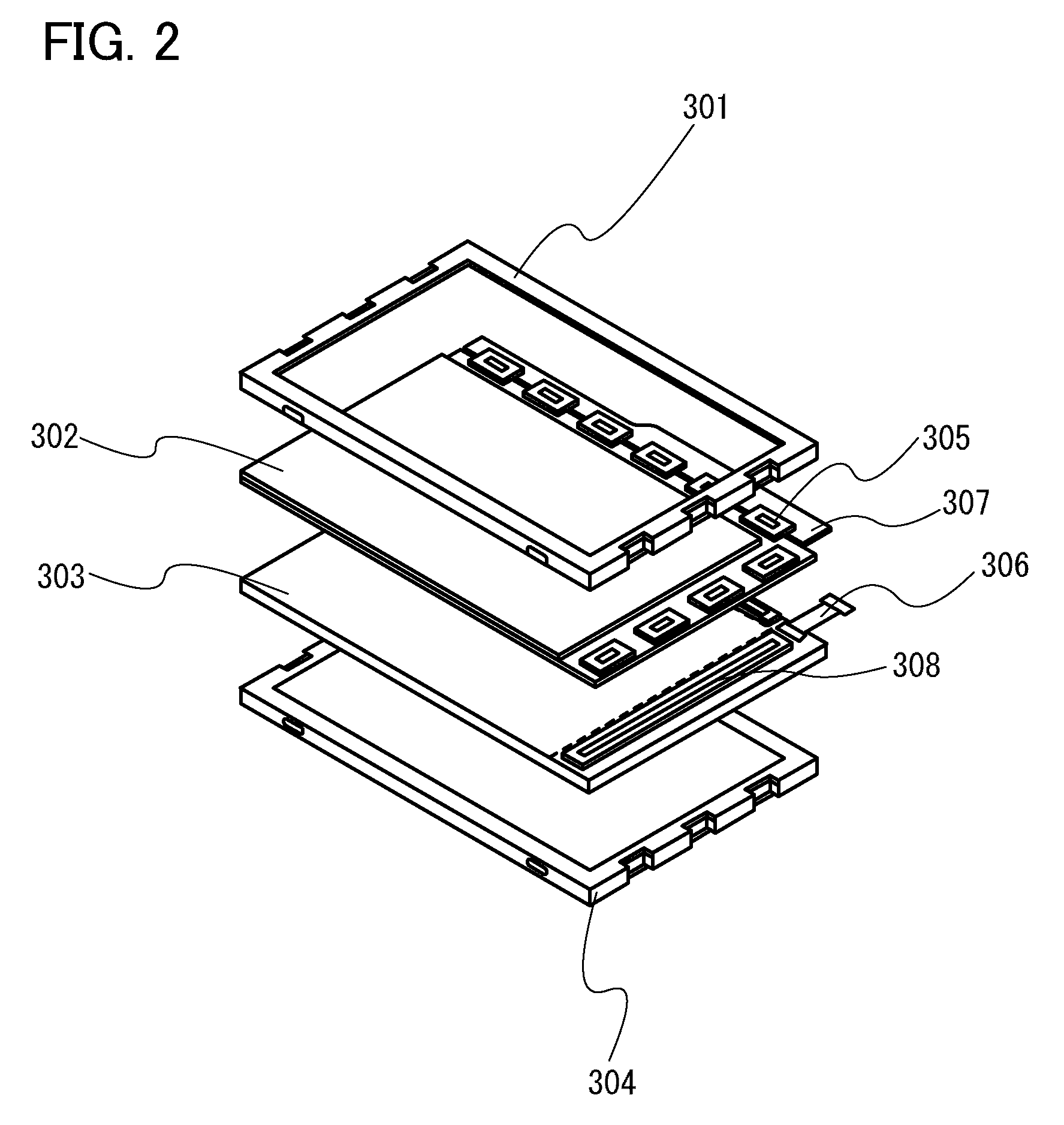

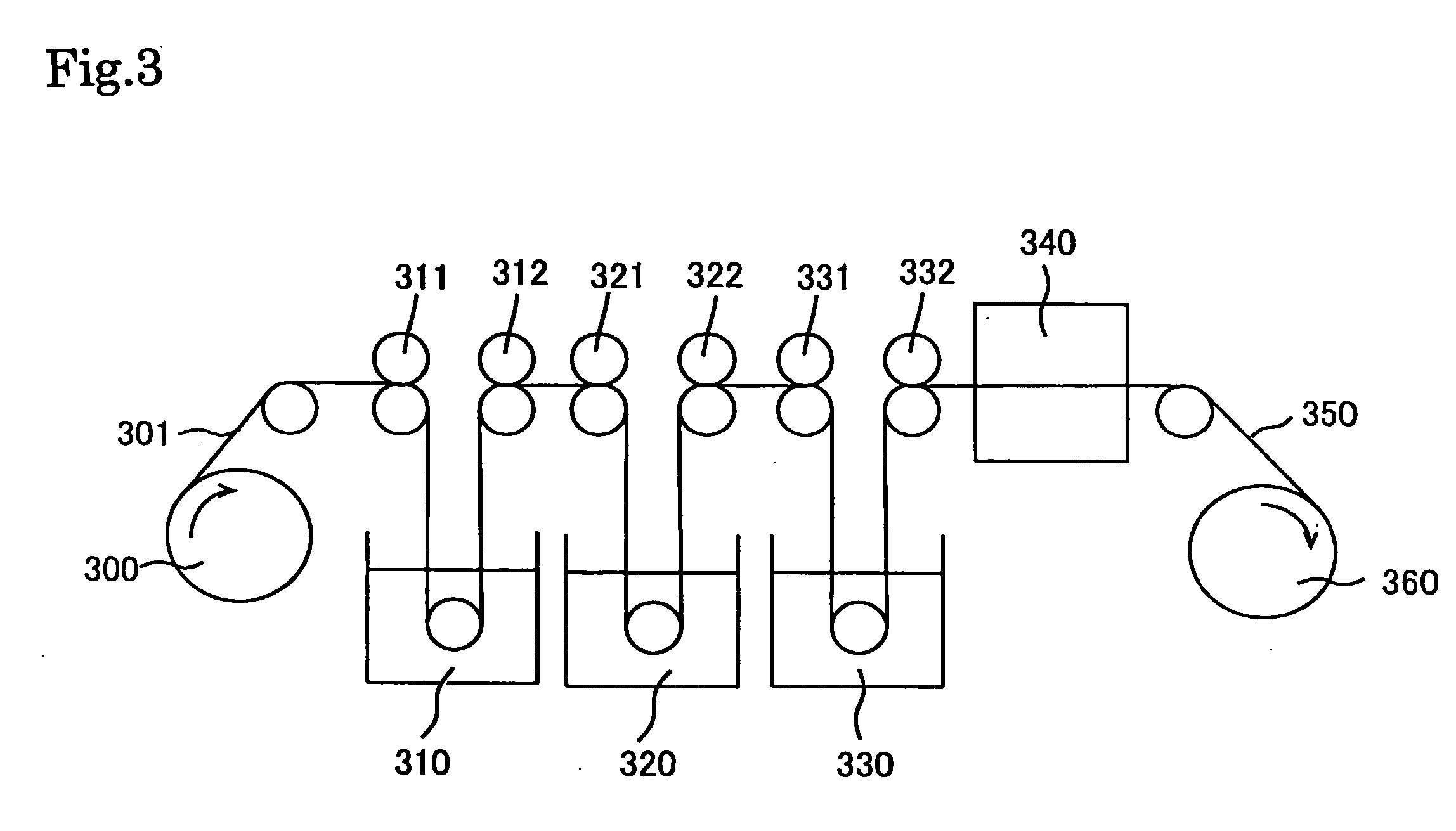

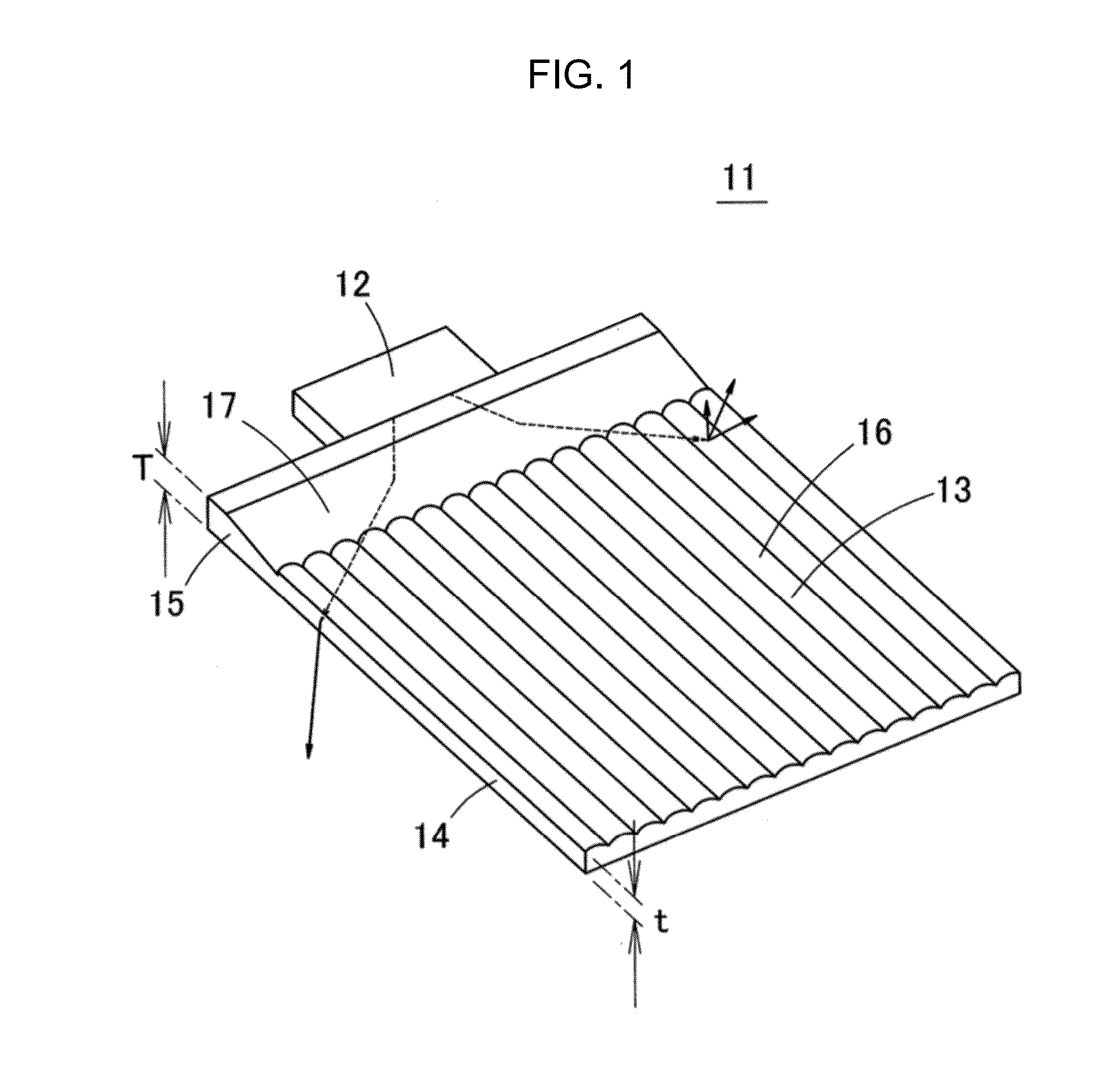

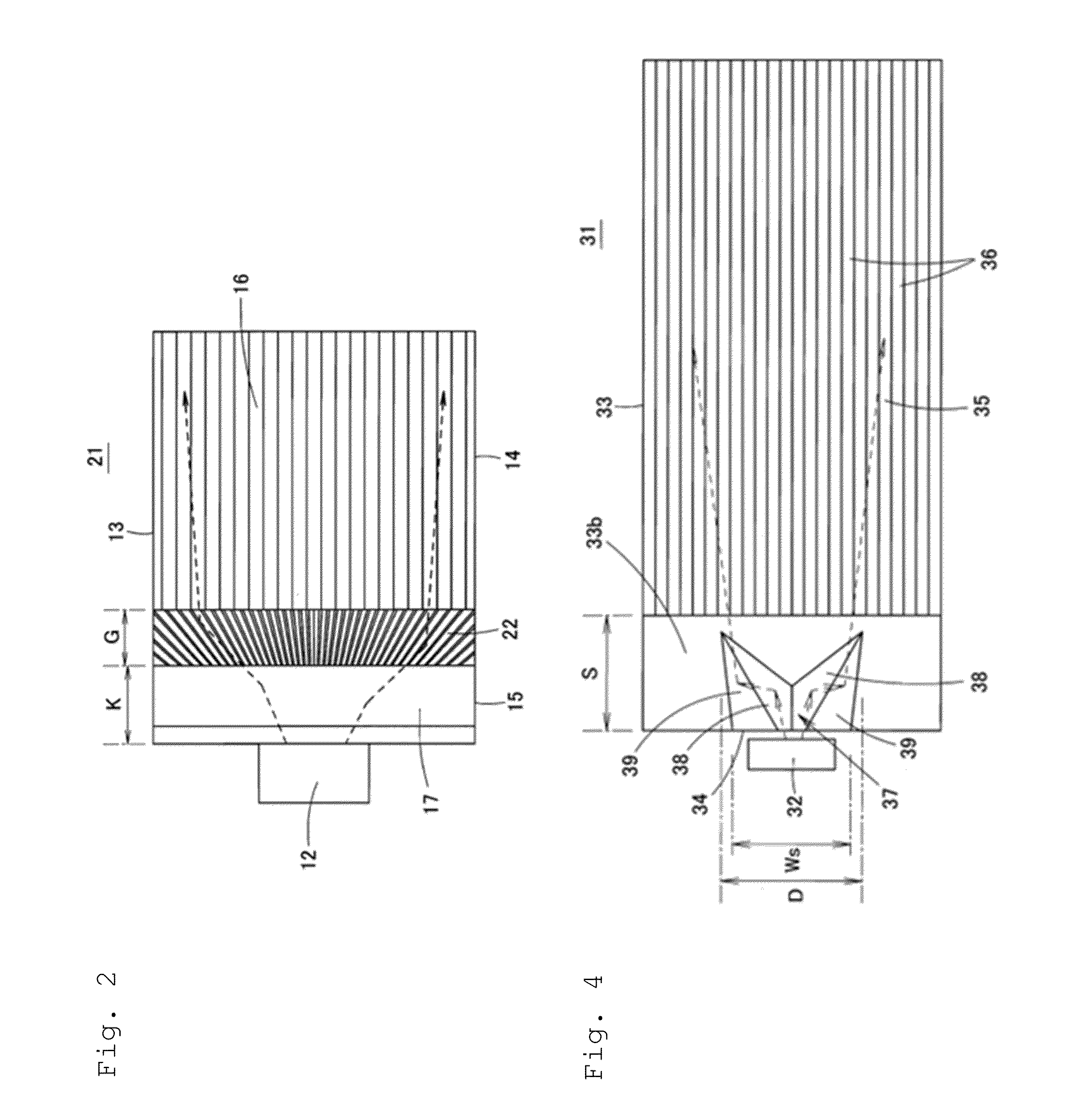

Illumination device, display device, and light guide plate

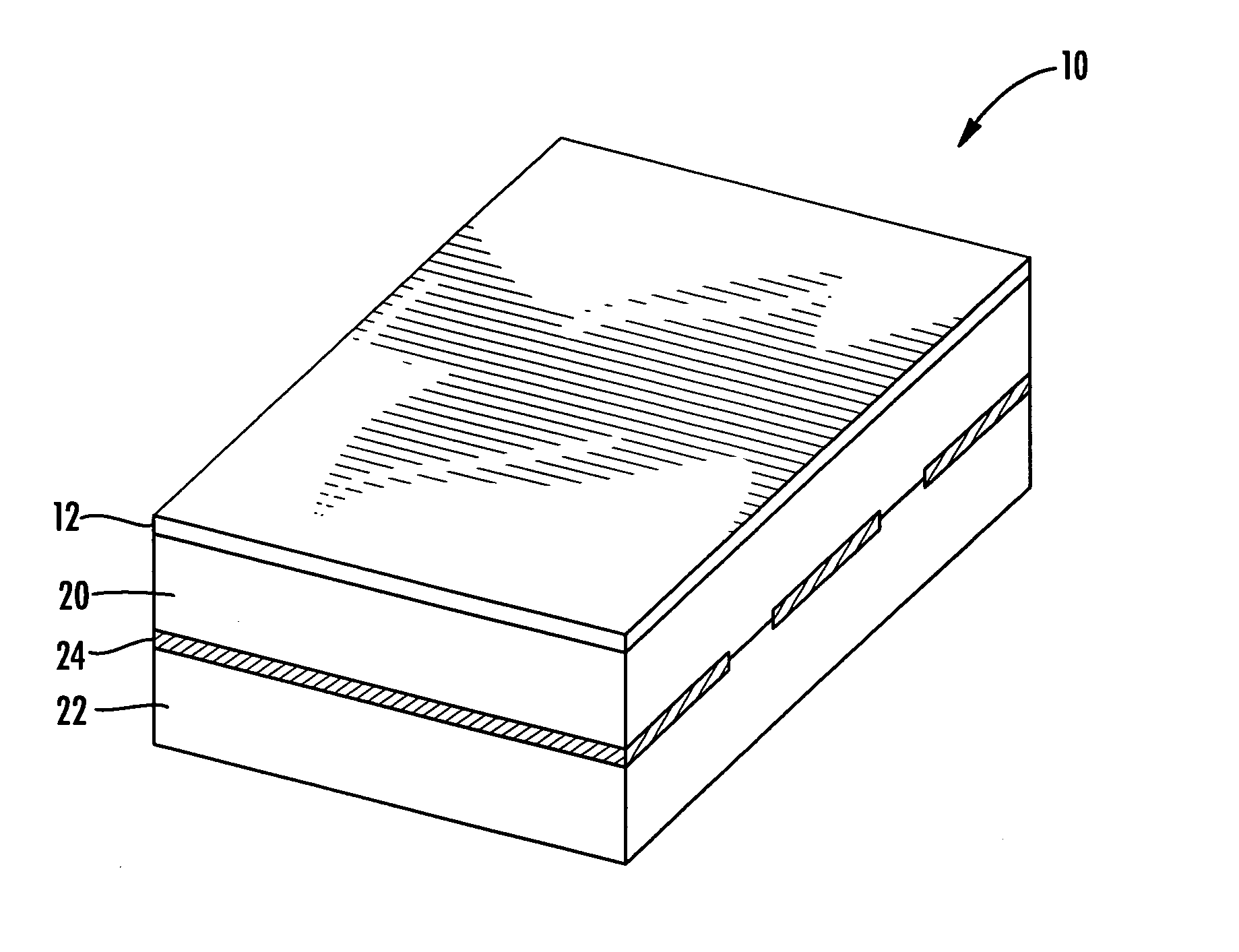

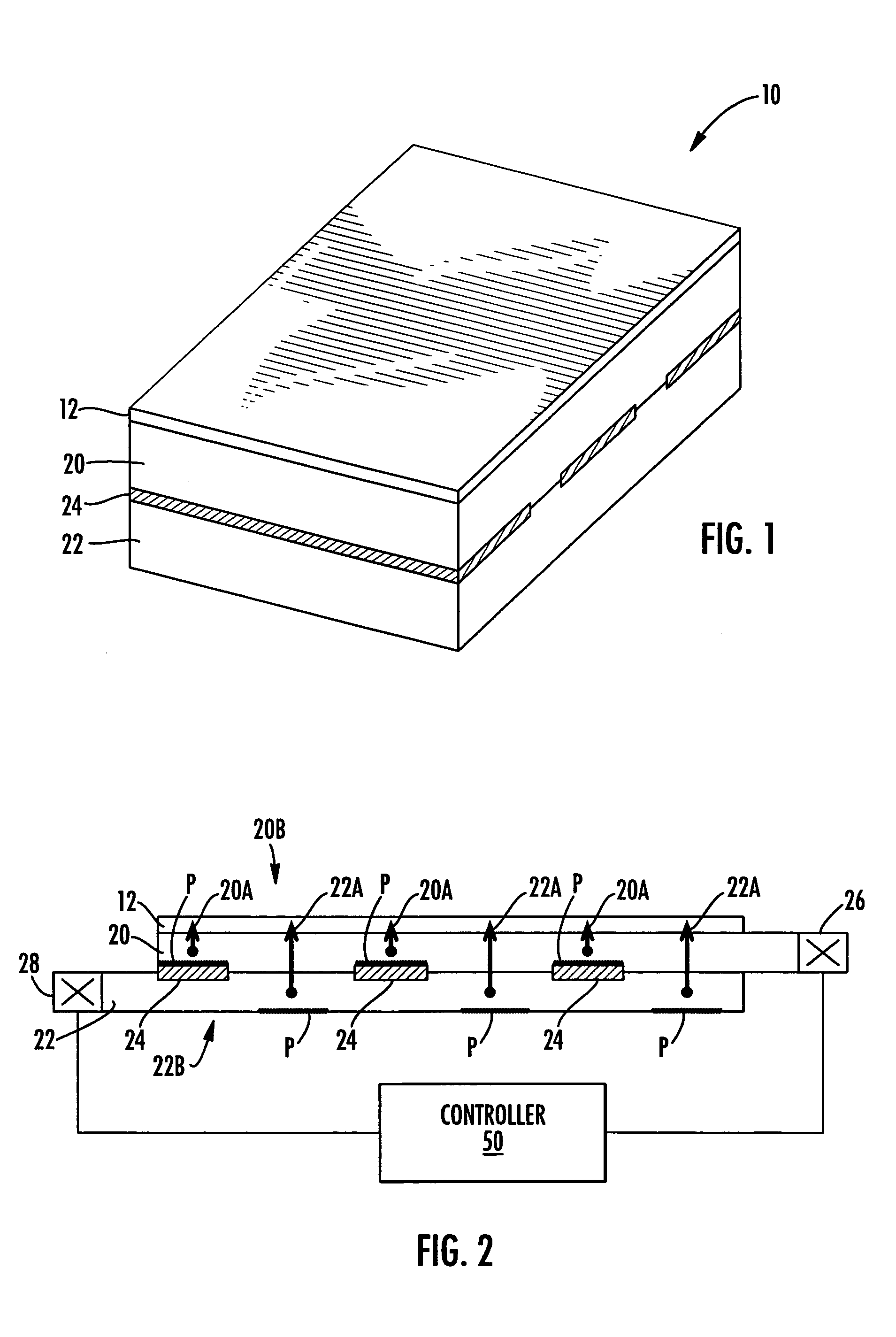

InactiveUS20110025730A1Reduce light leakageRetention strengthCathode-ray tube indicatorsPlanar/plate-like light guidesLight guideOptical axis

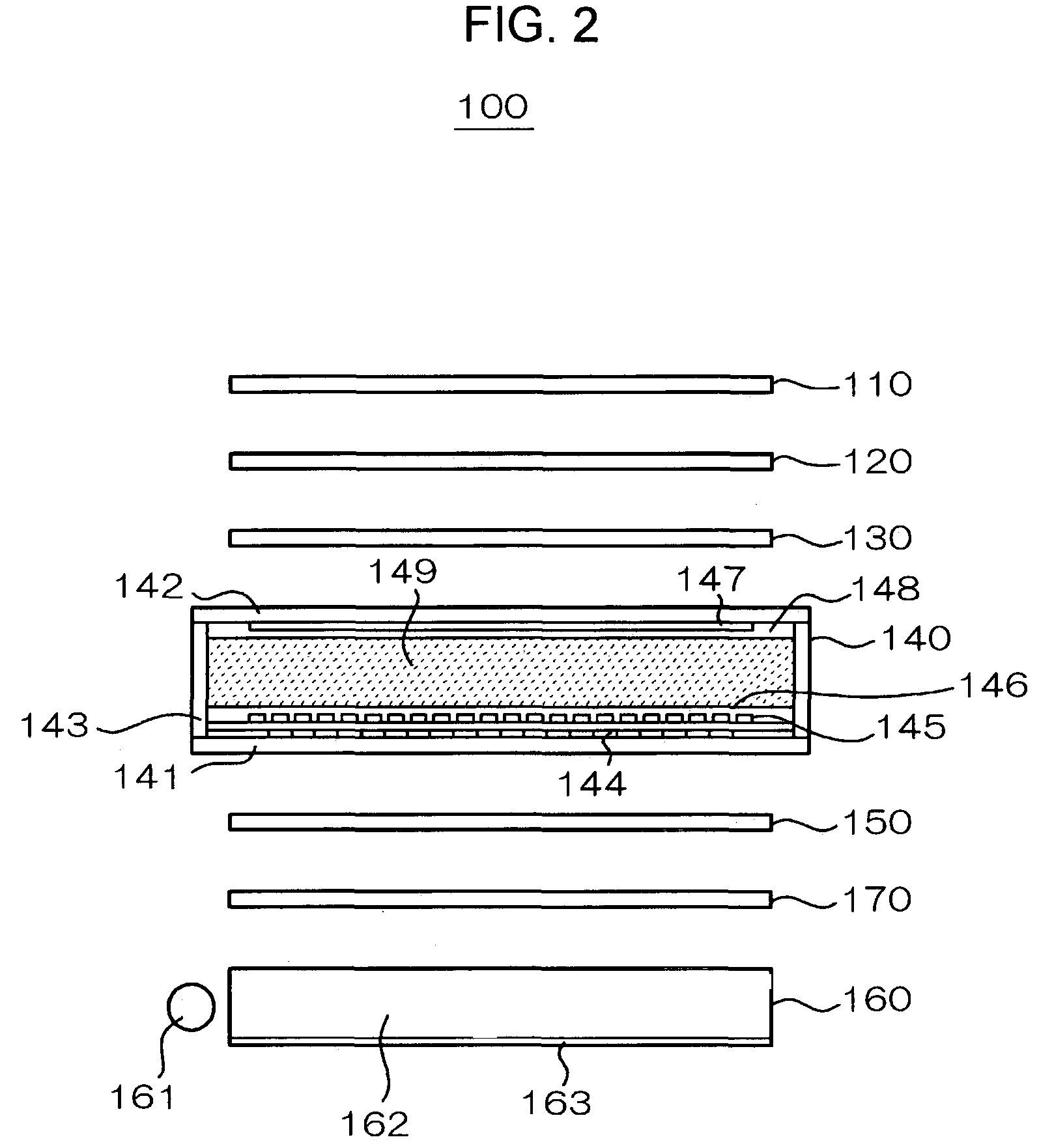

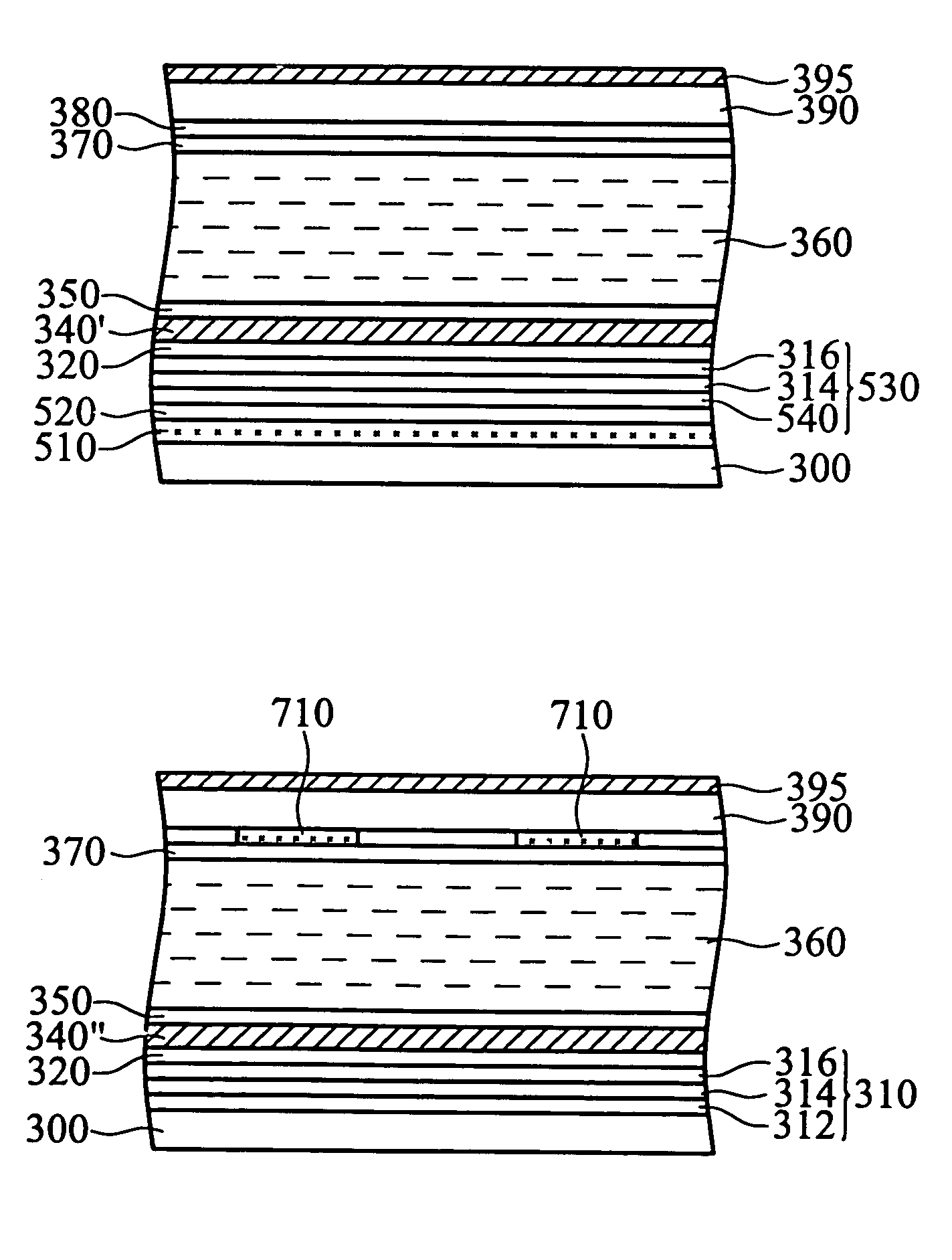

An illumination device (L) includes a plurality of light source units (20) each having a light guide plate (1) and a plurality of light sources (21). The light guide plate (1) has an illumination region (4) through which incident beams of light from the light sources (21) are emitted outward and a light guide region (3) through which the incident beams of light from the light sources (21) are guided toward the illumination region (4), with the light guide region (3) and the illumination region (4) laid side-by-side. The illumination region (4) is divided into a plurality of light-emitting sections (9) by slit sections (8), provided in such a way as to extend along directions of optical axes of the light sources (21), which restrict transmission of light. At least one of the light sources (21) is provided to each of the light-emitting sections (9) in such a way as to be placed side-by-side along the light guide region (3). The light source units (20) are provided in such a way as to be placed side-by-side along at least along a first direction along which the light-emitting sections (9) are arranged in the illumination region (4). There is also provided a slit section (8) in at least part of a space between light-emitting sections (9) between light source units (20) adjacent to each other along the first direction. This makes it possible to provide an illumination device (L) capable of retaining its strength as a combination of light guide blocks while reducing leakage of light into an adjacent area and capable of emitting uniform light.

Owner:SHARP KK

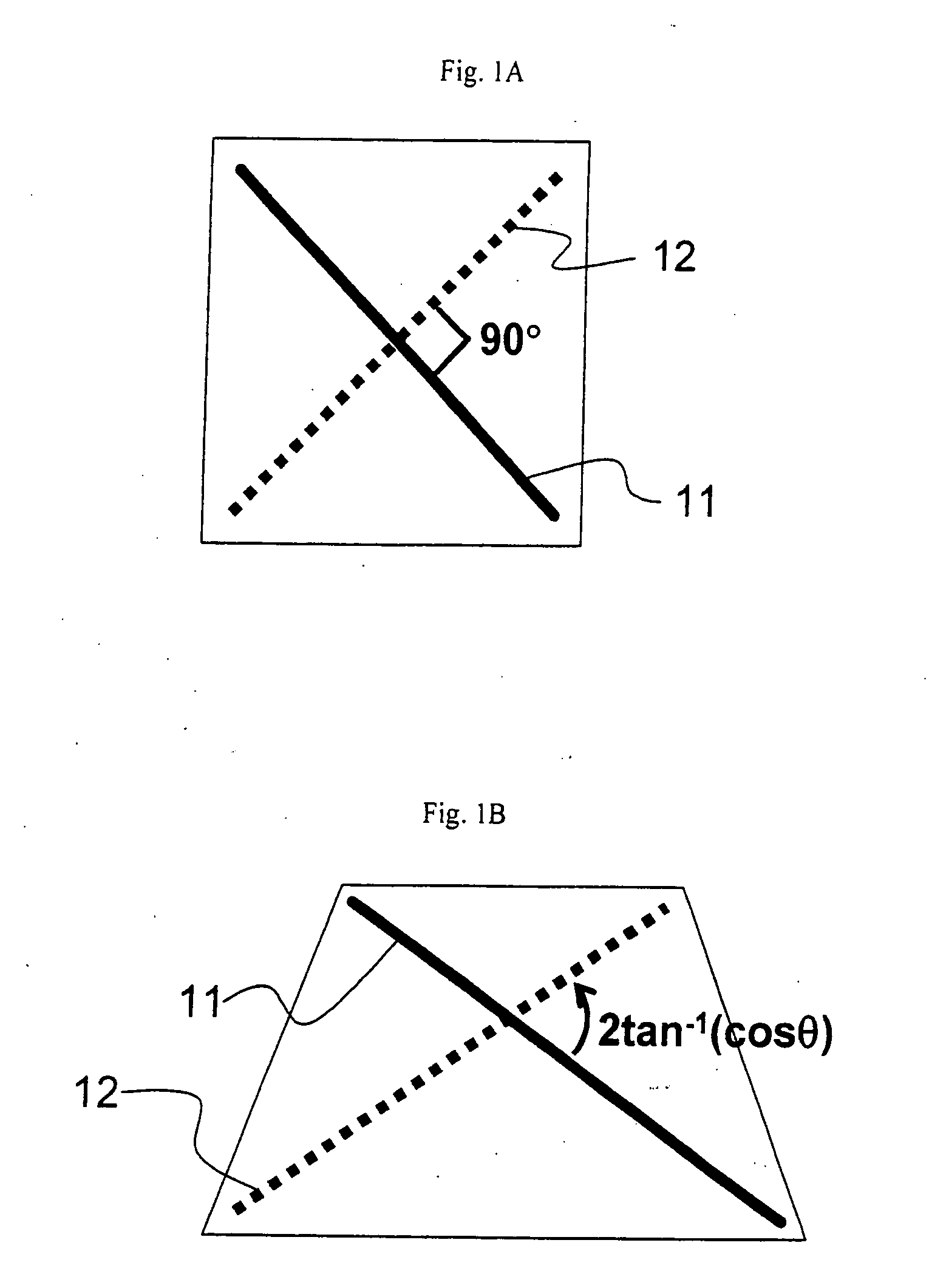

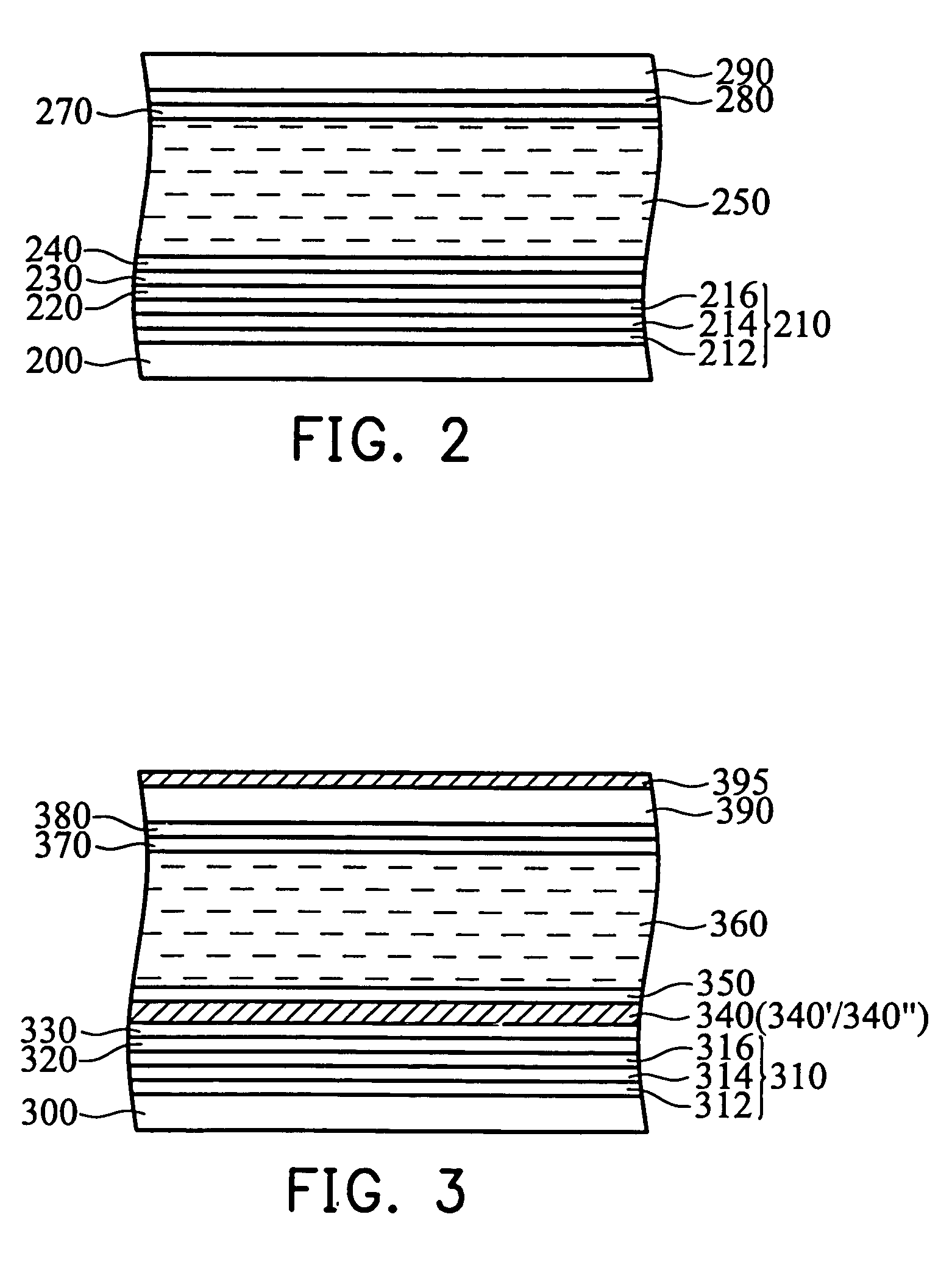

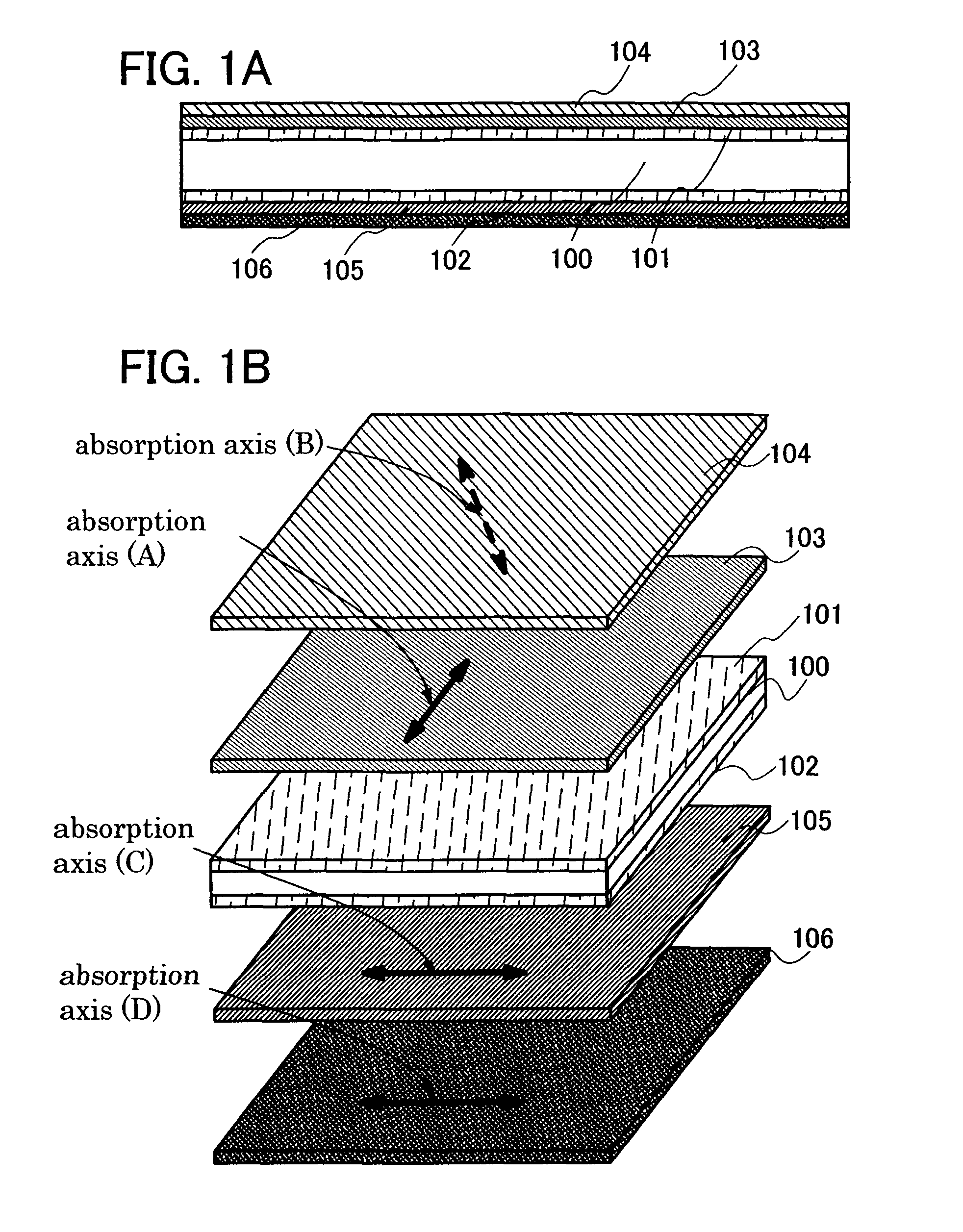

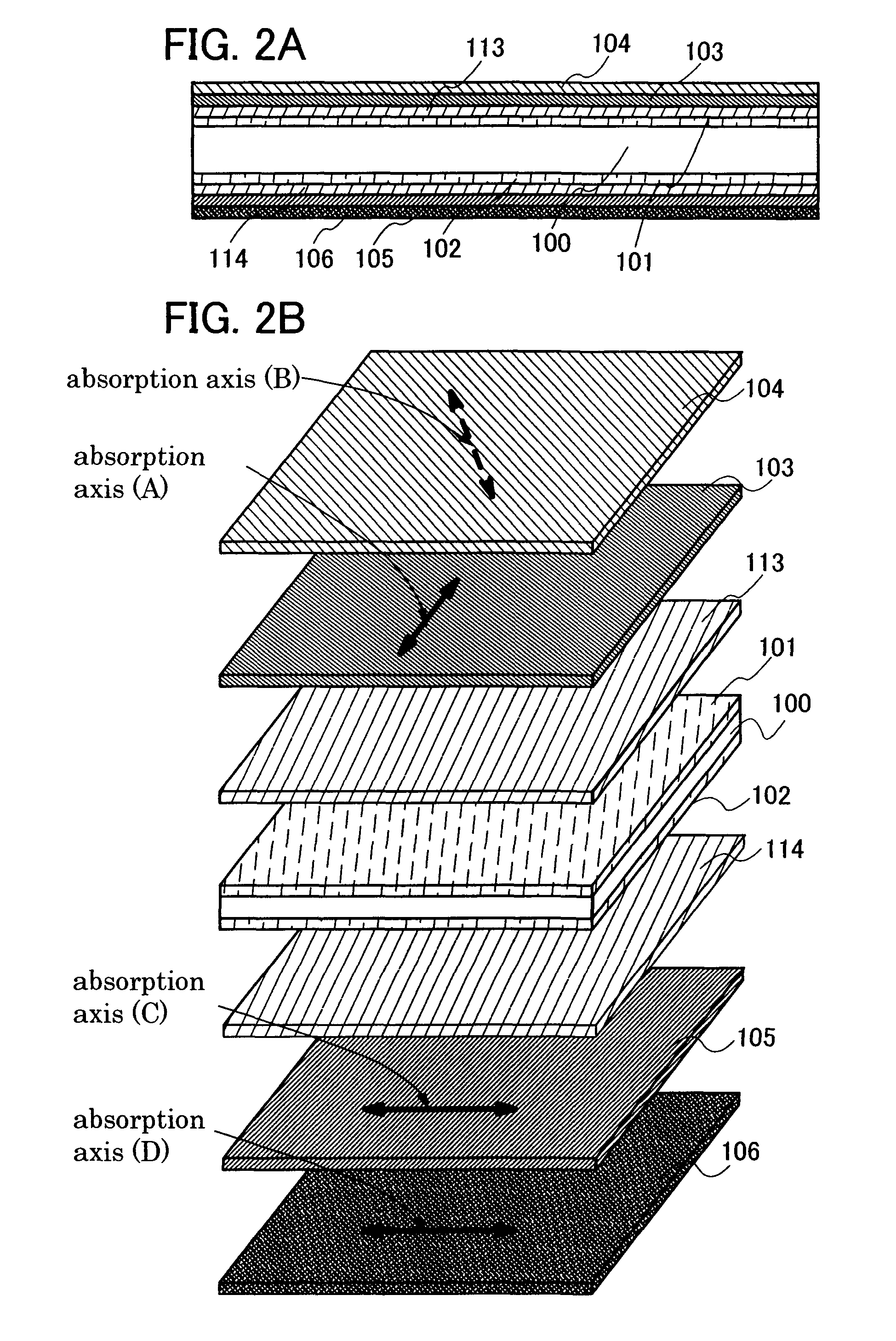

Multi-film compensated liquid crystal display with initial homogeneous alignment

InactiveUS20080158491A1Reduce light leakageWide viewing angleNon-linear opticsLiquid-crystal displayPolarizer

A liquid crystal display having a positive A-film and a negative A-film between a top polarizer and a bottom polarizer to increase the viewing angle of the liquid crystal display by reducing or eliminating light leakage at voltage-off state when viewed from an oblique angle. Method of increasing the viewing angle of the liquid crystal display by reducing or eliminating light leakage at voltage-off stage when viewed from an oblique angle. The compensation is applicable to use with liquid crystal displays having a liquid crystal layer that is homogenously aligned at off-state when no voltage is applied to the liquid crystal layer, such as IPS and FFS mode liquid crystal displays.

Owner:UNIV OF CENT FLORIDA RES FOUND INC +1

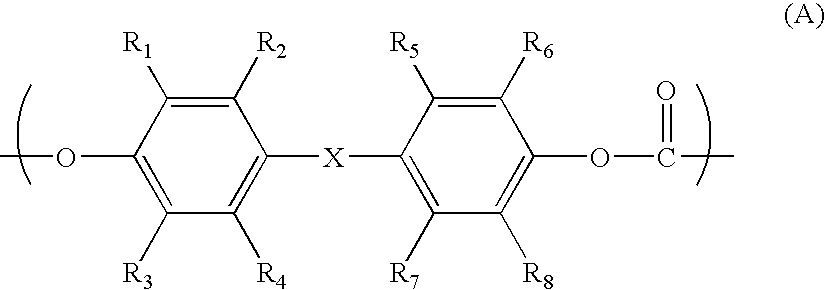

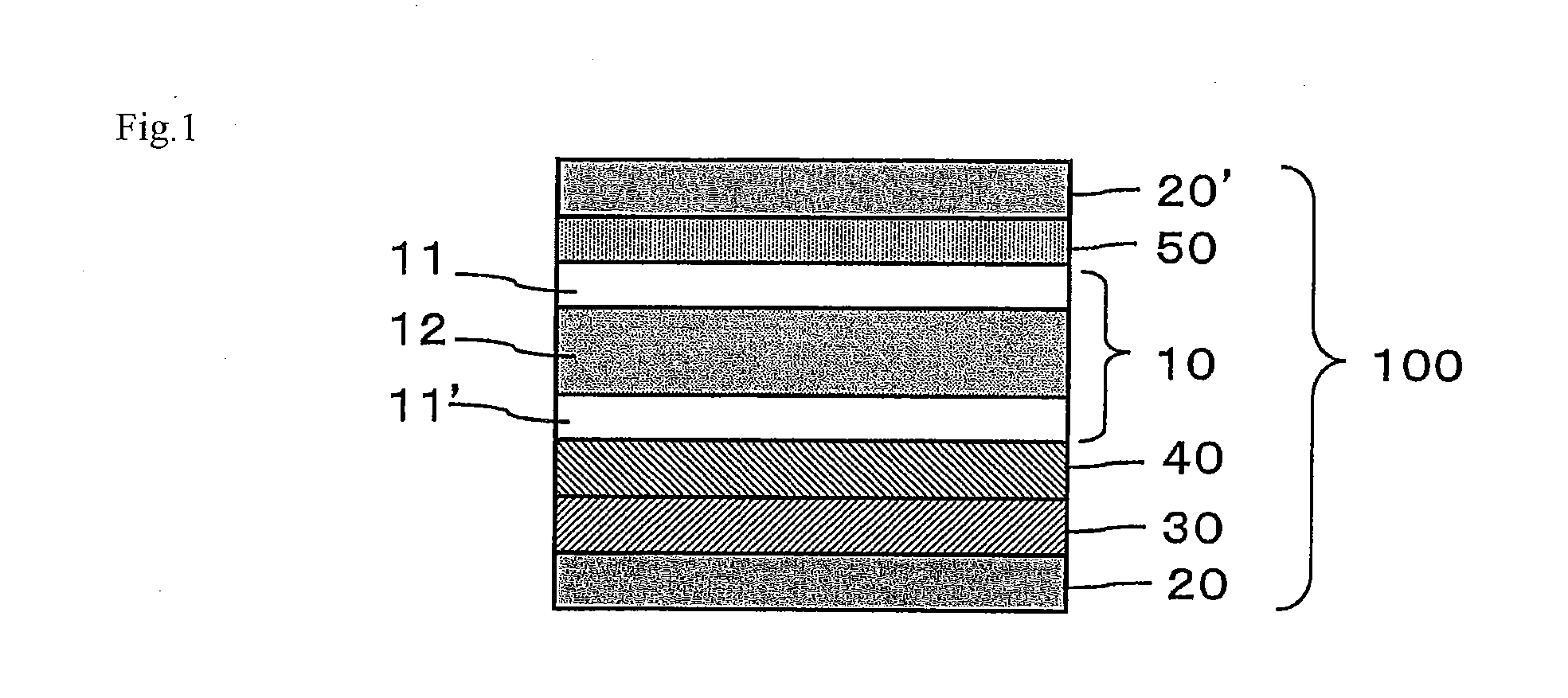

Liquid crystal display element, and use of phase difference film used the same for

InactiveUS20040239852A1Reduce light leakageSmall retardationNon-linear opticsLiquid-crystal displayPhase difference

The present invention provides a liquid crystal display device of VA mode having decreased leakage of light over a wide range and giving a clear and almost achromatic black display by using a retardation film A having smaller retardation with shorter wavelength in combination with a retardation film C having larger retardation with shorter wavelength. Accordingly, a high-quality liquid crystal display device having excellent picture quality can be produced by the present invention.

Owner:TEIJIN LTD

Liquid crystal display device

ActiveUS6987547B2Light utilization efficiencyThin thicknessNon-linear opticsWire gridLiquid-crystal display

A liquid crystal display (LCD) device, with an organic electroluminescent display (OLED) element serving as a light source, a common electrode, and a polarizer which is a wire grid polarizer or a thin film polarizer are formed on a lower substrate. A pixel electrode is formed on an upper substrate. According to the invention, a thinner integrated LCD device with improved light utilization efficiency is obtained.

Owner:HANNSTAR DISPLAY CORPORATION

Polarizing plate and liquid crystal display

ActiveUS20100231830A1Improved gray scale inversionSimple configurationDiffusing elementsPolarising elementsPolarizerLiquid-crystal display

A polarizing plate for a liquid crystal display is provided and includes a first protective film, a polarizer, a second protective film and a light diffusion layer in order. The light diffusion layer is a layer including a translucent resin and translucent particles having a refractive index different from a refractive index of the translucent resin. The internal haze of the light diffusion layer is 45% to 80%.

Owner:FUJIFILM CORP

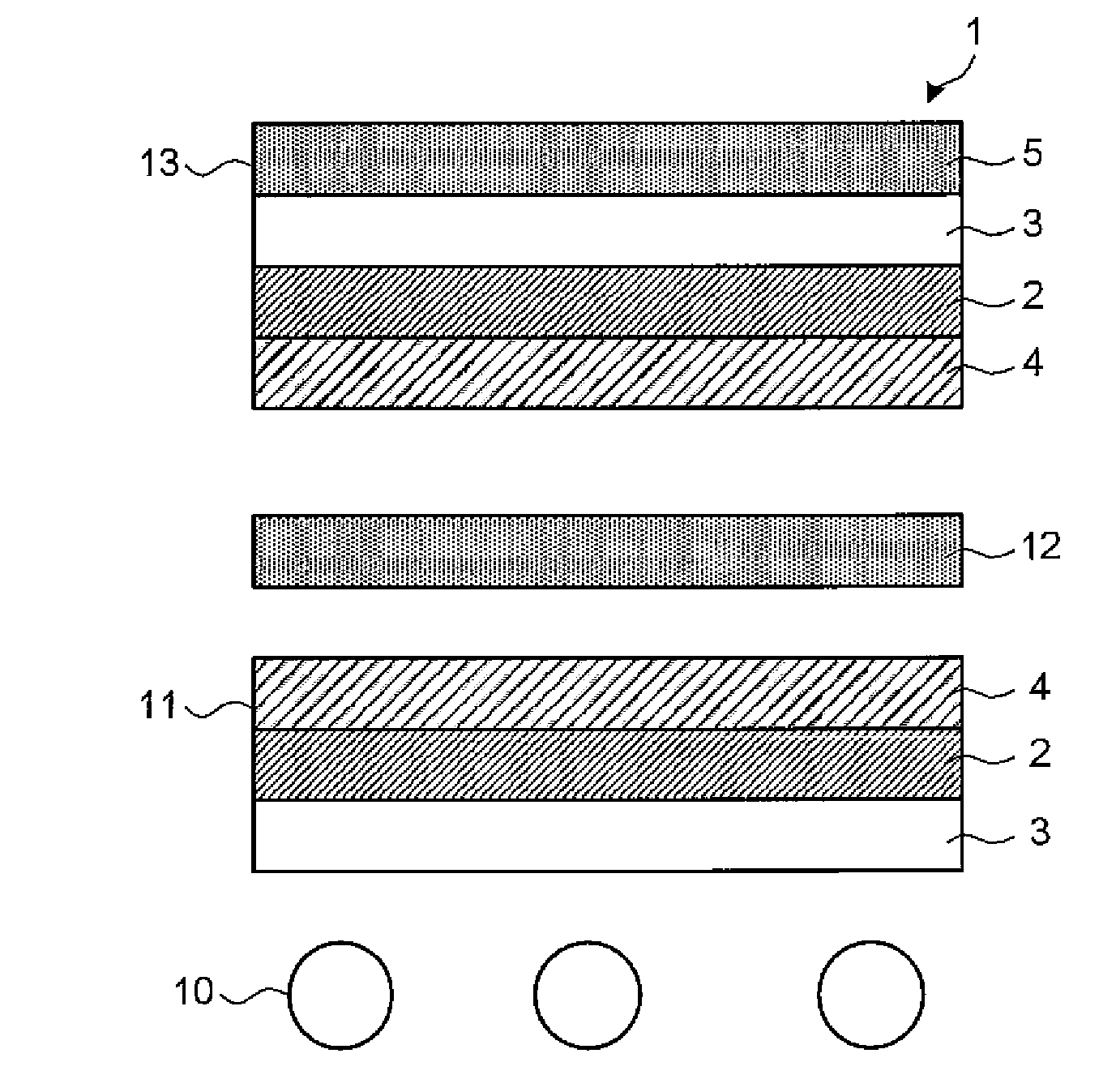

Composite film and display device

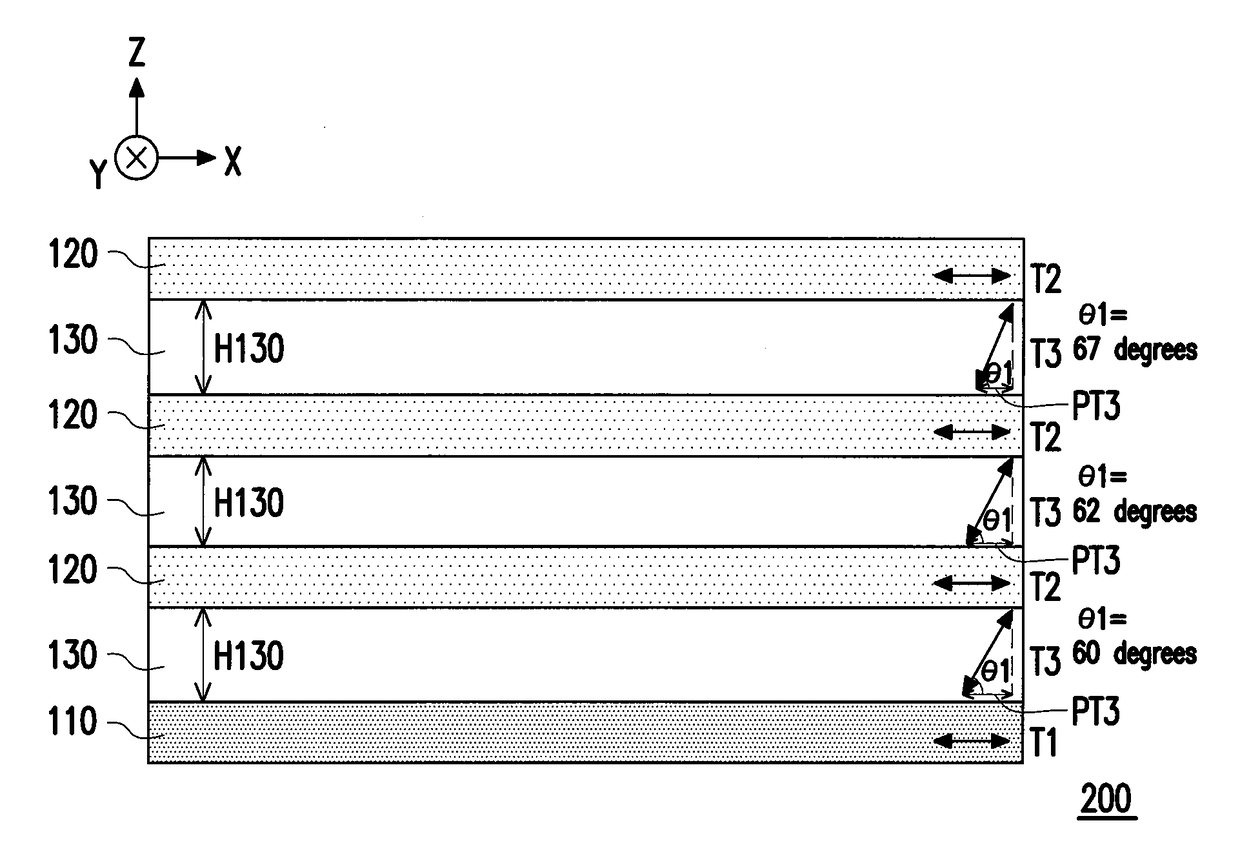

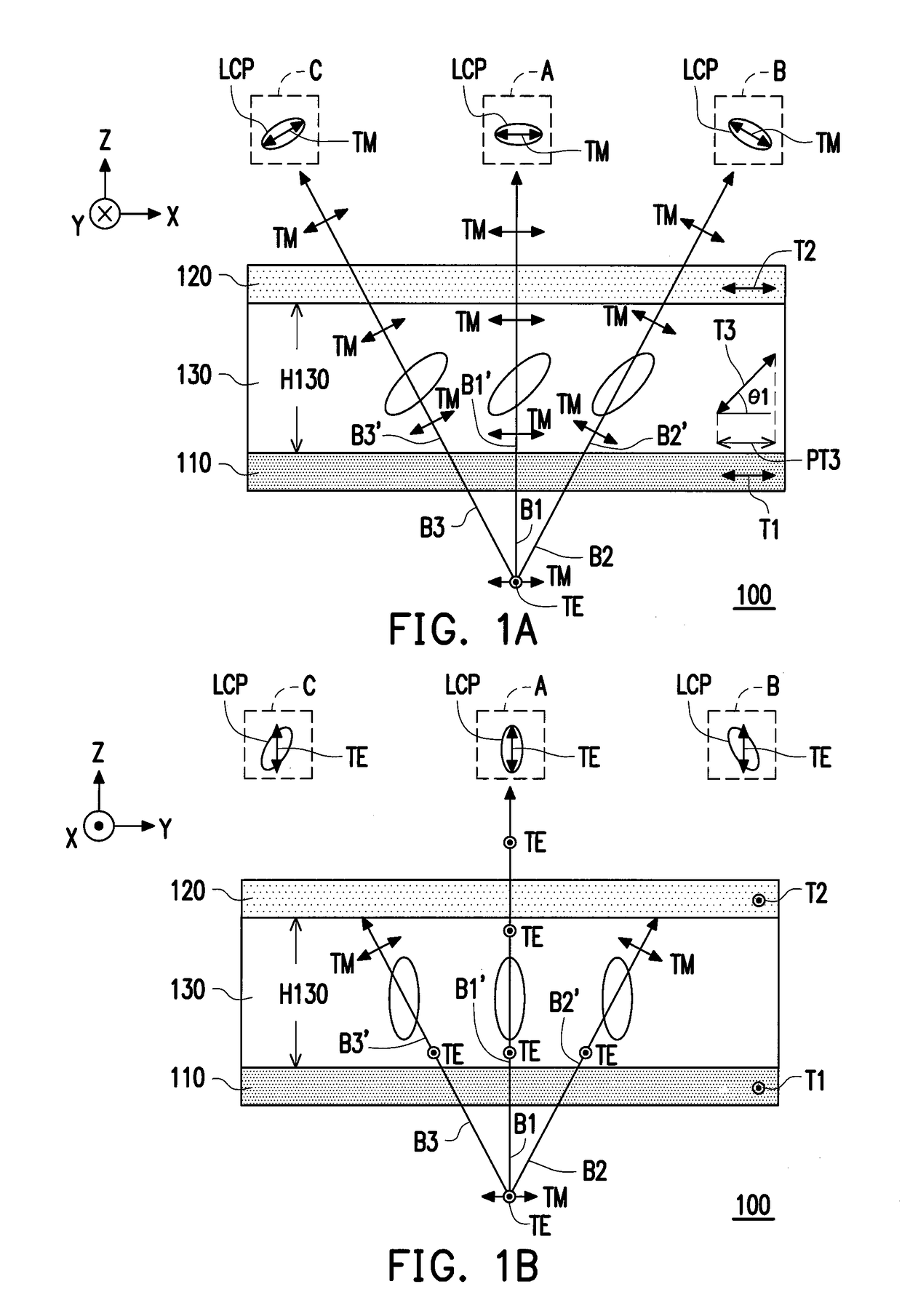

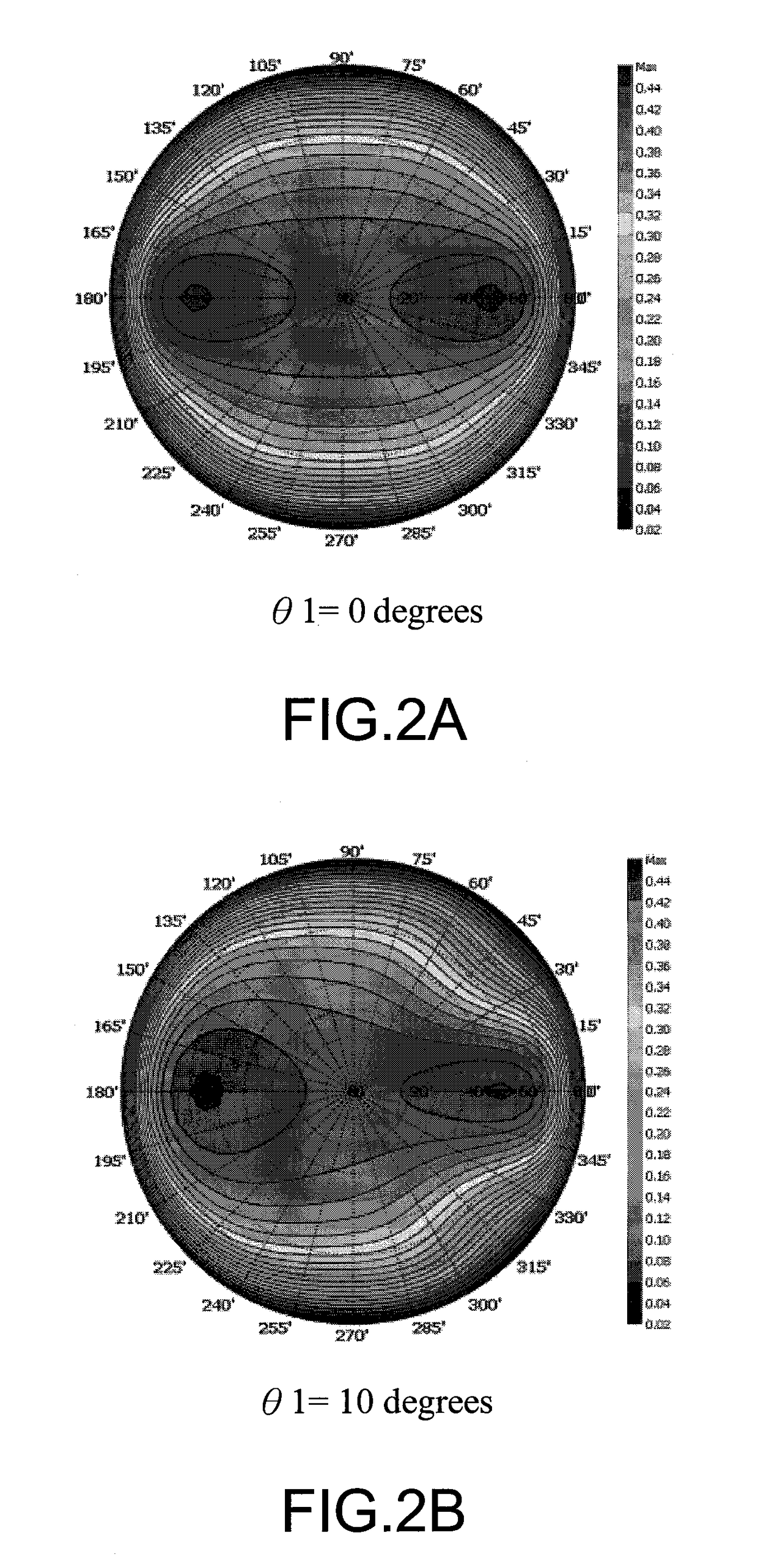

ActiveUS20170343715A1Limited viewing angleReduce large-angle light leakagePolarising elementsNon-linear opticsComposite filmOptical axis

A composite film including a first polarizing film, at least one second polarizing film, and at least one first phase compensation film is provided. The first polarizing film has a first transmission axis. Each second polarizing film has a second transmission axis parallel to the first transmission axis. The at least one first phase compensation film is disposed between the first polarizing film and the at least one second polarizing film. Each first phase compensation film has a first optical axis. An orthographic projection of the first optical axis on the first polarizing film is parallel to an axial direction of the first transmission axis, and a first included angle between the first optical axis and the first polarizing film is greater than 0 degrees and less than 90 degrees. A display device is also provided.

Owner:CORETRONIC

Illuminant keyboard device

ActiveUS8592702B2Reduce difficultyReduce light leakageContact mechanismsMeasurement apparatus componentsLight guideMembrane switch

A illuminant keyboard device includes a bottom frame having a plurality of latch parts, a plurality of keying units disposed on the bottom frame, a membrane switch interposed between the bottom frame and the keying units, a light guide plate interposed between the membrane switch and the bottom frame, a least a light source disposed on predetermined position of the light guide plate, a plate interposed between the membrane switch and the light guide plate and a light-shielding plate interposed between the membrane switch and the keying units. The light guide plate has a plurality of first holes and the plate has a plurality of second holes, the diameter of each of the first holes is larger than the diameter of each of the second holes.

Owner:CHICONY ELECTRONICS

Polarizing plate, liquid crystal display and protective film

ActiveCN101460306AImprove scratch resistanceHigh mechanical strengthSynthetic resin layered productsPolarising elementsVisibilityTectorial membrane

Disclosed is a polarizing plate having high mechanical strength, while being excellent in flexibility and abrasion resistance. This polarizing plate is not deteriorated in visibility even under high temperature, high humidity conditions, and hardly suffers from visibility obstacles such as color shading due to dimensional change. Also disclosed is a liquid crystal display using such a polarizing plate. A film mainly containing a thermoplastic resin and composed of a plurality of layers is employed as a first protective film used on the viewer side of the polarizing plate, and at least one surface layer of the first protective film is mainly composed of an acrylic resin. A second protective layer having specific characteristics is arranged on the liquid crystal cell side.

Owner:ZEON CORP

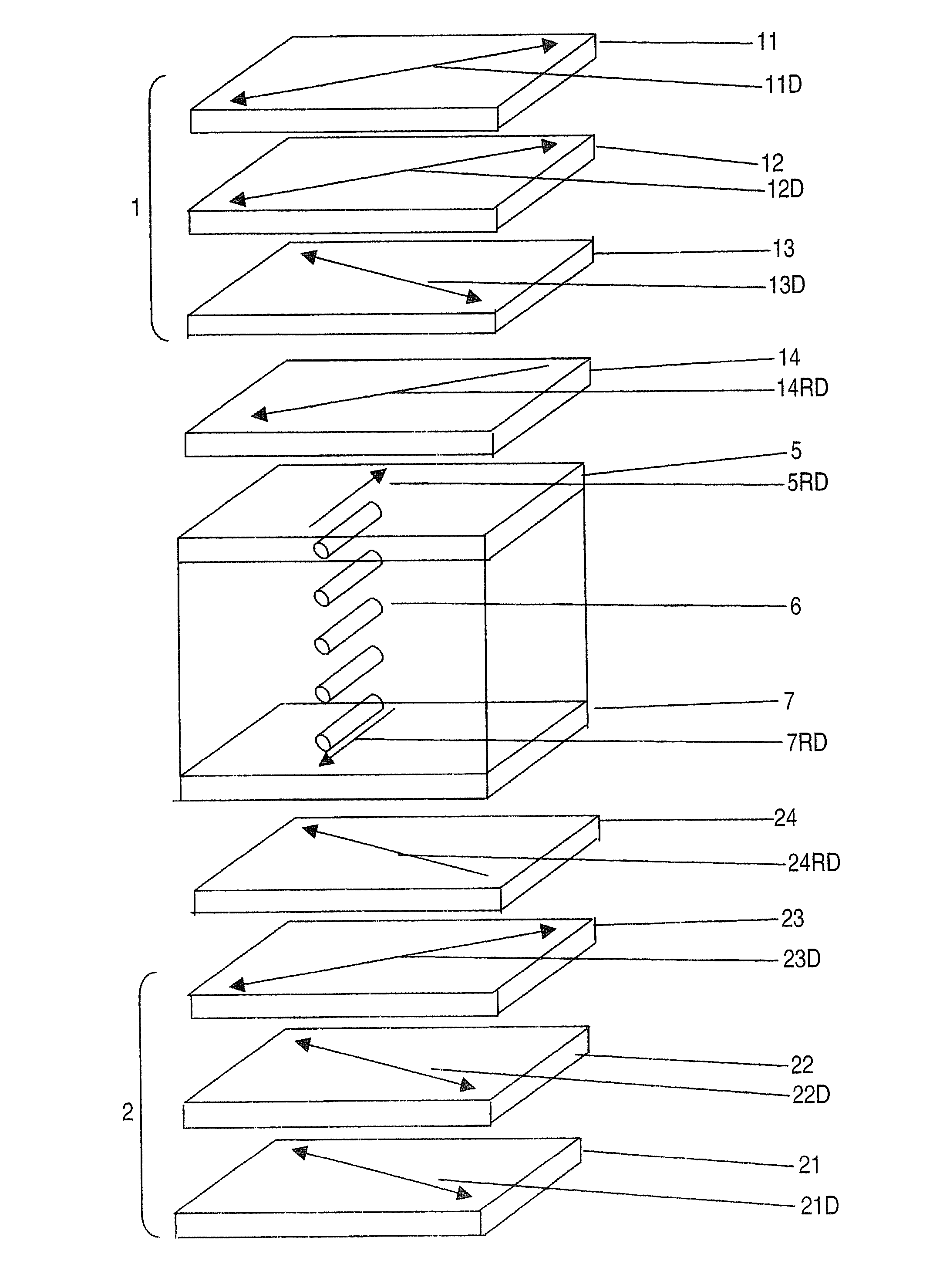

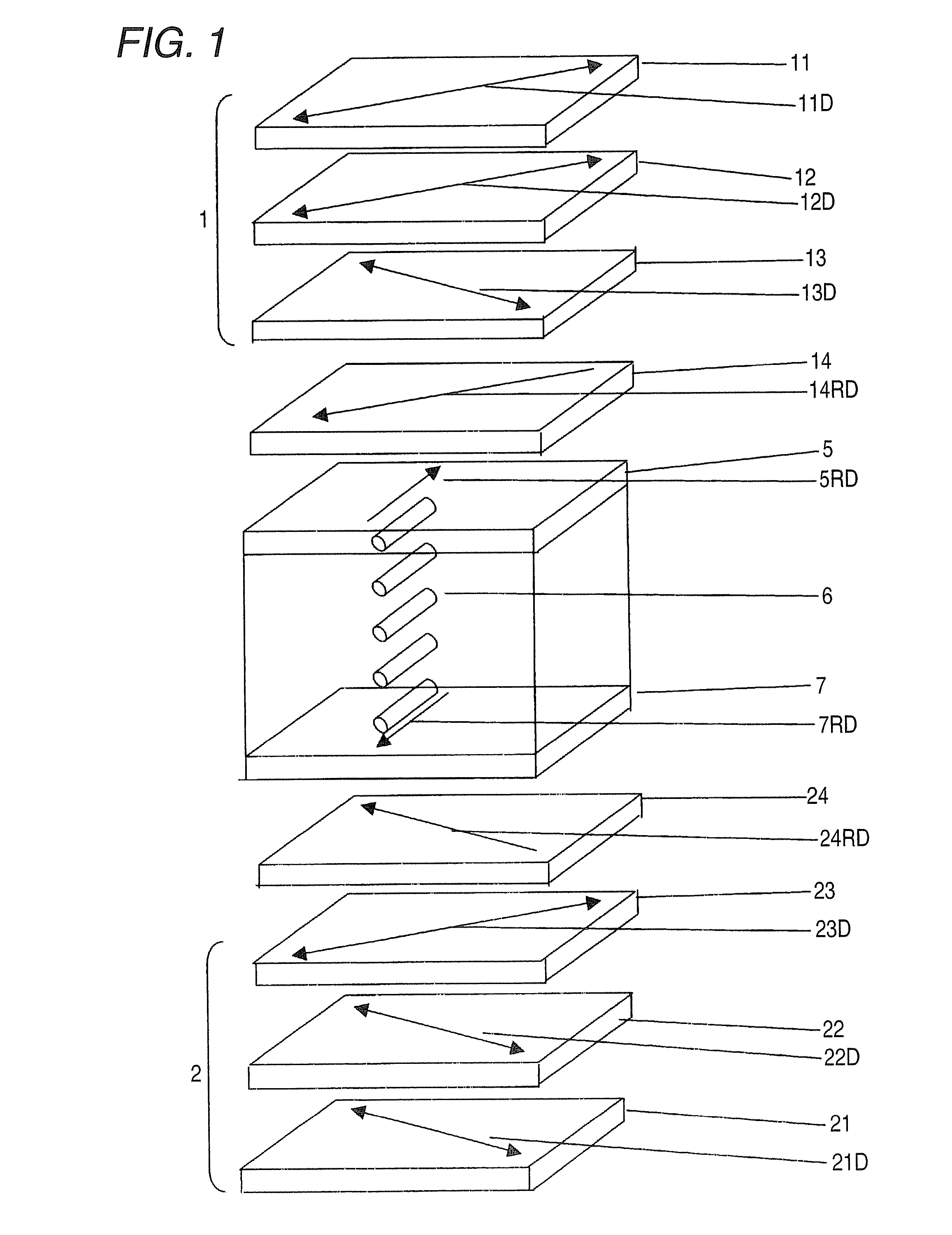

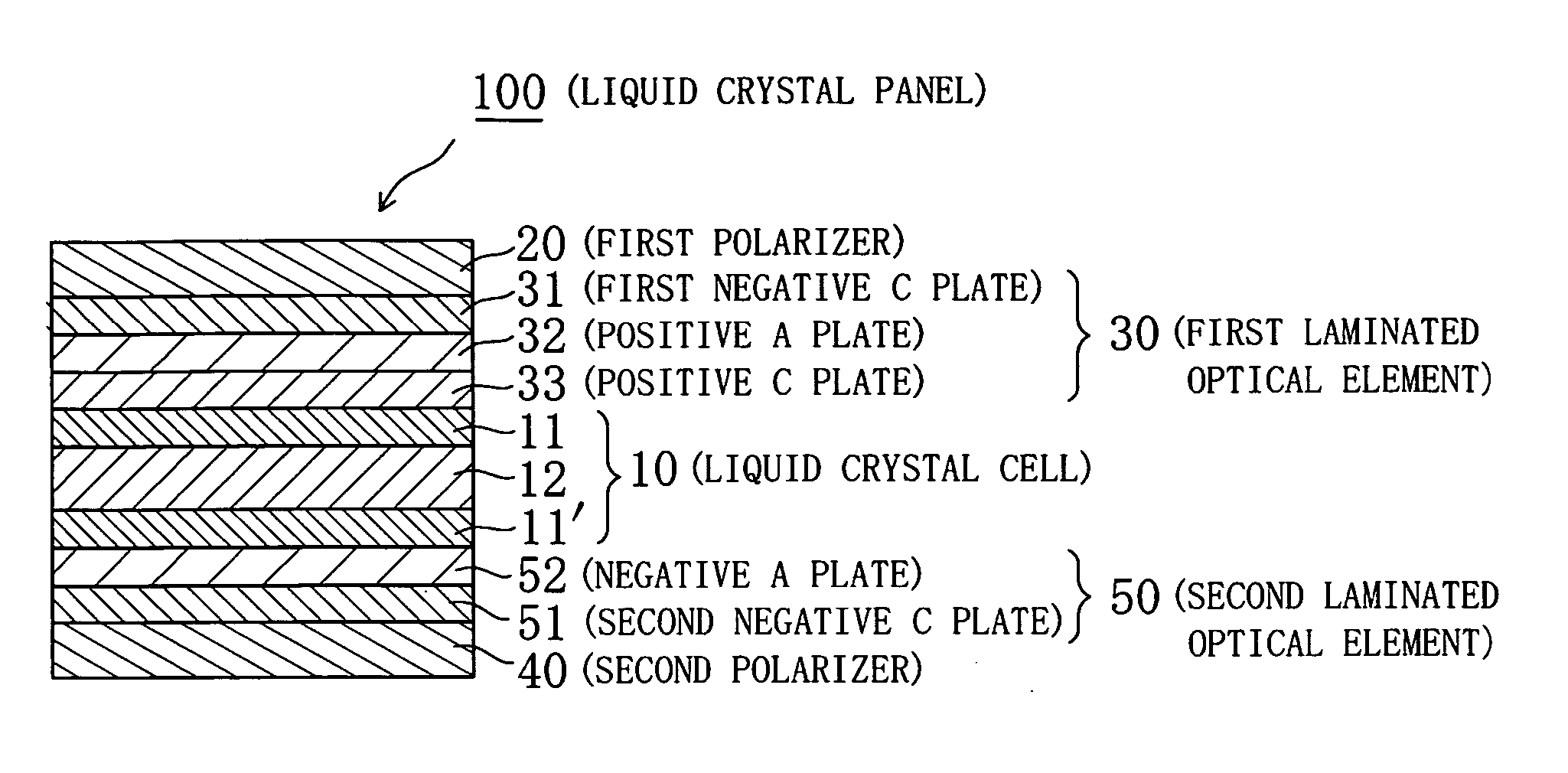

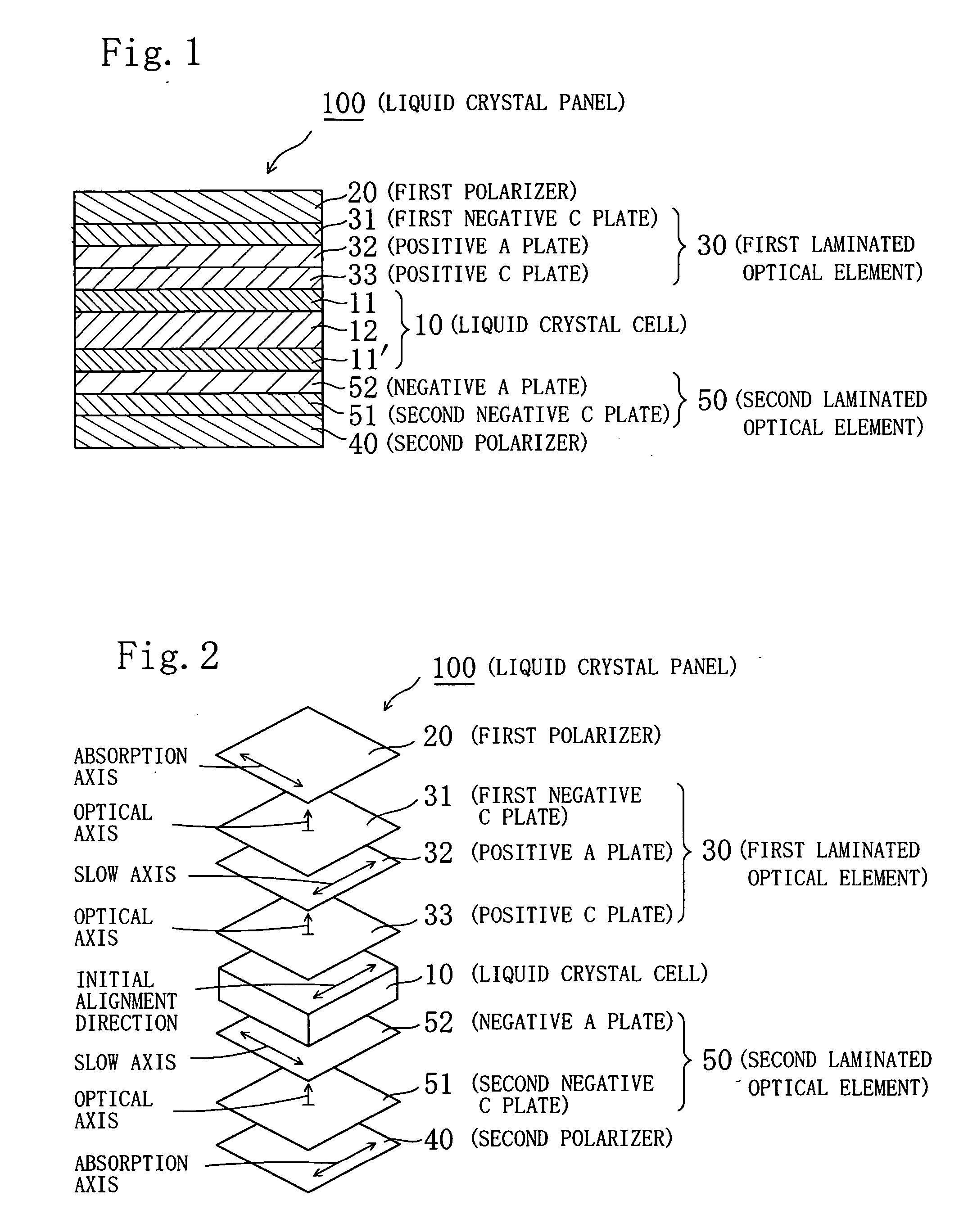

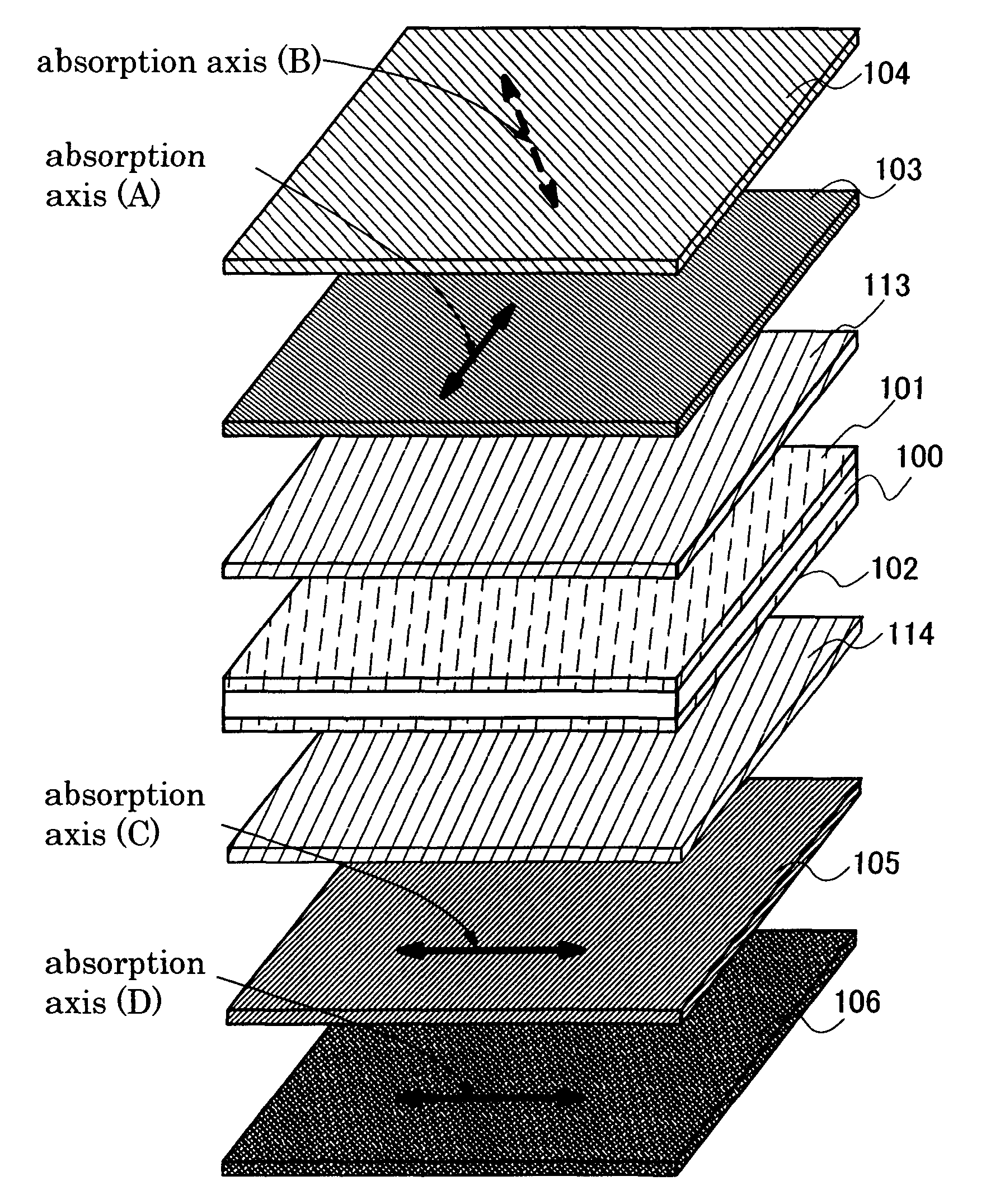

Liquid Crystal Panel, Liquid Crystal Television, and Liquid Crystal Display Apparatus

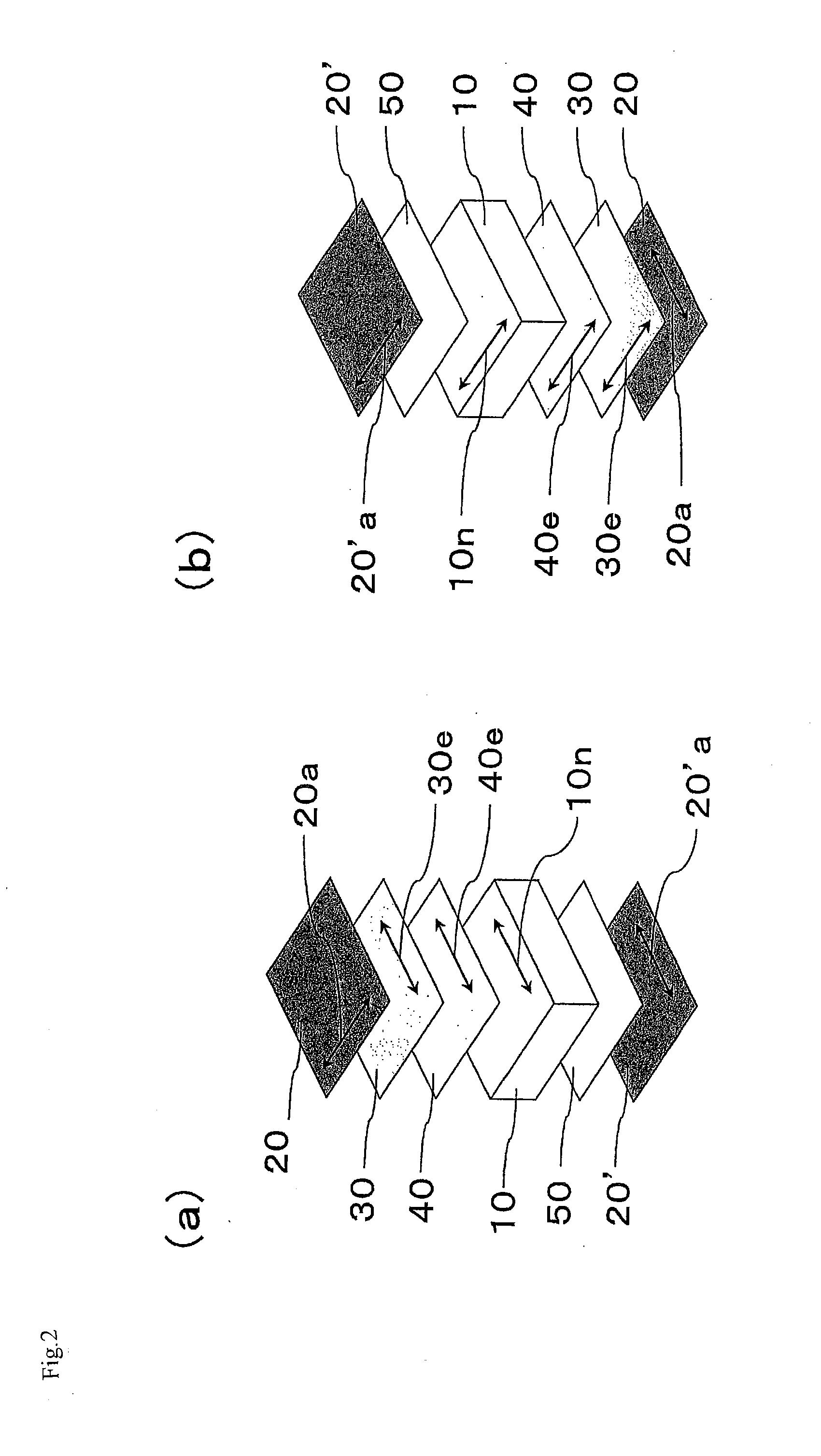

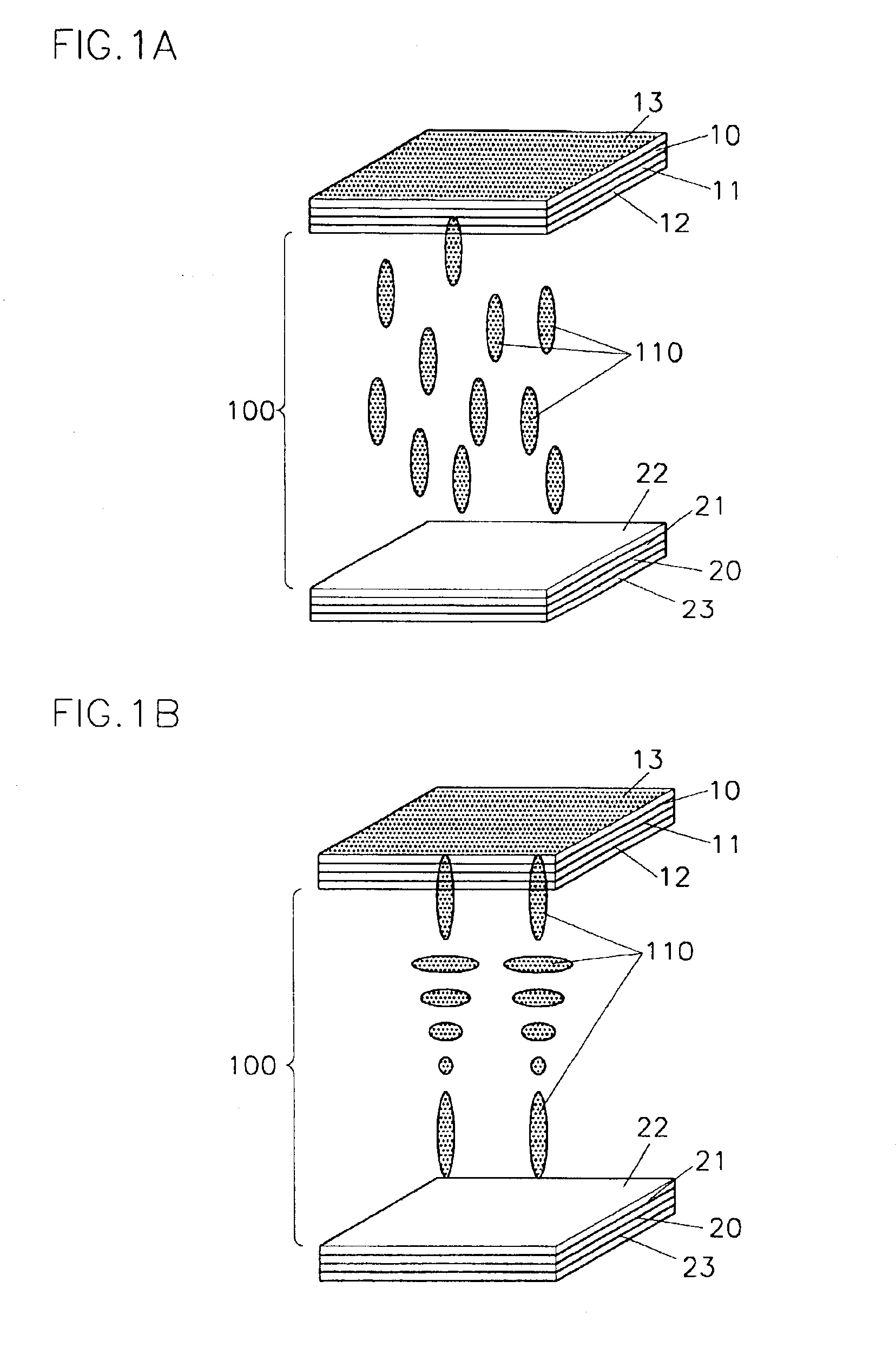

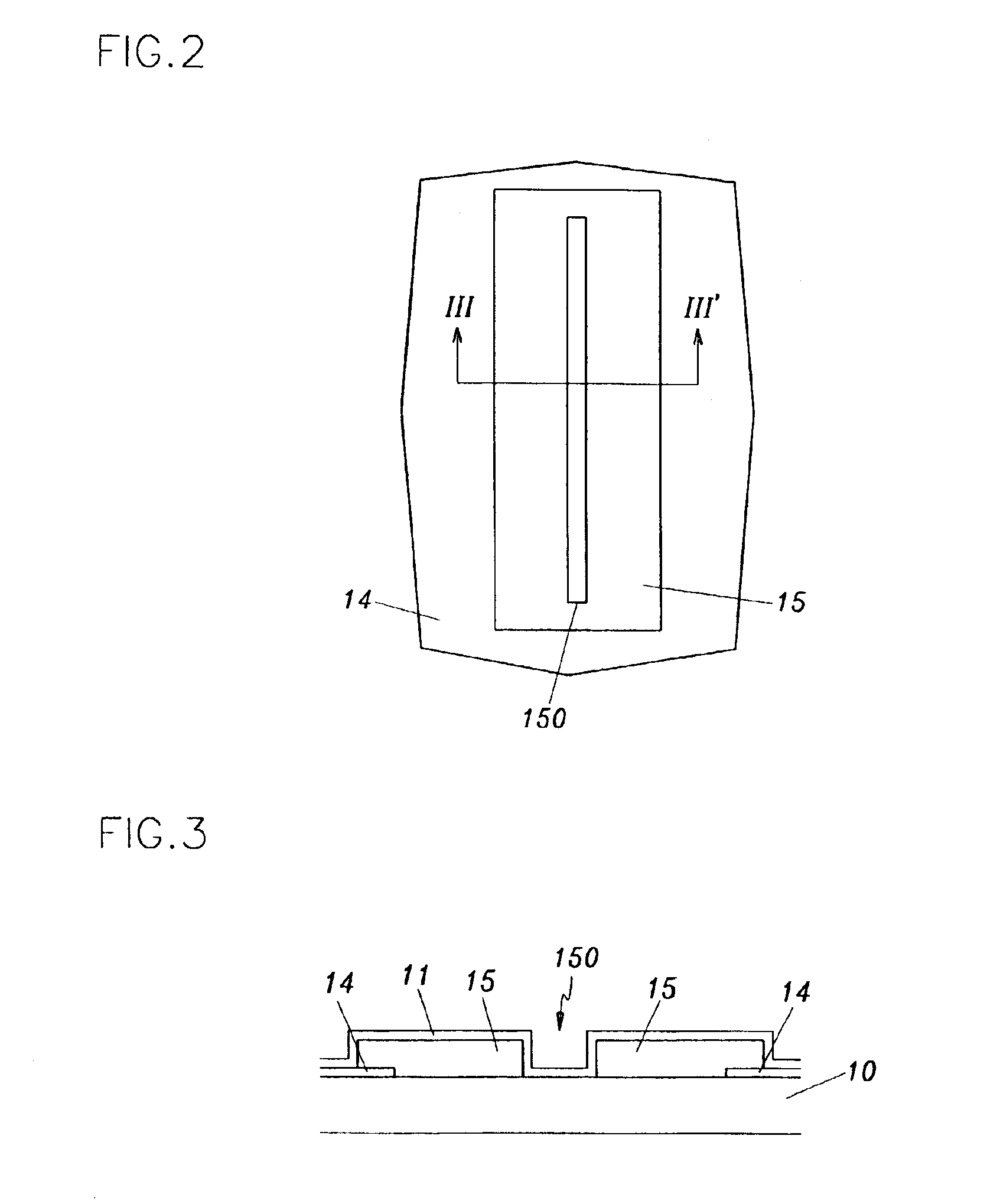

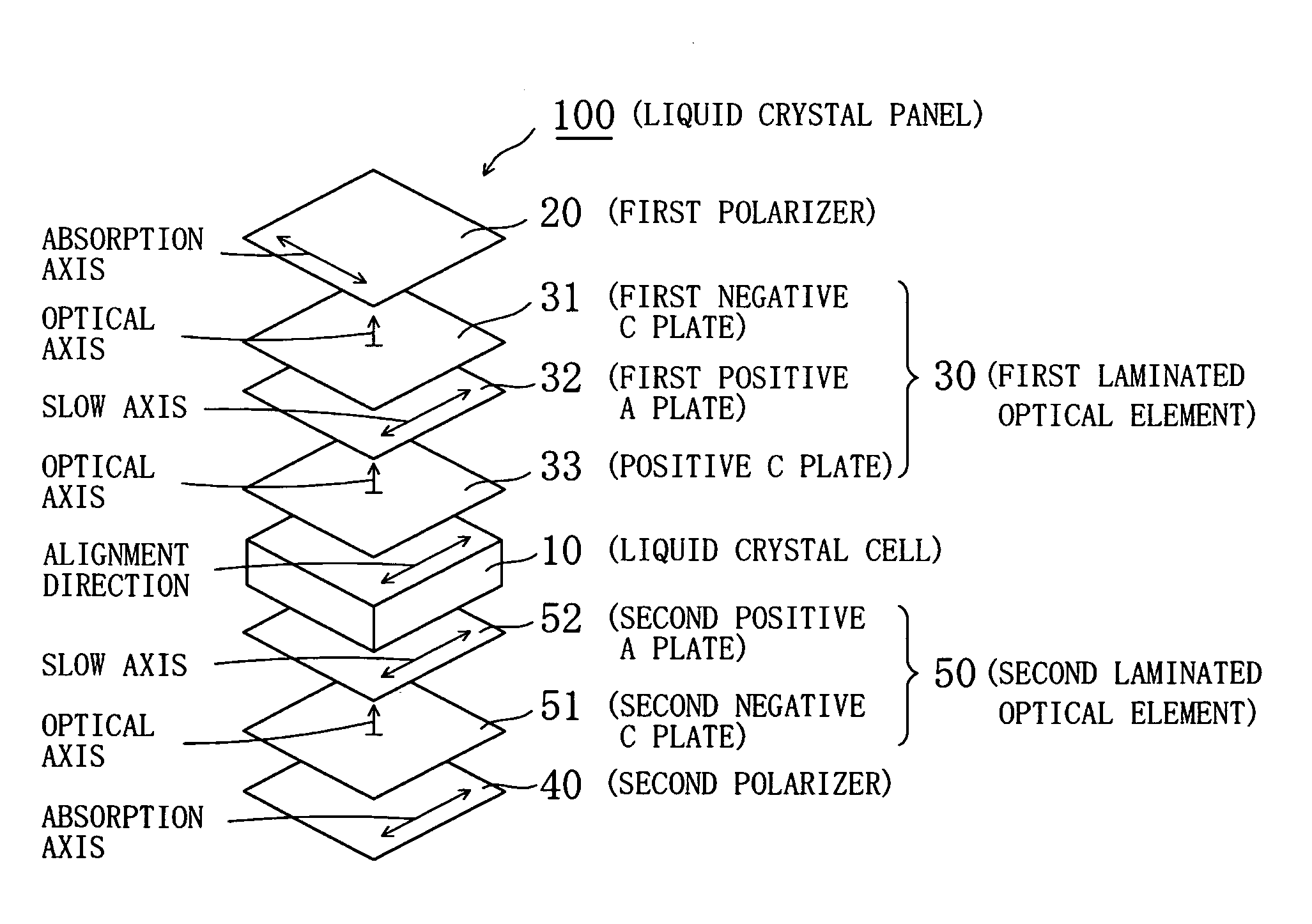

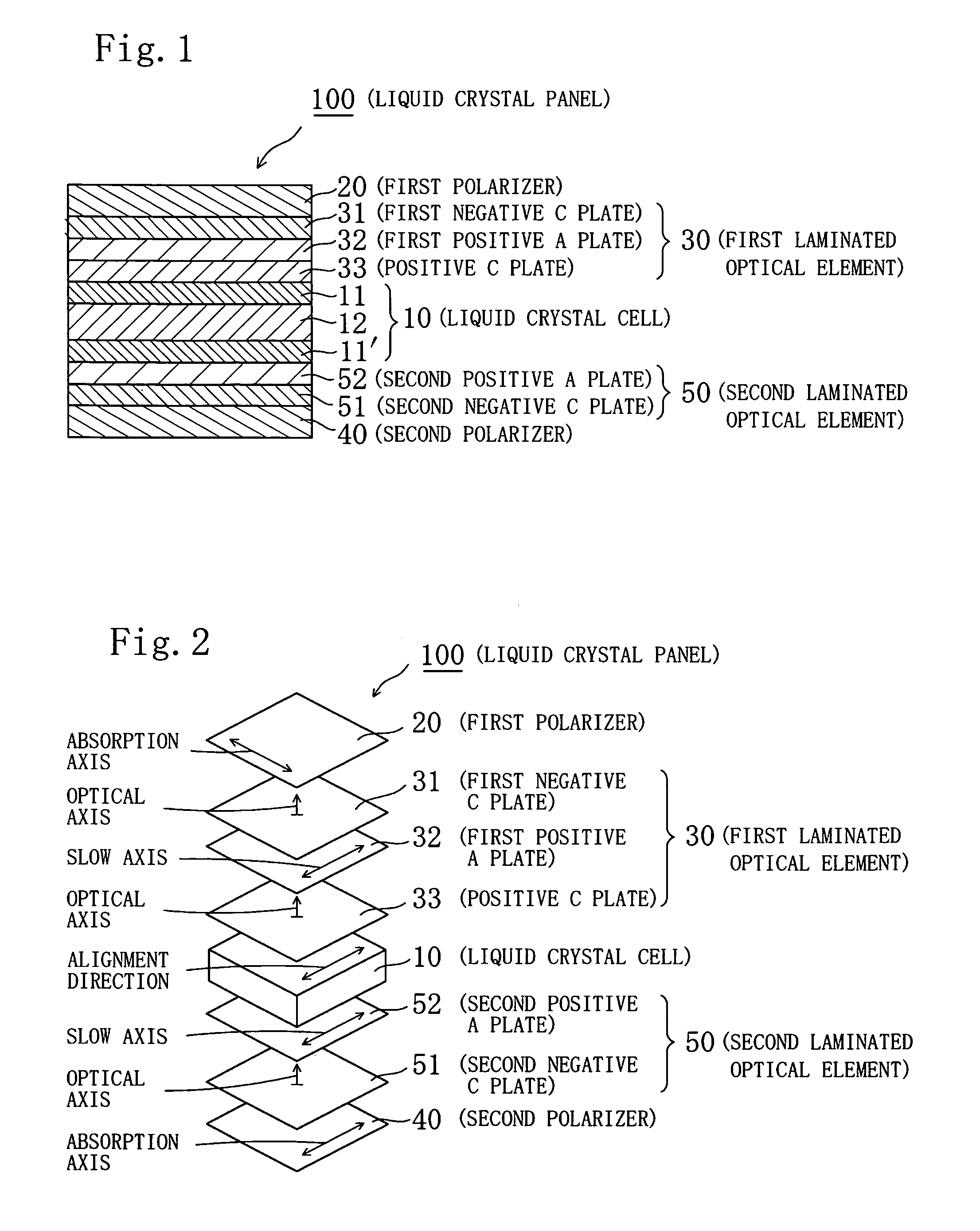

It is an object of the present invention to provide a liquid crystal panel, a liquid television and a liquid crystal display apparatus each having significantly reduced light leak and coloring in black display, a high contrast ratio in an oblique direction and a small color shift in an oblique direction. A liquid crystal panel according to the present invention includes: a liquid crystal cell including a liquid crystal layer containing nematic liquid crystals in homogeneous alignment in an absence of an electric field; a first polarizer arranged on a viewer side of the liquid crystal cell; a first laminated optical element arranged between the liquid crystal cell and the first polarizer; a second polarizer arranged on a backlight side of the liquid crystal cell; and a second laminated optical element arranged between the liquid crystal cell and the second polarizer.

Owner:NITTO DENKO CORP

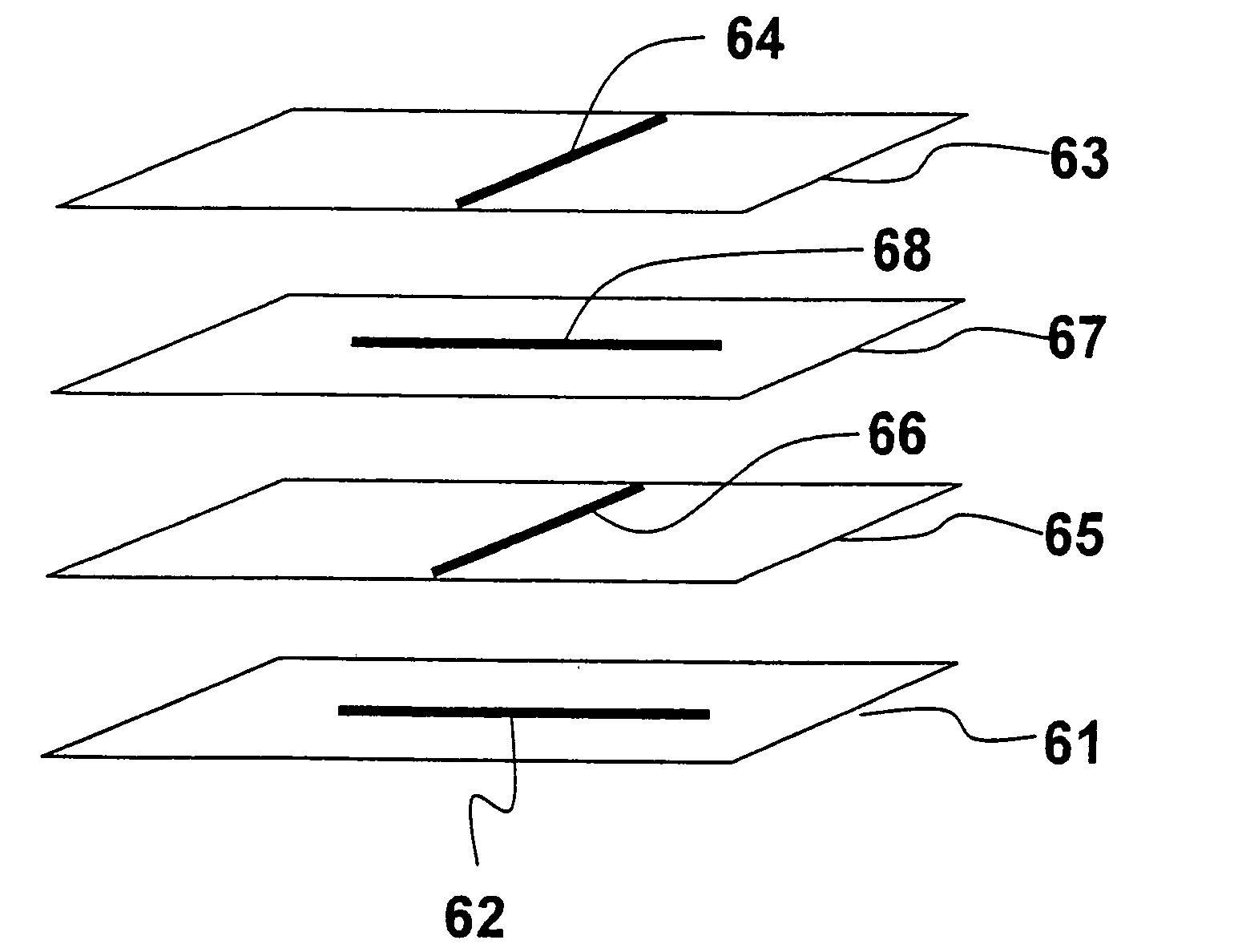

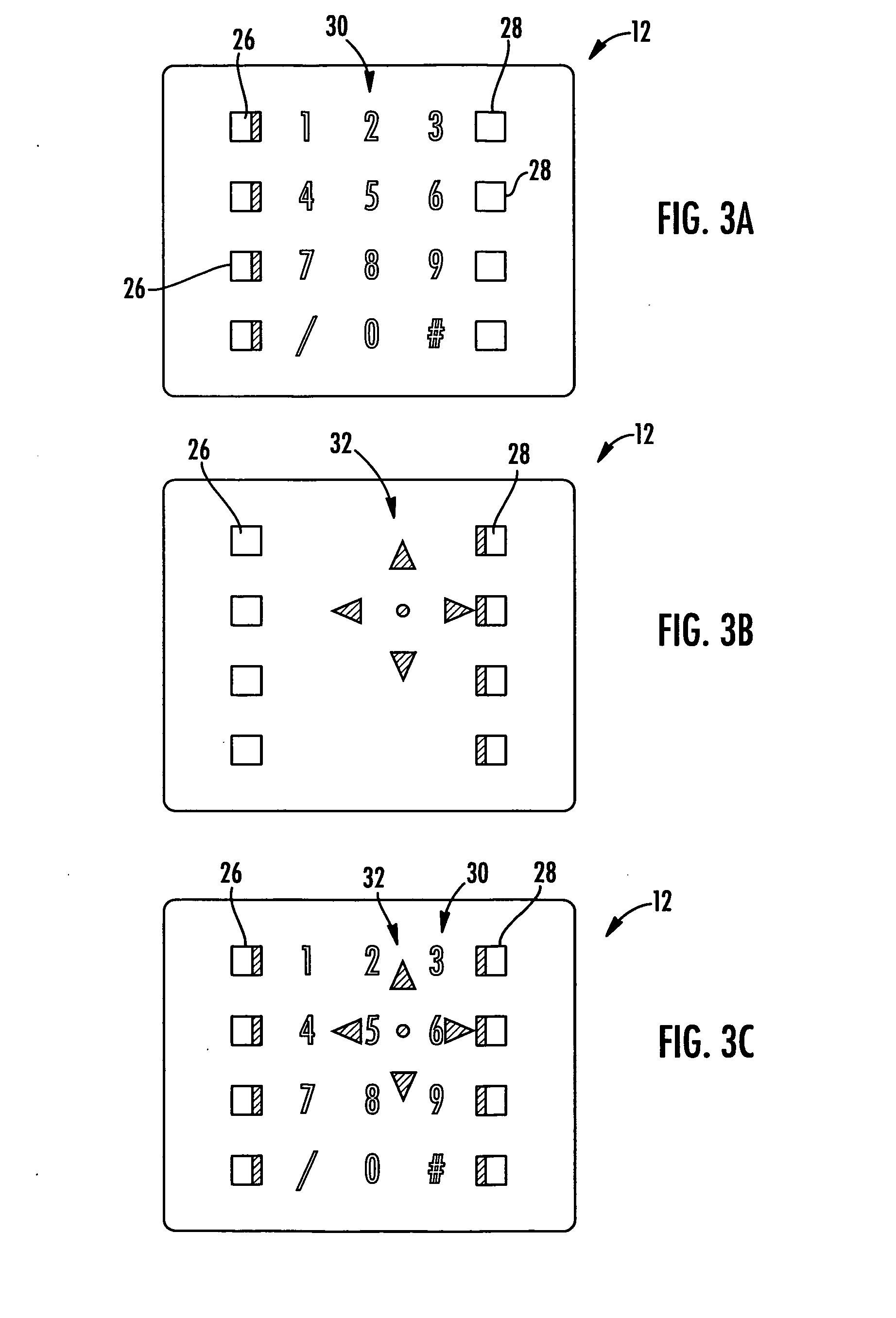

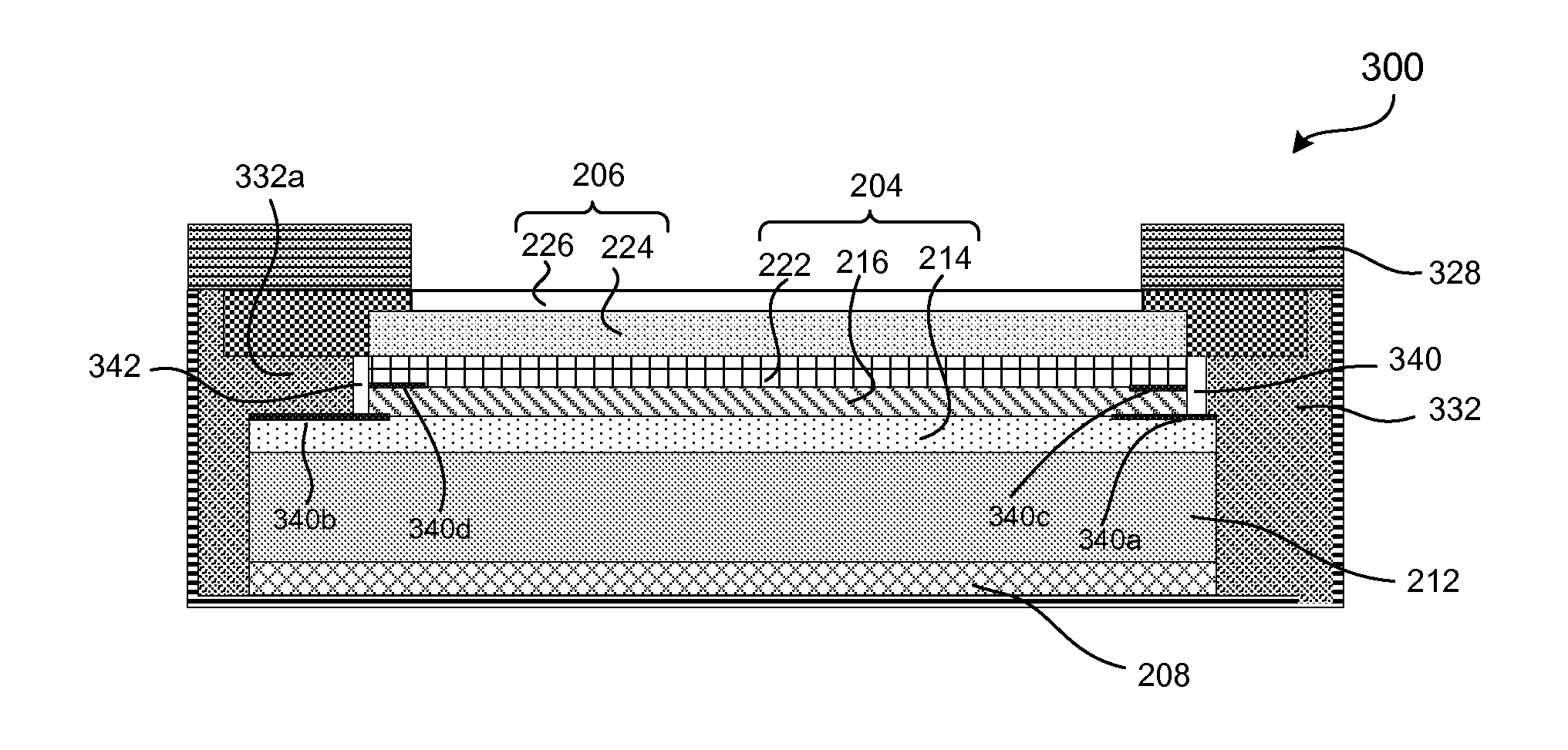

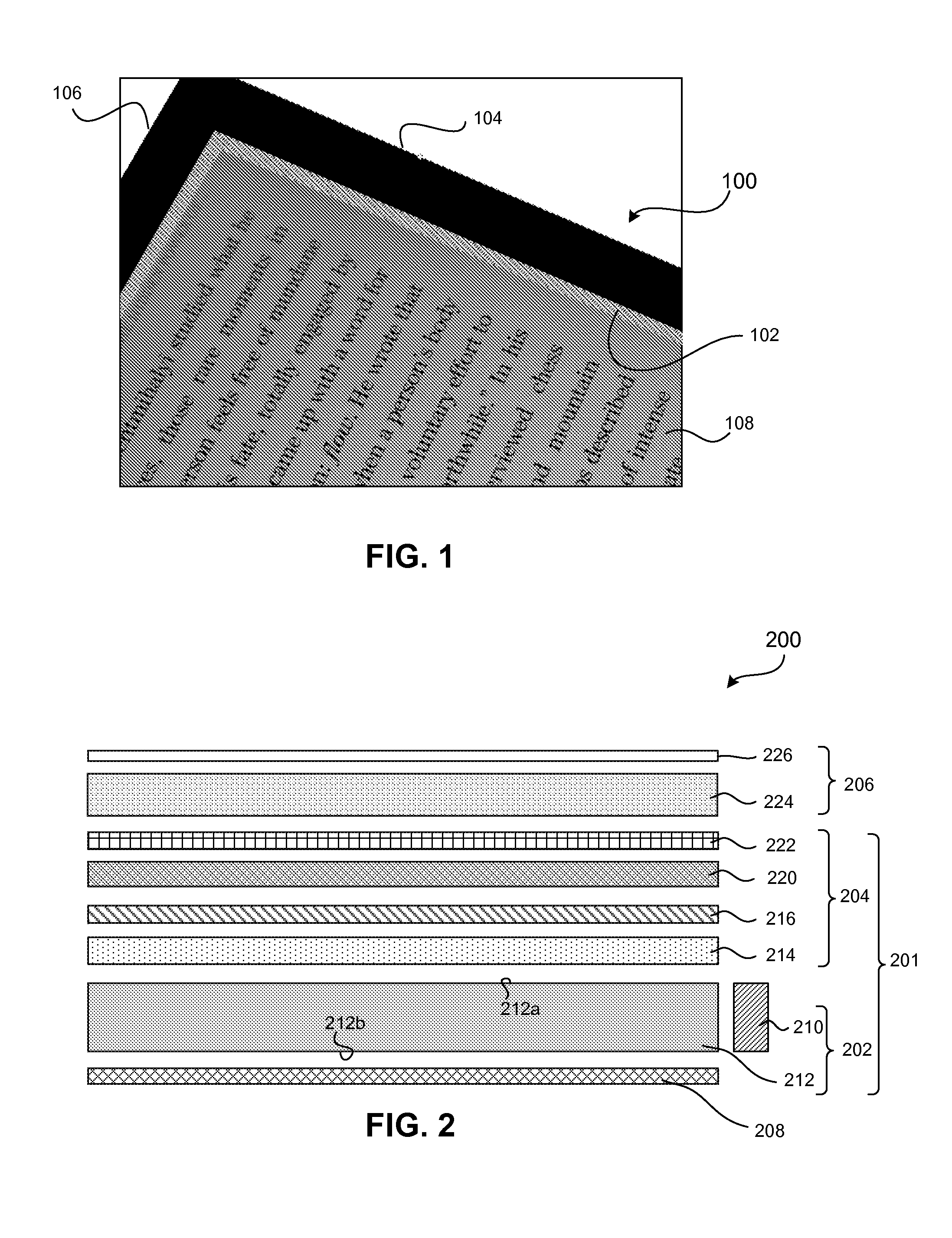

Light guide display systems and related methods, systems, and computer program products

A light guide display system includes a display and a first light guide adjacent the display and having transmissive and nontranasmissive regions. The transmissive regions are configured to transmit light in a first pattern from the first light guide to the display. A second light guide is adjacent the first light guide opposite the display. The second light guide has transmissive and nontransmissive regions, and the transmissive regions of the second light guide are configured to transmit light from the second light guide through the first light guide and to the display in a second pattern.

Owner:SONY ERICSSON MOBILE COMM AB

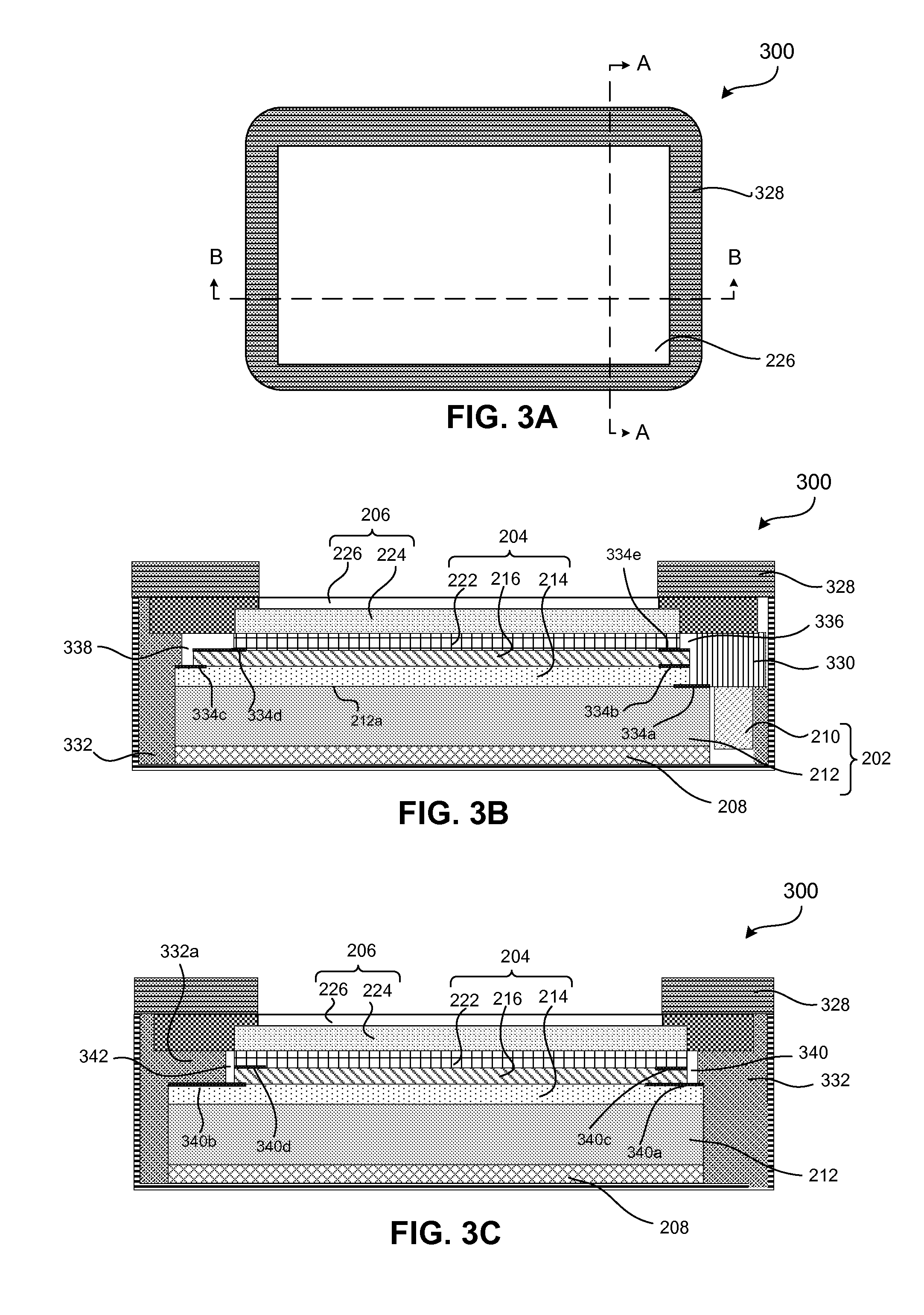

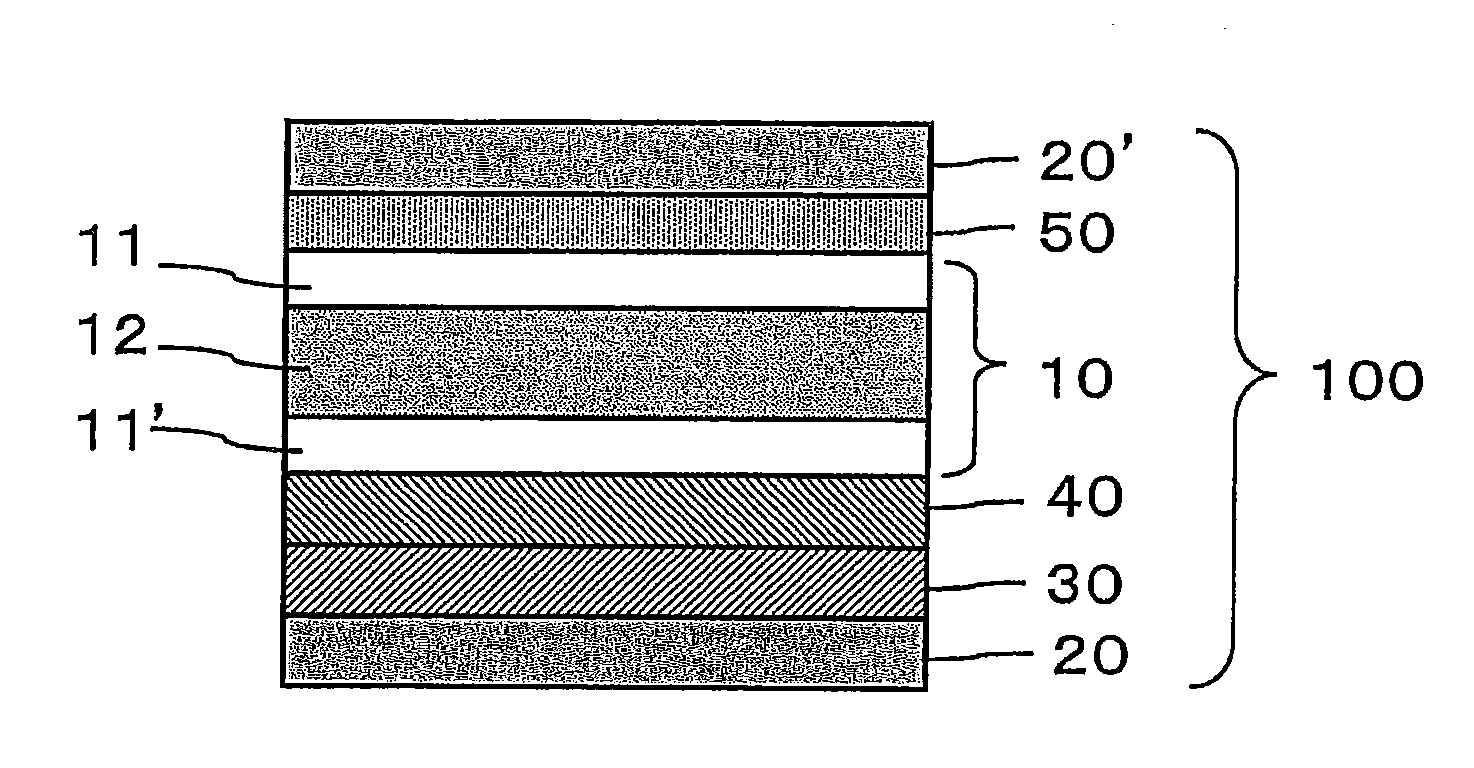

Backlight unit for display devices

ActiveUS20150124195A1Reduce optical leakageReduce light leakageMechanical apparatusPlanar/plate-like light guidesQuantum dotOptical processing

Embodiments of a display device and a method of reducing optical leakage from a backlight unit of a display device are described. The display device includes a backlight unit, an image generating unit coupled to the backlight unit and a blocking structure. The backlight unit is configured to transit light to the image generating unit and the blocking structure is configured to prevent the light from reaching the image generating unit without passing through the optical processing unit. The backlight unit includes a light source unit and an optical processing unit having a quantum dot film coupled to the light source unit. The method of reducing optical leakage from the backlight unit of the display device includes providing a first blocking structure to a portion of the light source unit and providing a second blocking structure to a portion of the optical processing unit.

Owner:NANOSYS INC

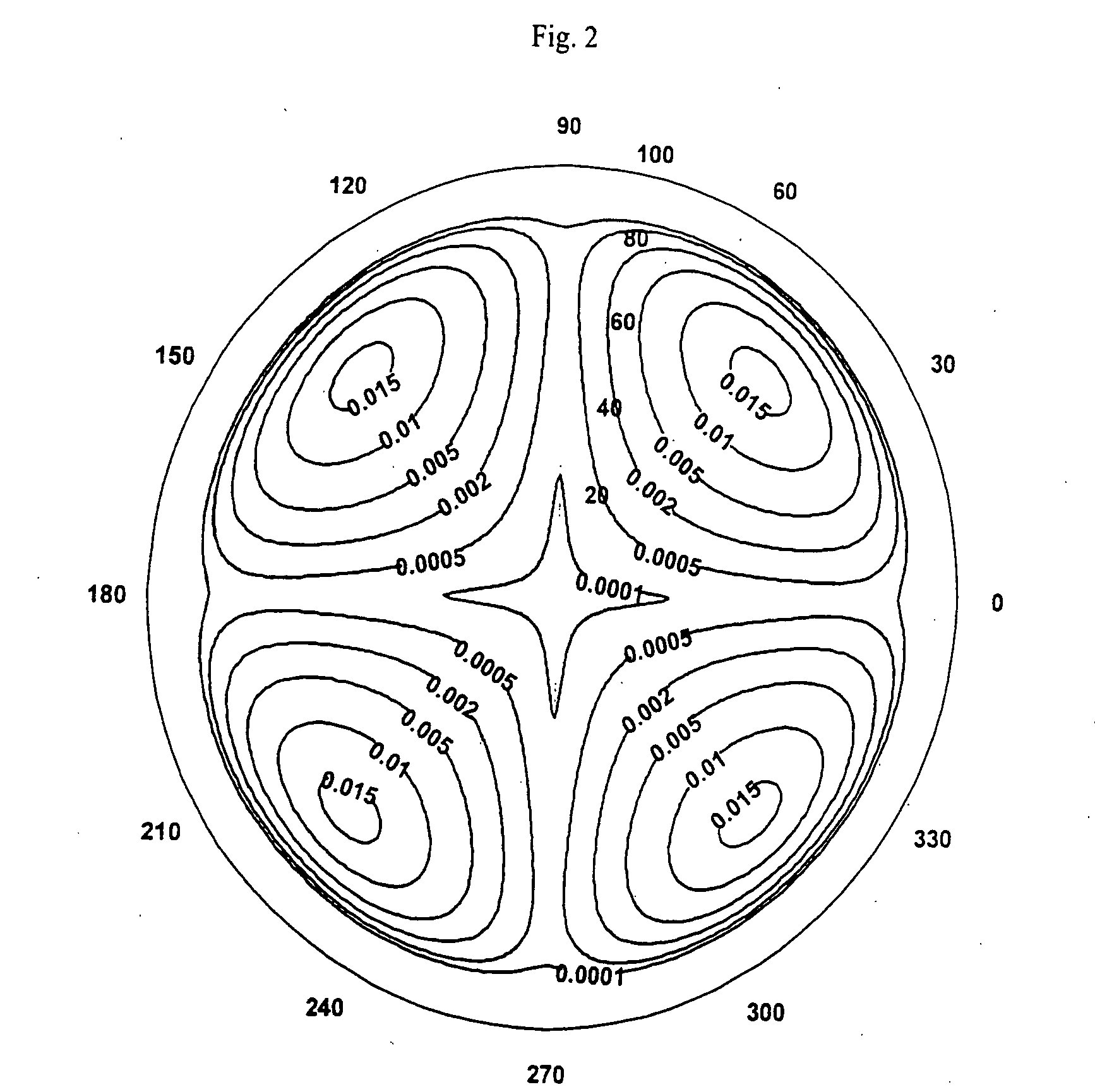

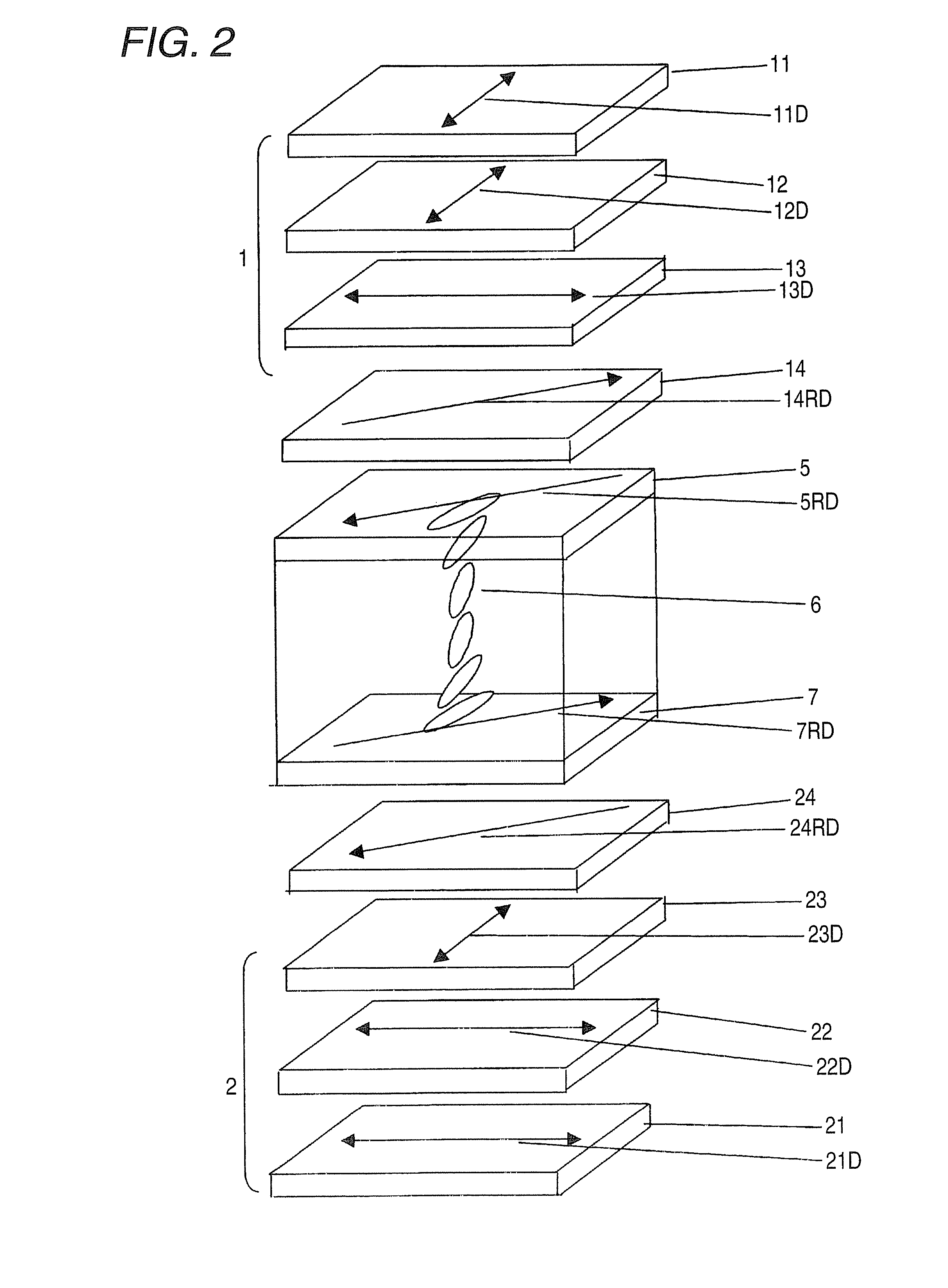

Liquid crystal panel and liquid crystal display

ActiveUS20100309414A1Reduce light leakageIncrease contrastNon-linear opticsOptical elementsPolarizerElectric field

The invention provides a liquid crystal panel and a liquid crystal display device, which has suppressed light leakage at an angle of 45 degrees to an absorption axis of a polarizing plate, a low black-state brightness in an oblique direction and an improved contrast. The liquid crystal panel comprises a liquid crystal cell including a liquid crystal layer containing liquid crystal molecules that is oriented in homogeneous alignment when no electric field is applied thereto, a first polarizer placed on one side of the liquid crystal cell, a second polarizer placed on another side of the liquid crystal cell, a first anisotropic optical element placed between the liquid crystal cell and the first polarizer and satisfying nx1>ny1>nz1, and a second anisotropic optical element placed between the first anisotropic optical element and the liquid crystal cell and satisfying nz2>nx2>ny2, wherein the slow axis of the first anisotropic optical element is parallel to the slow axis of the second anisotropic optical element.

Owner:NITTO DENKO CORP

Liquid crystal display element, and use of phase difference film used the same for

The present invention provides a liquid crystal display device of VA mode having decreased leakage of light over a wide range and giving a clear and almost achromatic black display by using a retardation film A having smaller retardation with shorter wavelength in combination with a retardation film C having larger retardation with shorter wavelength. Accordingly, a high-quality liquid crystal display device having excellent picture quality can be produced by the present invention.

Owner:TEIJIN LTD

Polarization plate, liquid crystal display device and protective film

ActiveUS20090257003A1Sufficient visibilityExcellent abrasion resistanceAdhesive processesMirrorsTectorial membraneVisibility

Provided are a polarization plate which has a high mechanical strength, which does not impair a visibility even under a high temperature and high humidity, which is excellent in flexibility and abrasion resistance, and which reduces a visible disturbance such as color unevenness due to a size change, as well as a liquid crystal display device using the polarization plate. A film composed of a plurality of layers composed mainly of thermoplastic resins is used as a first protection film used for a visible side of the polarization plate, and at least one surface layer of this first protection film is composed mainly of an acrylic resin. Furthermore, a second protection film having a specific property is disposed at a side of a liquid crystal cell.

Owner:ZEON CORP

Display device

InactiveUS20070177071A1Low costReduce light leakagePolarising elementsNon-linear opticsPolarizerHigh contrast

To provide a display device having a high contrast ratio by a simple and easy method and to manufacture a high-performance display device at low cost, in a display device having a display element between a pair of light-transmitting substrates, layers each including a polarizer having different wavelength distribution of extinction coefficient from each other with respect to the absorption axes are stacked and provided on an outer side of the light-transmitting substrates. Further, a retardation plate may be provided between the stacked polarizers.

Owner:SEMICON ENERGY LAB CO LTD

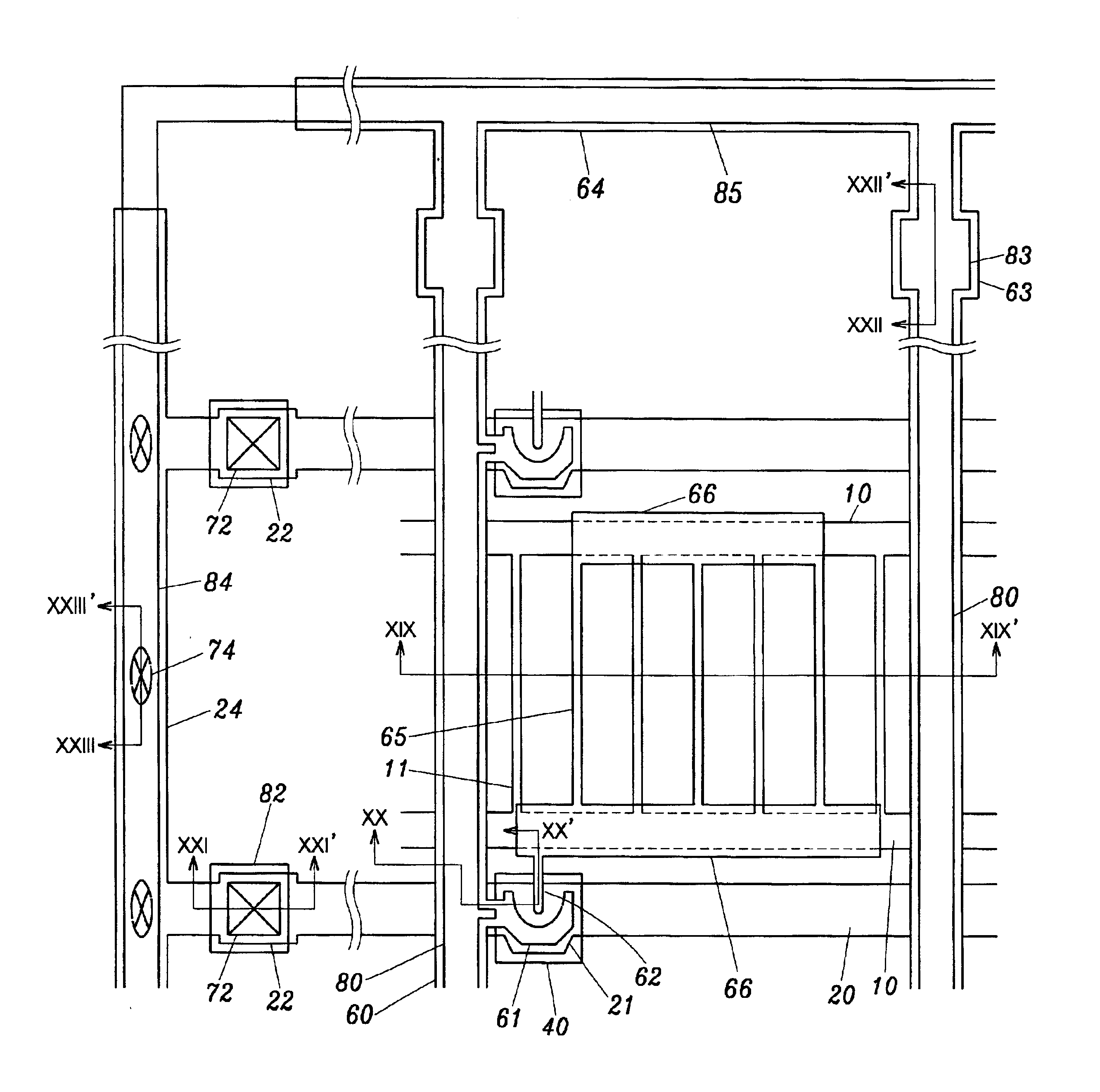

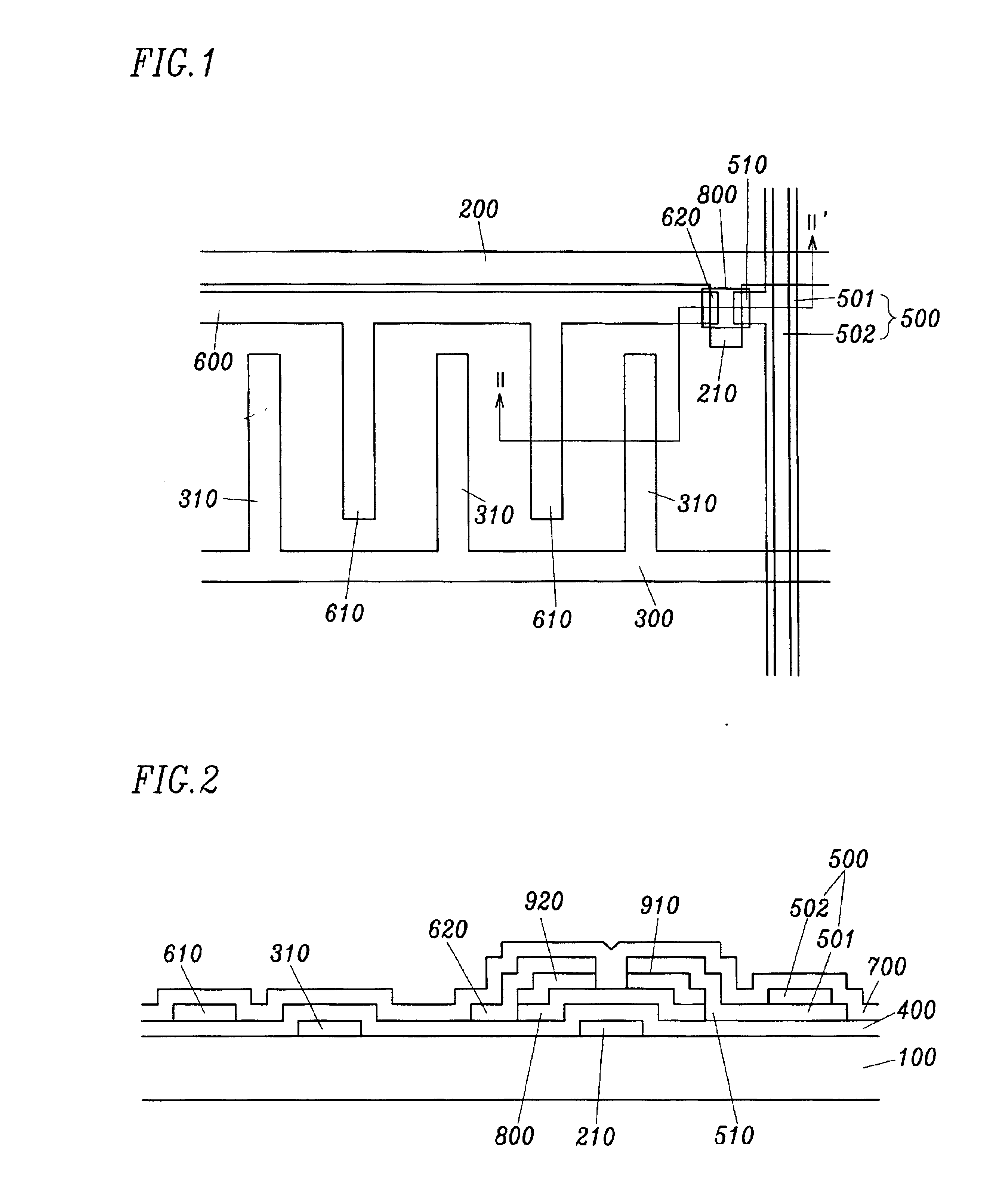

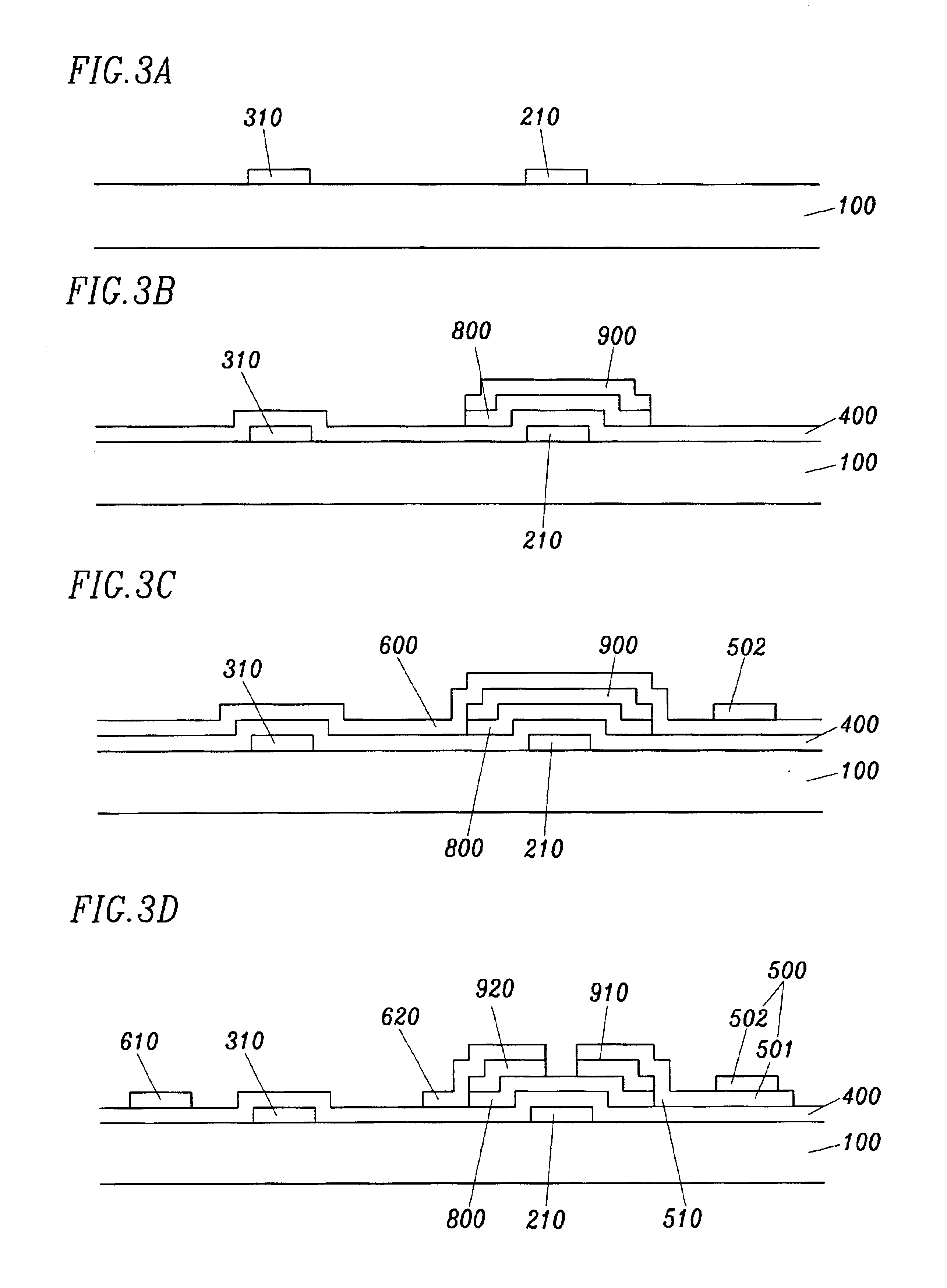

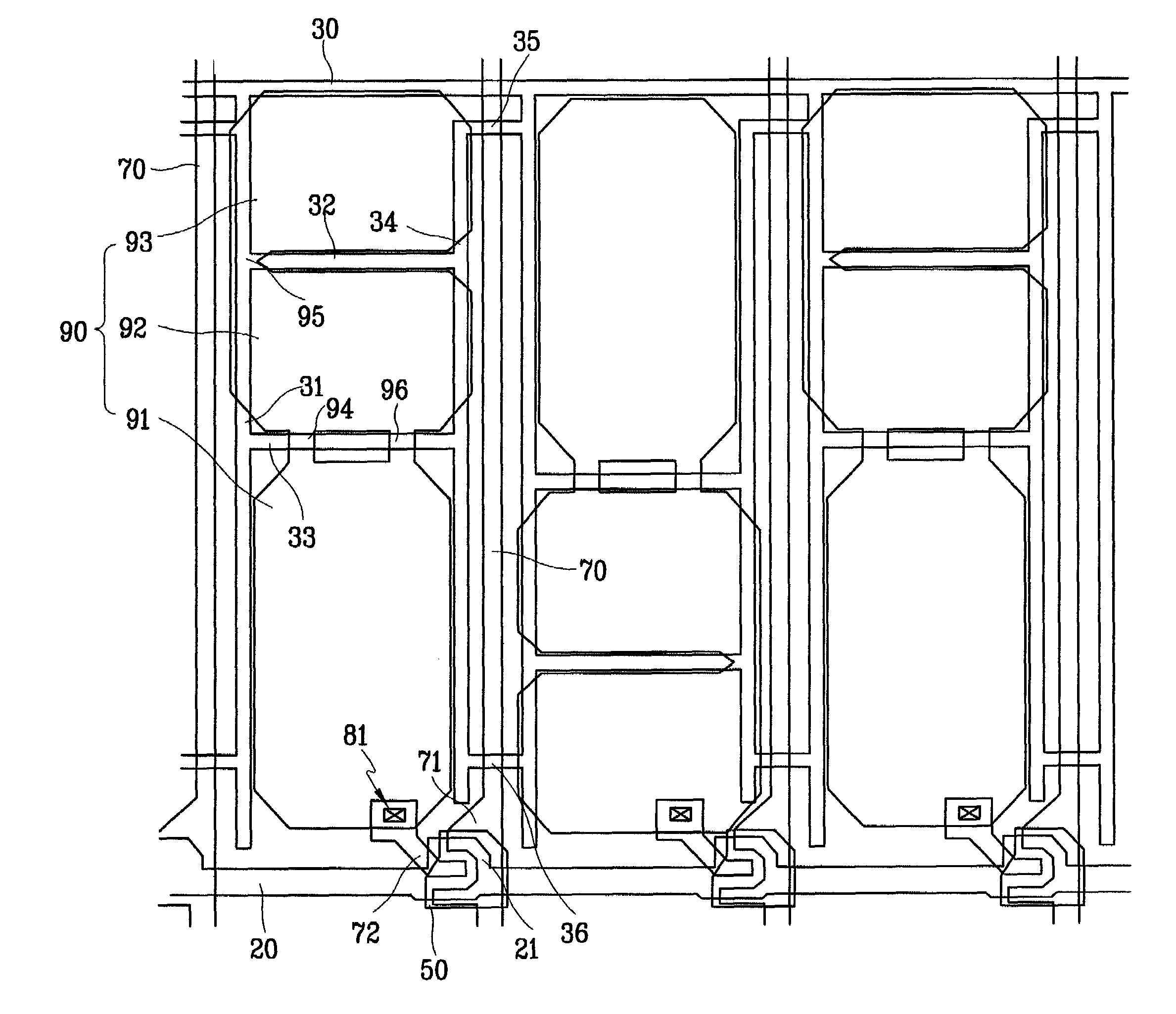

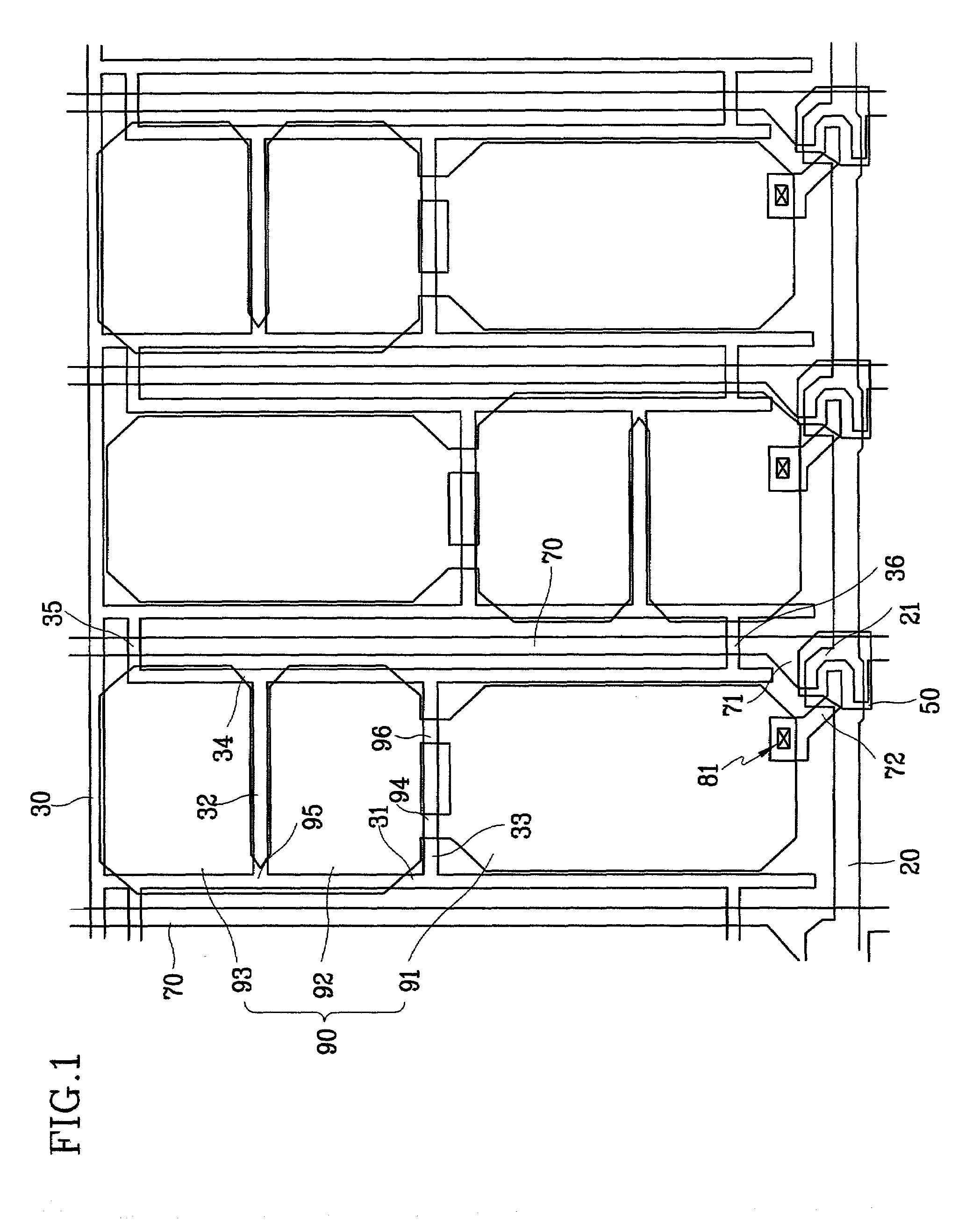

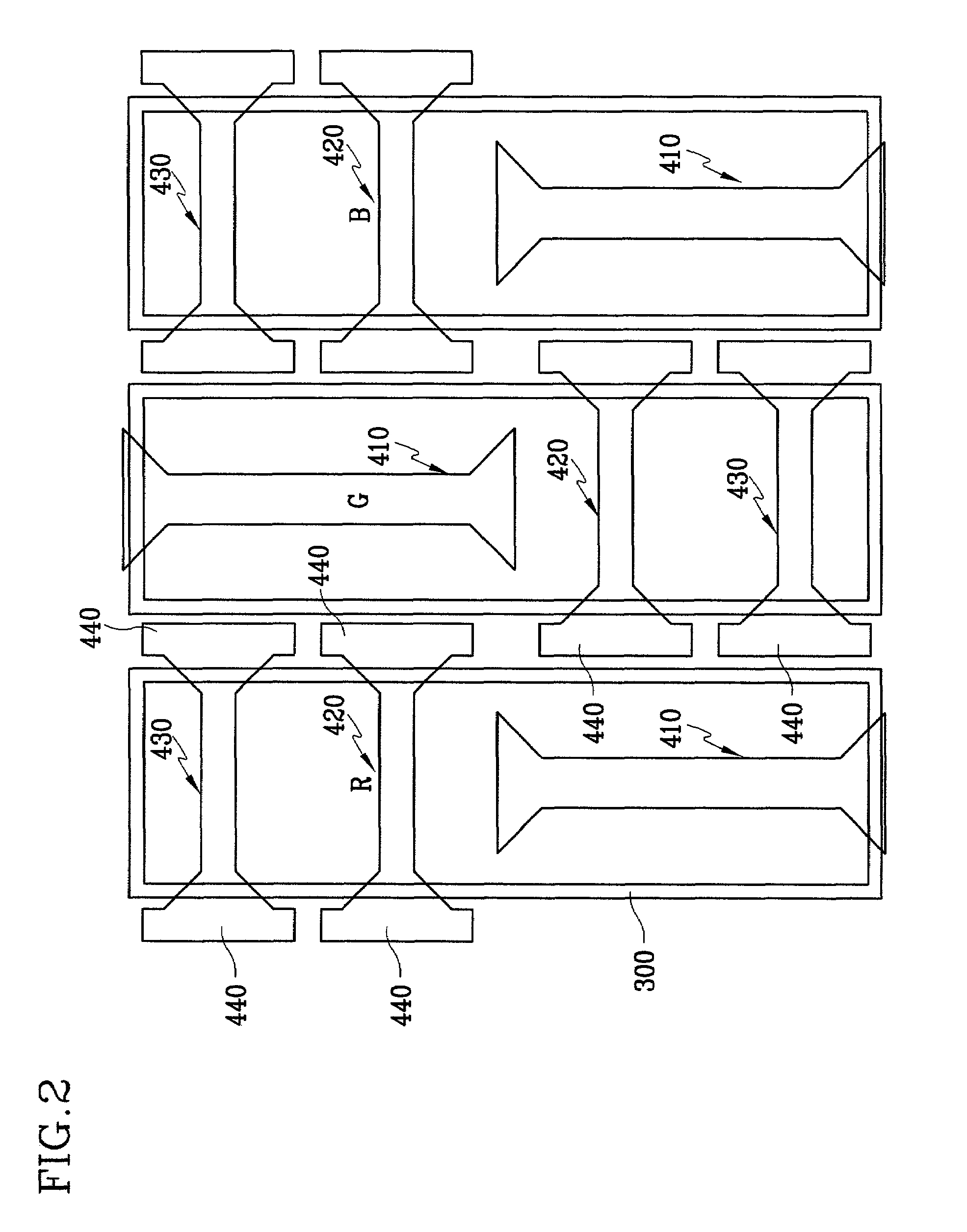

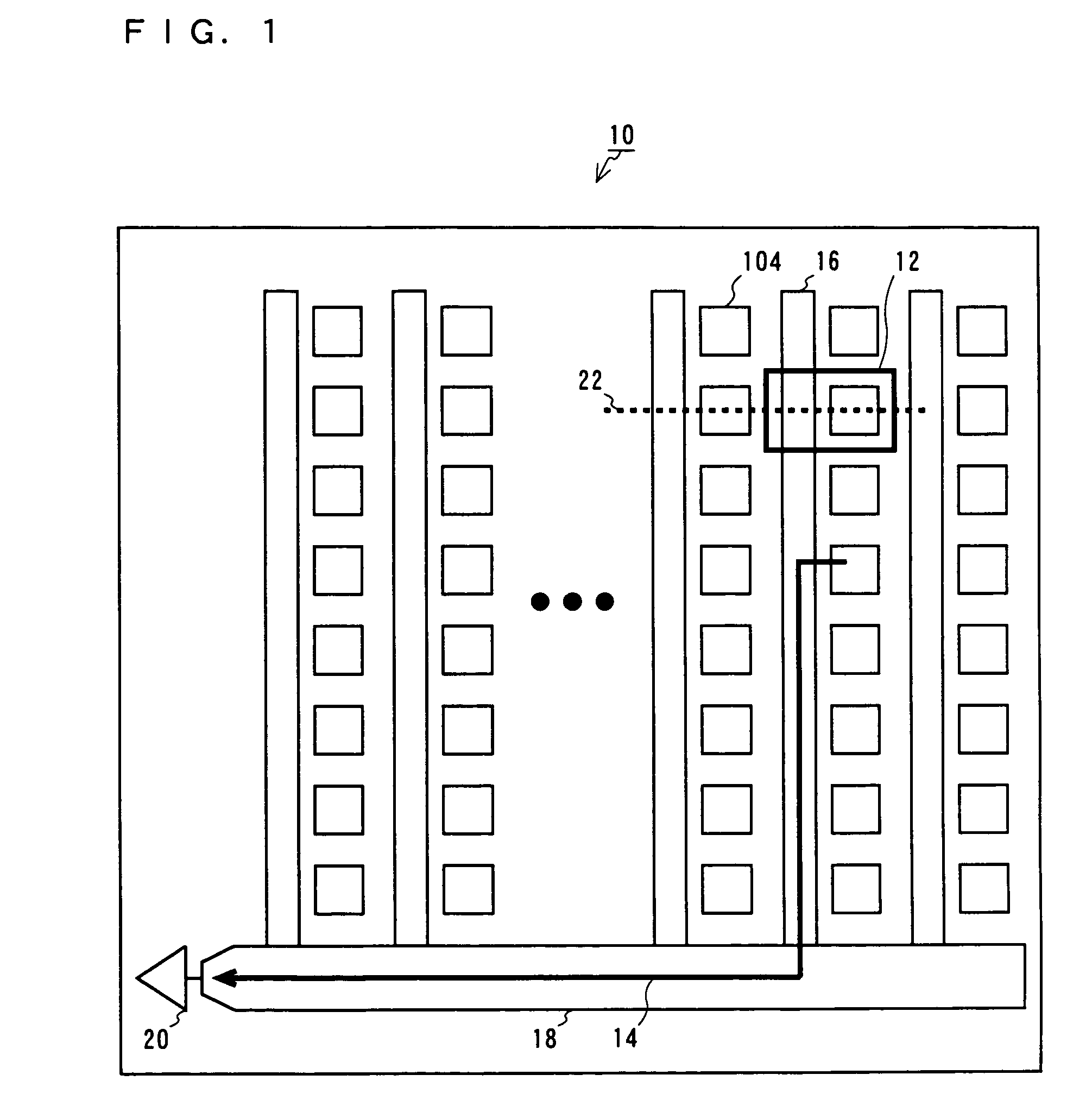

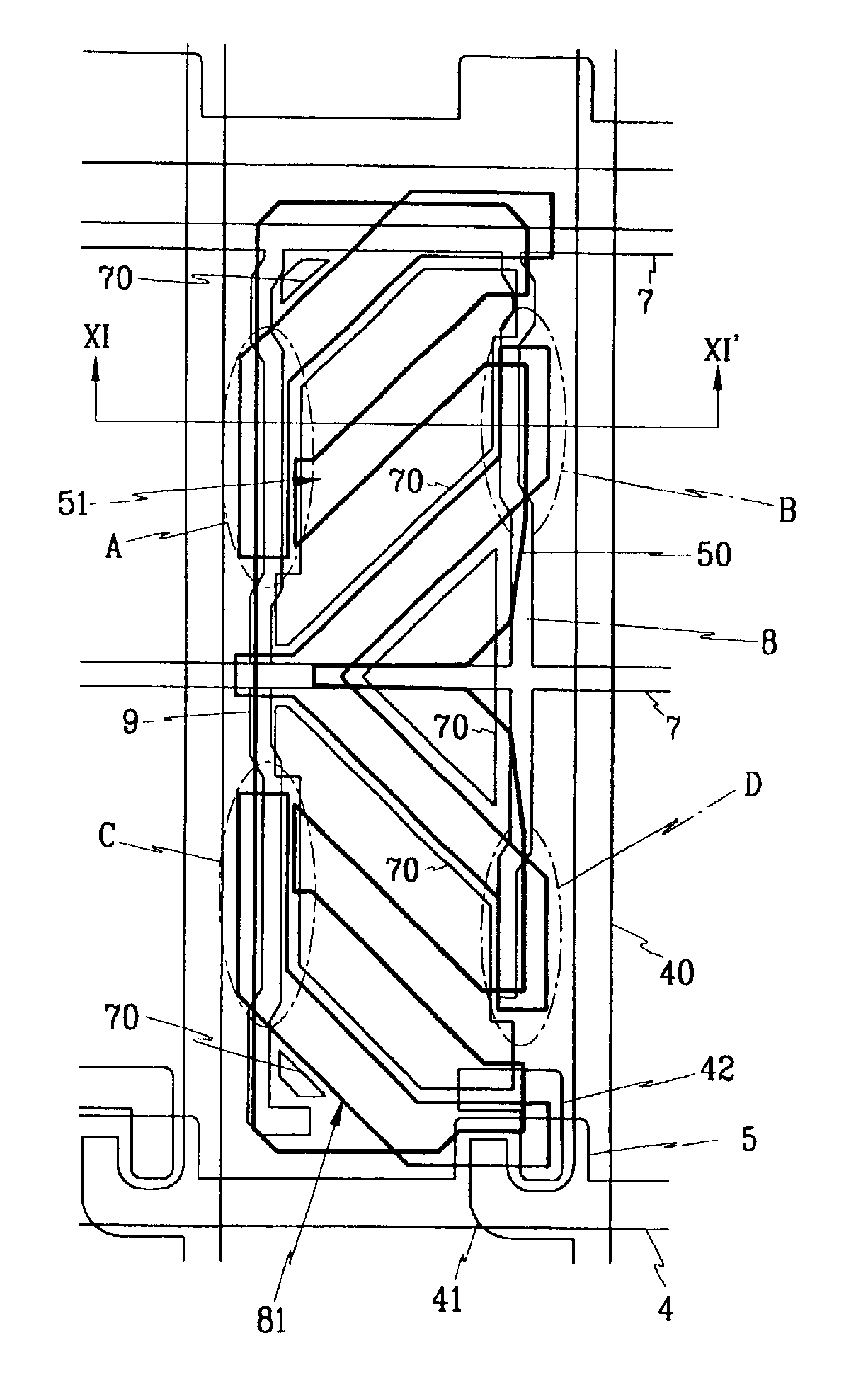

Liquid crystal display (LCD) devices having redundant patterns

InactiveUS6856372B2Reduce light leakageAvoid damageNon-linear opticsElectricityLiquid-crystal display

A gate wire including a gate line, a gate electrode, a gate pad and a gate line connector and a common signal wire are formed on a substrate, and a gate insulating layer is formed over the gate wire and the common signal wire. A semiconductor layer and an ohmic contact layer are sequentially formed on the gate insulating layer, a data wire including a source and a drain electrode, a data line, a data pad and a data line connector and a pixel electrode are formed thereon. The thickness of the data wire and the pixel electrode is equal to or less than 500 Å. A passivation layer is formed on the data wire and the pixel electrode, a redundant data wire is formed thereon, and a redundant gate pad and a redundant gate line connector are formed. The redundant data wire is electrically connected to the data wire through the contact holes in the passivation layer, and the redundant gate pad and the redundant gate line connector are electrically connected to the gate pad and the gate line connector respectively through the contact holes in the passivation layer and the gate insulating layer. The redundant gate line connector and the redundant data line connector are connected to each other to short the gate and the data wires. After an alignment layer is formed and rubbed, the edge of the panel is cut away to remove the gate line connector and the data line connector.

Owner:SAMSUNG ELECTRONICS CO LTD

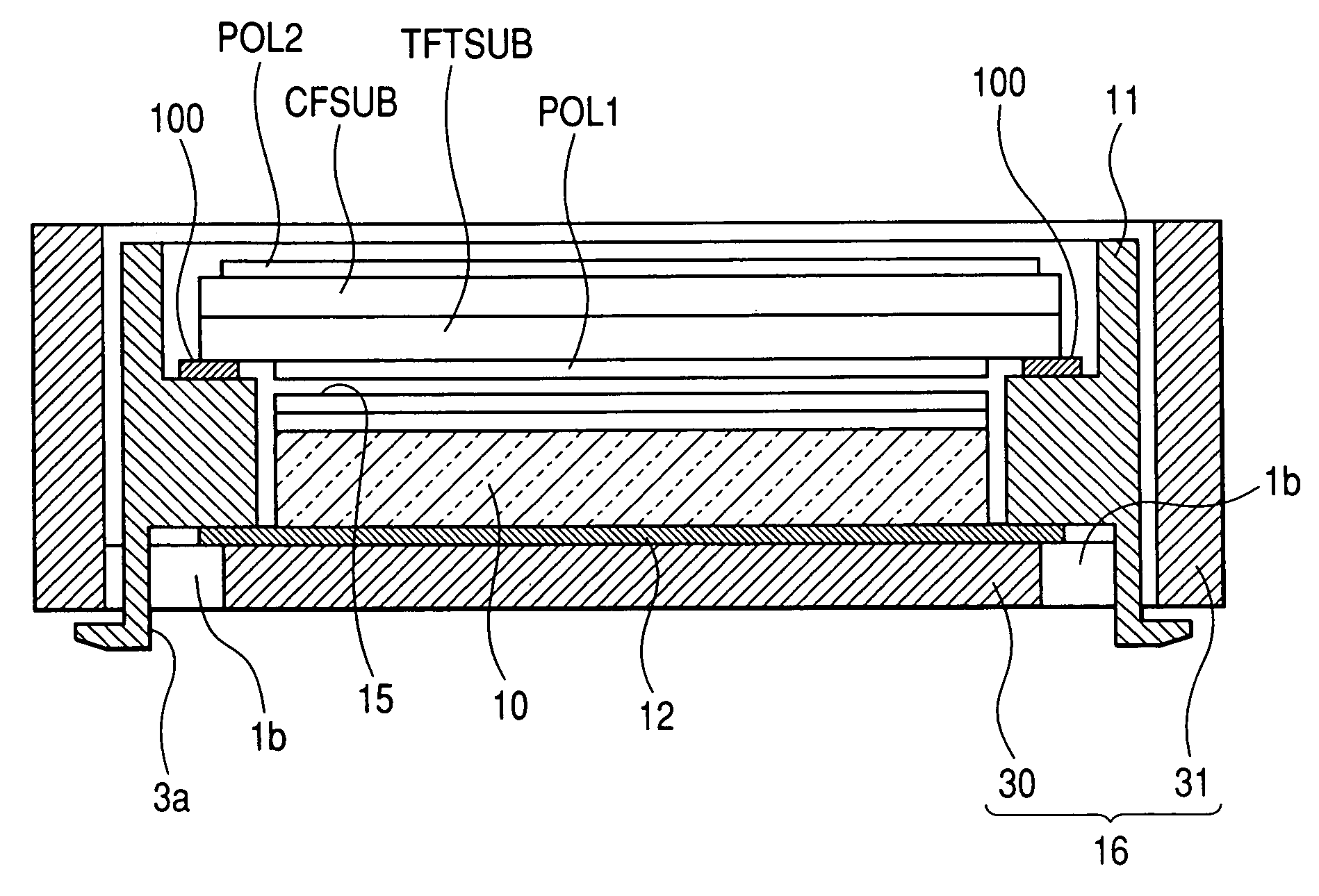

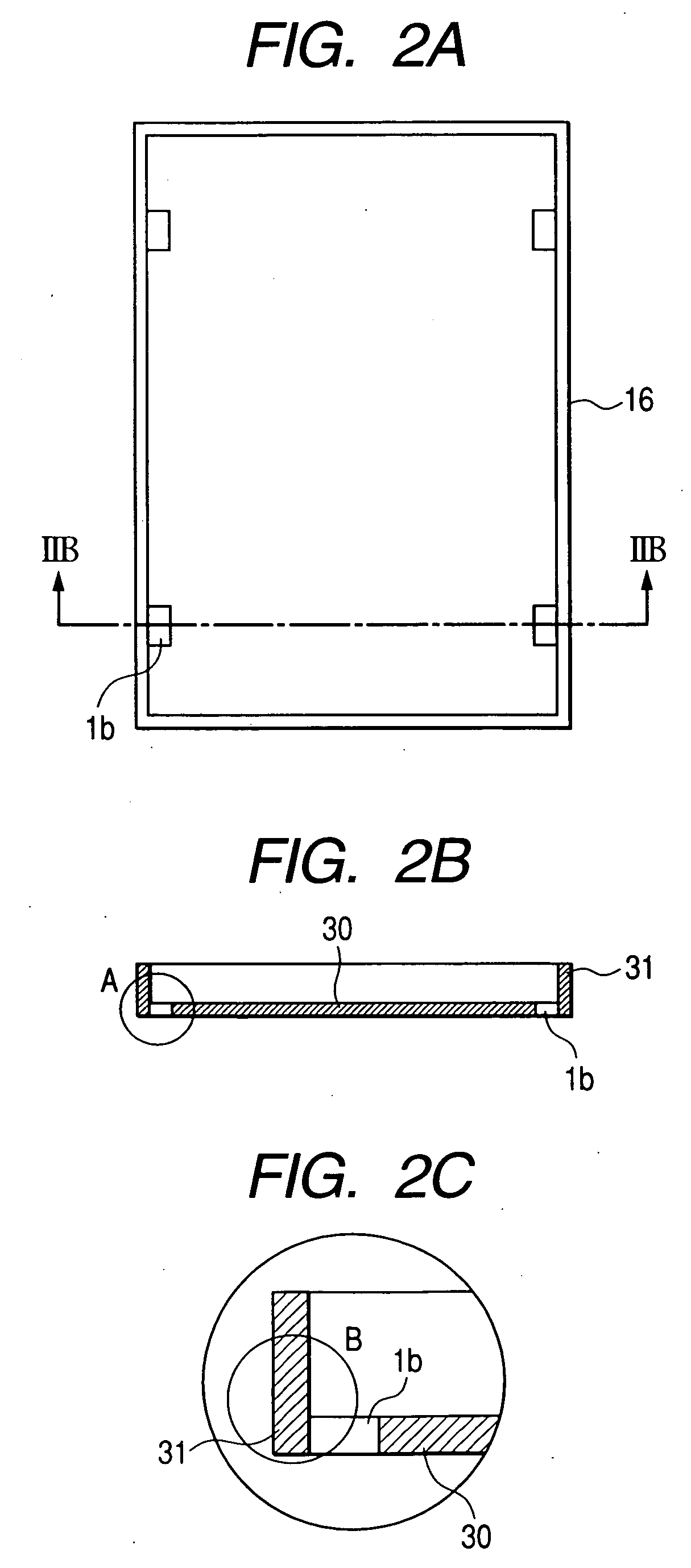

Liquid crystal display device

ActiveUS20070002206A1Reduce light leakageNon-linear opticsReflectorsLiquid-crystal displayLiquid crystal

A liquid crystal display device includes a liquid crystal display panel having liquid crystal material sandwiched between a pair of substrates, optical components disposed behind the liquid crystal display panel, a frame-like mold which houses the liquid crystal display panel and the optical components, and a frame which houses the frame-like mold. The frame includes a bottom portion and a sidewall, and the bottom portion is provided with plural engaging through holes which are formed along the sidewall not to extend into the sidewall. The frame-like mold is provided with plural engaging protrusions which are disposed correspondingly to the engaging holes and protrude downward beyond a lower surface of the frame-like mold. The frame-like mold and the frame are fixed together by inserting each of the engaging protrusions into a corresponding one of the engaging through holes.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Liquid crystal display device

ActiveUS20090322997A1Low contrastReducing normal contrastLiquid crystal compositionsNon-linear opticsIn planeBlue phase liquid crystal

The invention relates to a liquid crystal display device of the present invention has at least a pair of transparent substrates, polymer-stabilized blue phase liquid crystal layer disposed therebetween, and a transparent film having an absolute value |Re| of in-plane retardation Re of 10 nm or smaller in the visible light region, having an absolute value |Rth| of thickness-wise retardation Rth of 30 nm or smaller in the visible light region, having an absolute value |Re(400)−Re(700)| of difference between values of in-plane retardation Re at 400 nm and 700 nm of 10 nm or smaller, and having an absolute value |Rth(400)−Rth(700)| of difference between values of thickness-wise retardation Rth at 400 nm and 700 nm of 35 nm or smaller.

Owner:FUJIFILM CORP

Liquid crystal display

InactiveUS7016006B2Reduce loadImprove image qualityNon-linear opticsCapacitanceLiquid-crystal display

A gate line and a data line are formed on a first panel, a pixel electrode is divided into several small parts by an aperture, and a thin film transistor is formed on a pixel area defined by the intersection thereof. A common electrode having a domain dividing aperture and a data line aperture is formed on a second panel disposed opposite to the first substrate. Removing the common electrode from an upper side of the data line by forming the data line aperture as above can result in decreasing load of the data line, reducing a variation amount of liquid crystal capacitance, decreasing light leakage of due to side cross talk, and increasing an aperture ratio.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

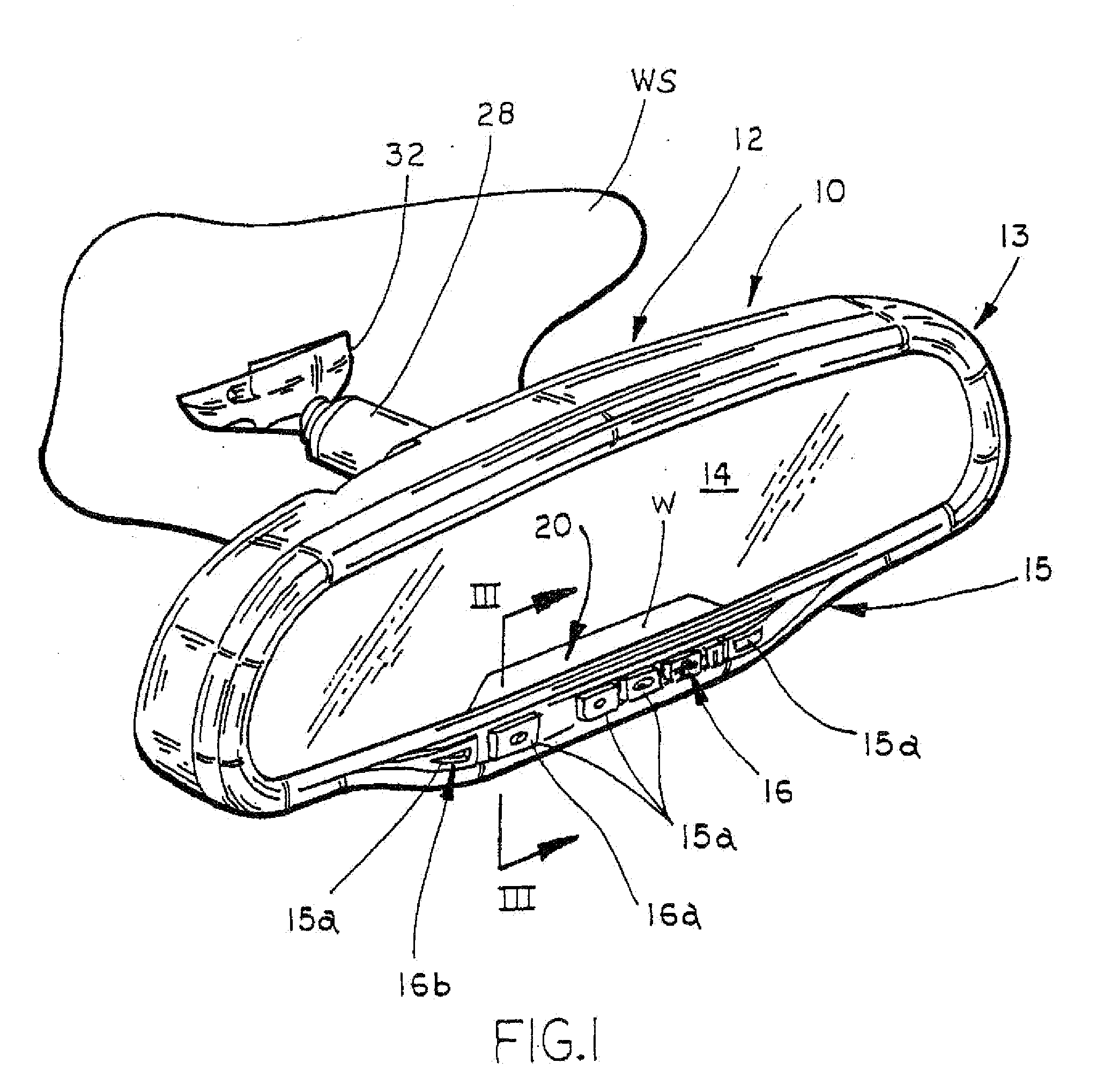

Information display system for a vehicle

InactiveUS20090141331A1Easy to install and arrangeReduce light leakageMirrorsElectrical apparatusInformation display systemsEngineering

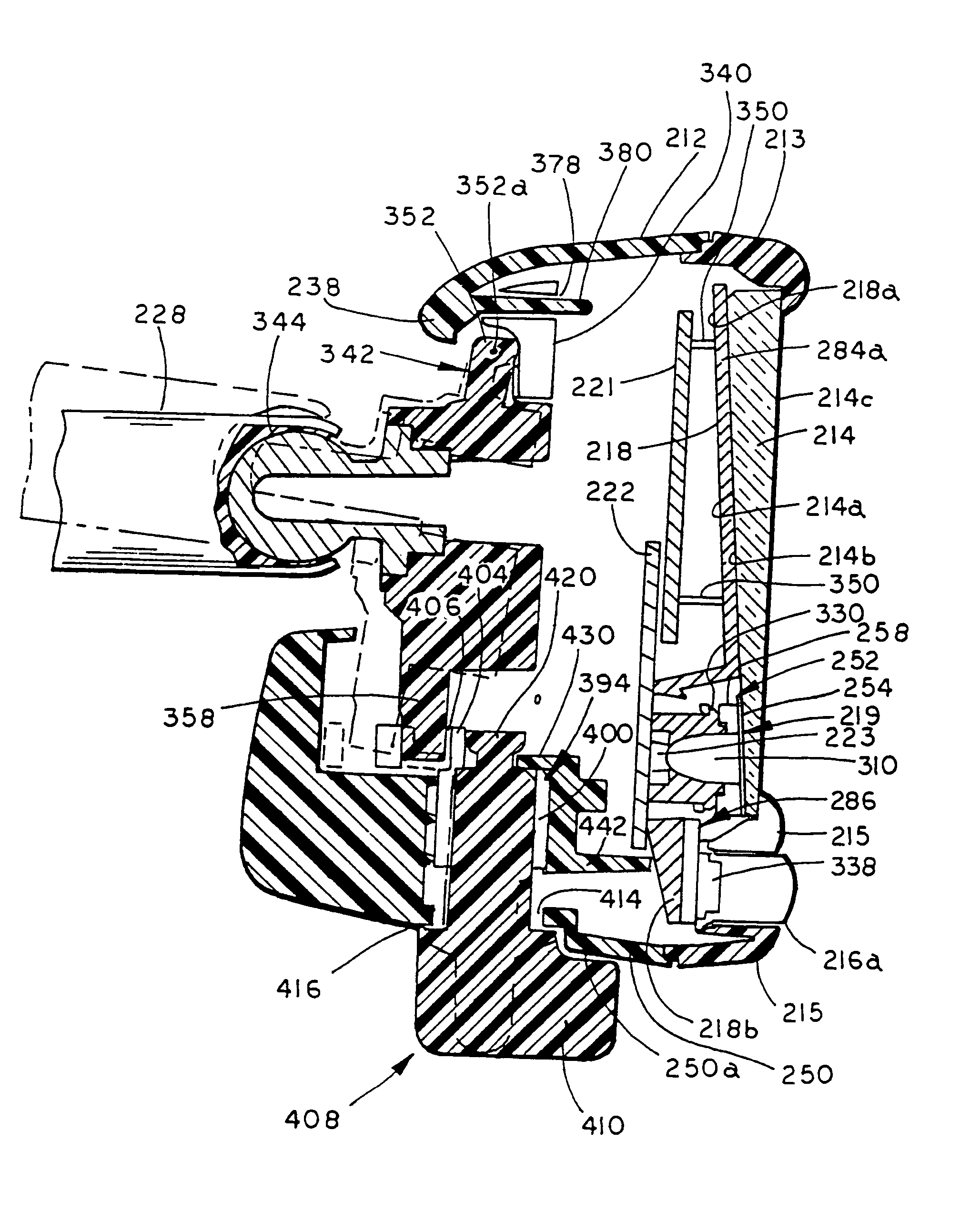

An interior rearview mirror assembly for vehicles includes a mirror case having a reflective element and a carrier positioned in the mirror case. The mirror case is adapted to mount to a vehicle. The reflective element includes a substrate, with a reflective coating on one side of the substrate, and a window therethrough. The carrier has a display element for displaying one or more indicia through the window to define a display area on the reflective element. The carrier comprises a plate member, with a first portion and a second portion offset rearwardly from the reflective element and from the first portion. The second portion includes the display element. Preferably, the interior rearview mirror assembly further includes at least one light assembly for displaying the indicia through said window so that it is visible to an occupant of the vehicle.

Owner:DONNELLY CORP

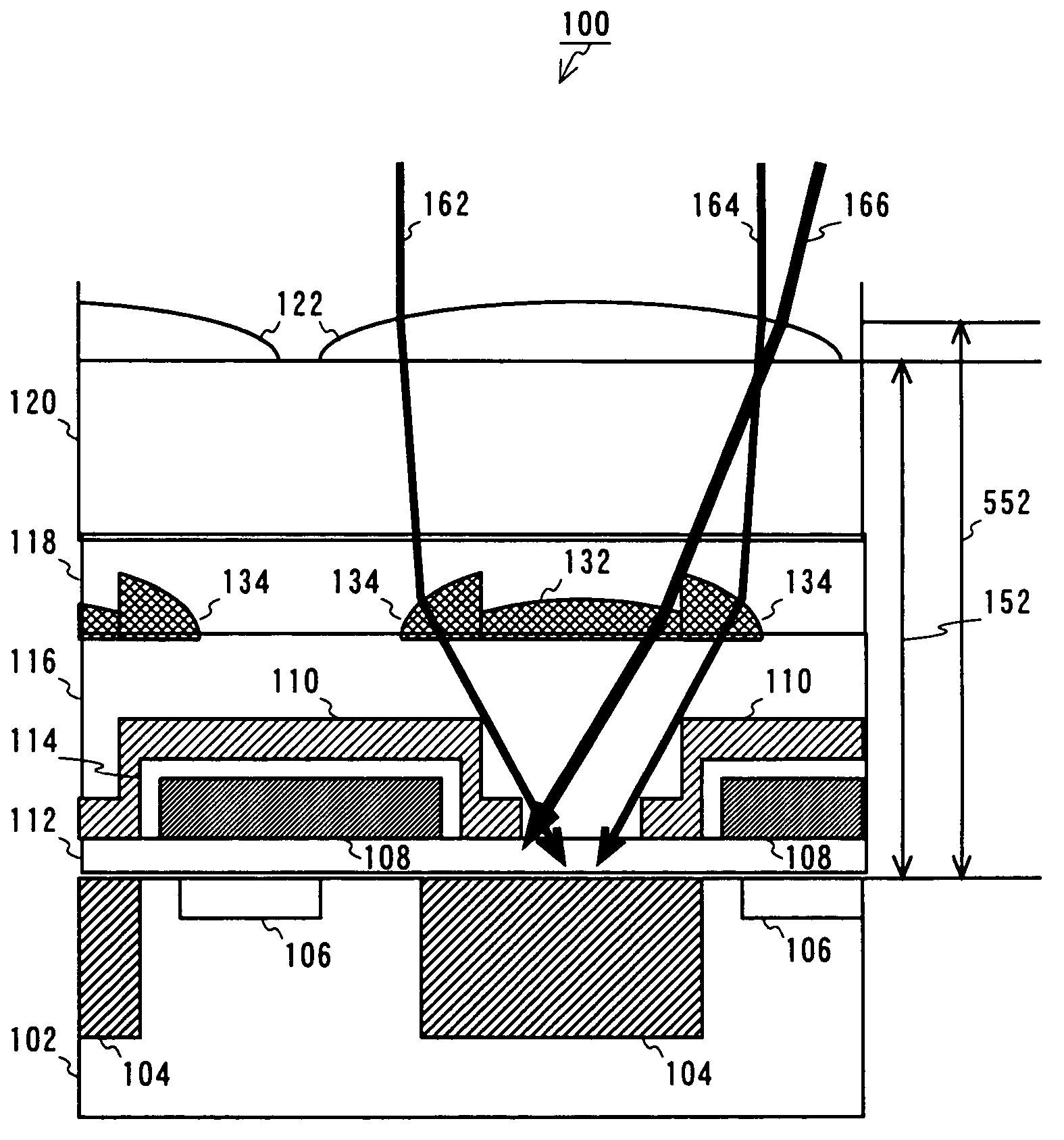

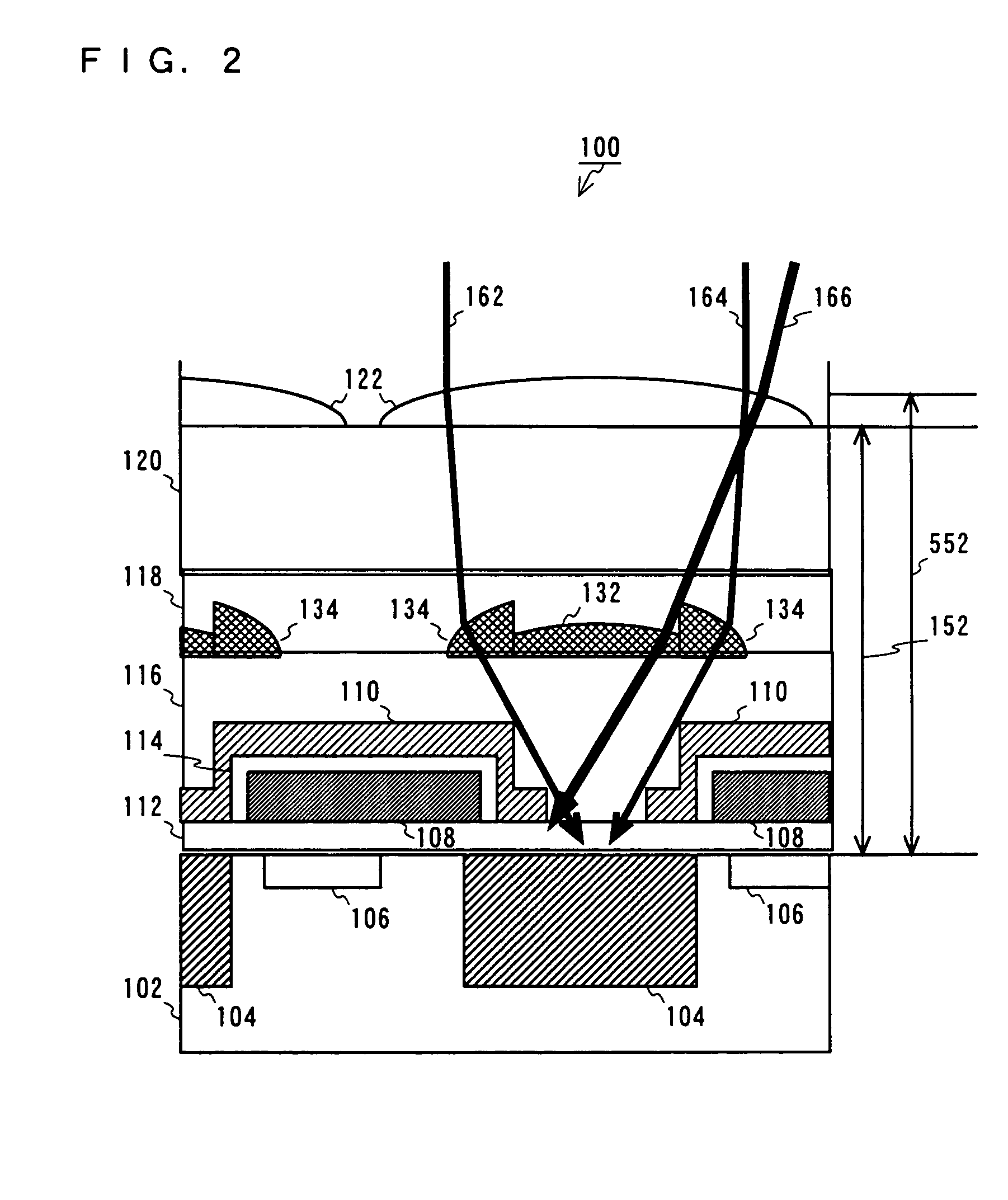

Solid state imaging device including annular and center lens in contact with each other

InactiveUS7499094B2High sensitivitySmall sizeTelevision system detailsSolid-state devicesFresnel lensEntocentric lens

Each intralayer lens disposed between a color filter 120 and photoelectric conversion sections has a Fresnel lens structure composed of a center lens 132 and an annular lens 134. As a result, the thickness of the intralayer lenses is reduced, and positions of upper lenses can be lowered without having to reduce the thickness of a color filter.

Owner:COLLABO INNOVATIONS INC

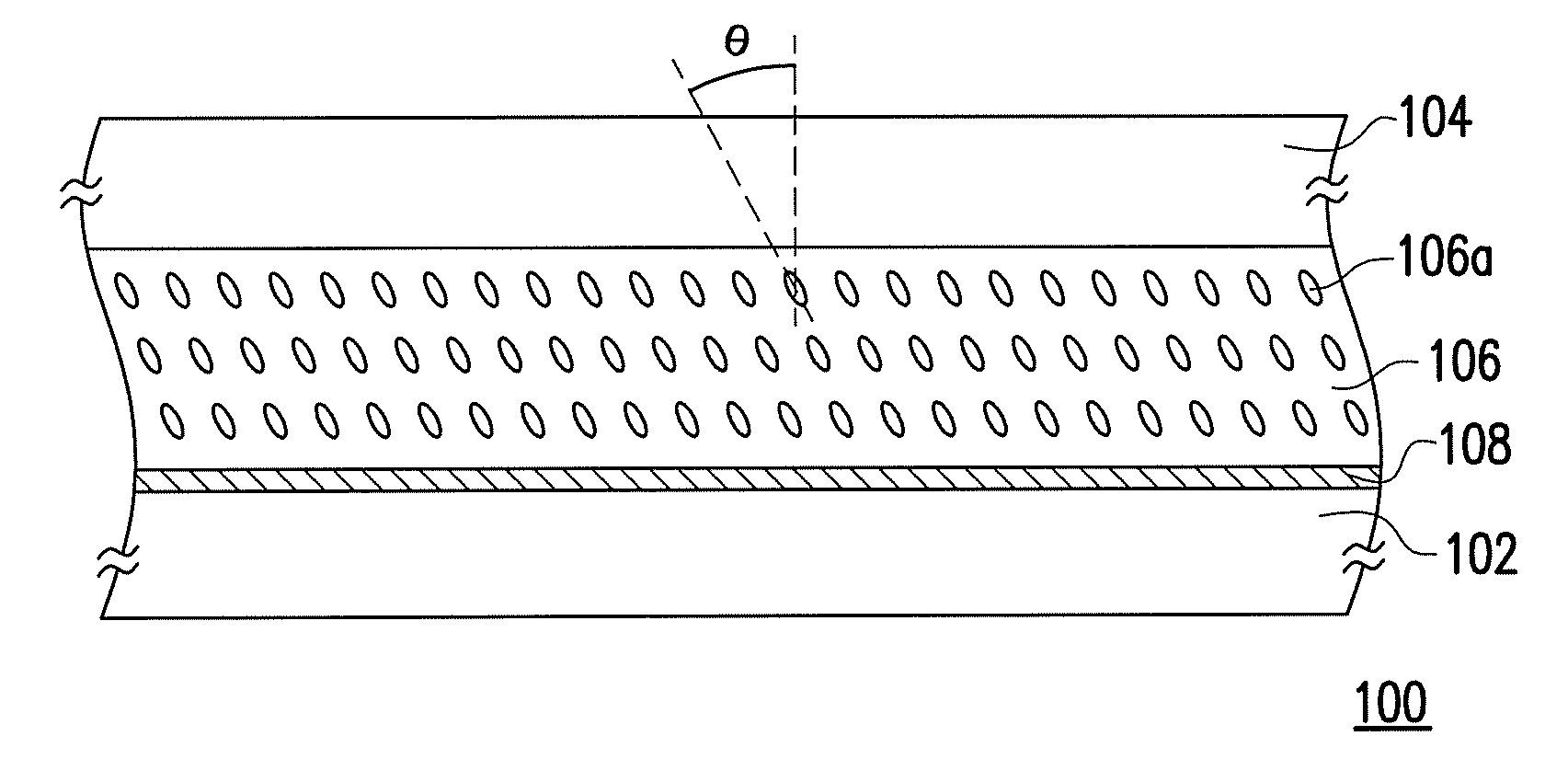

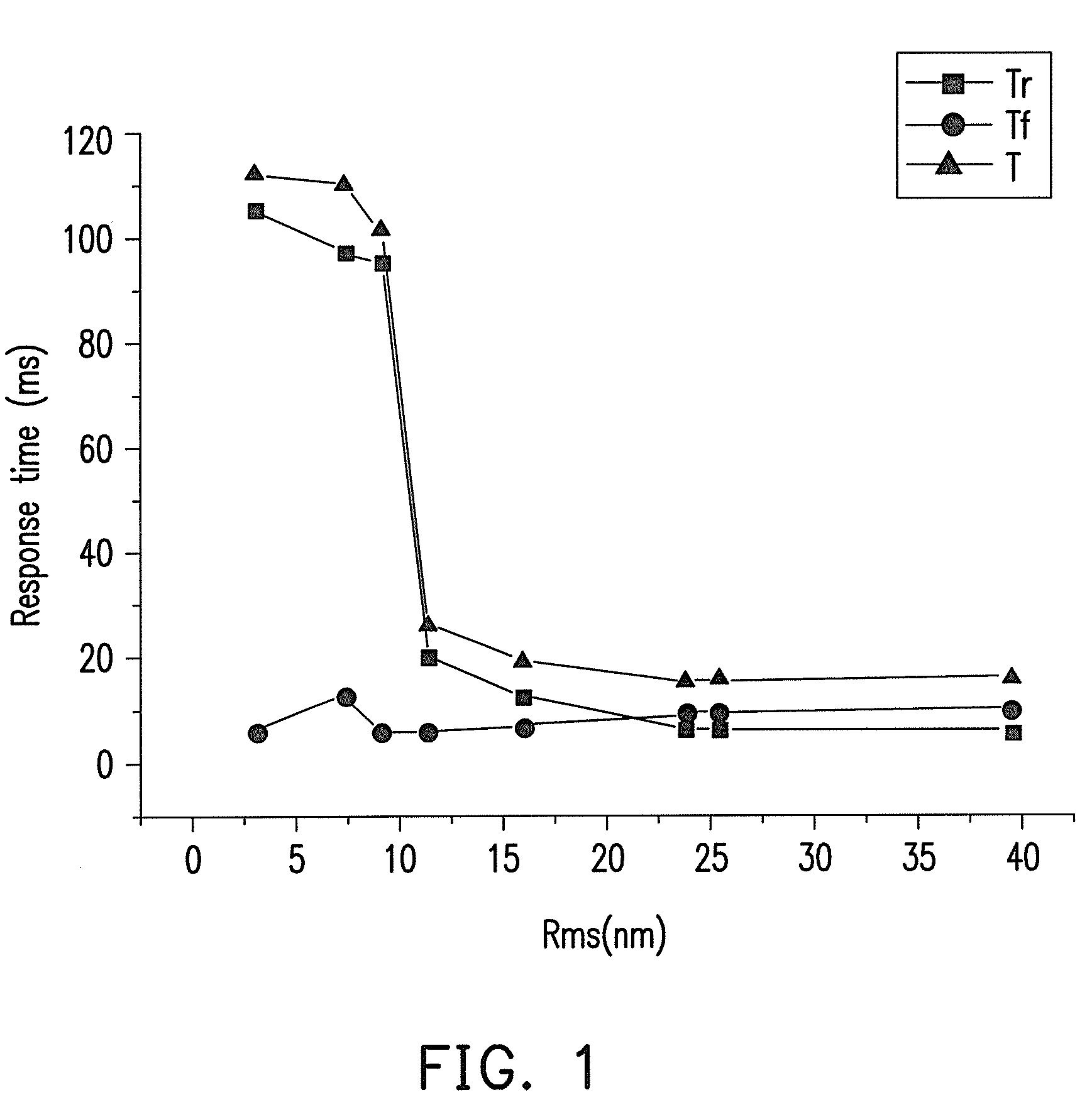

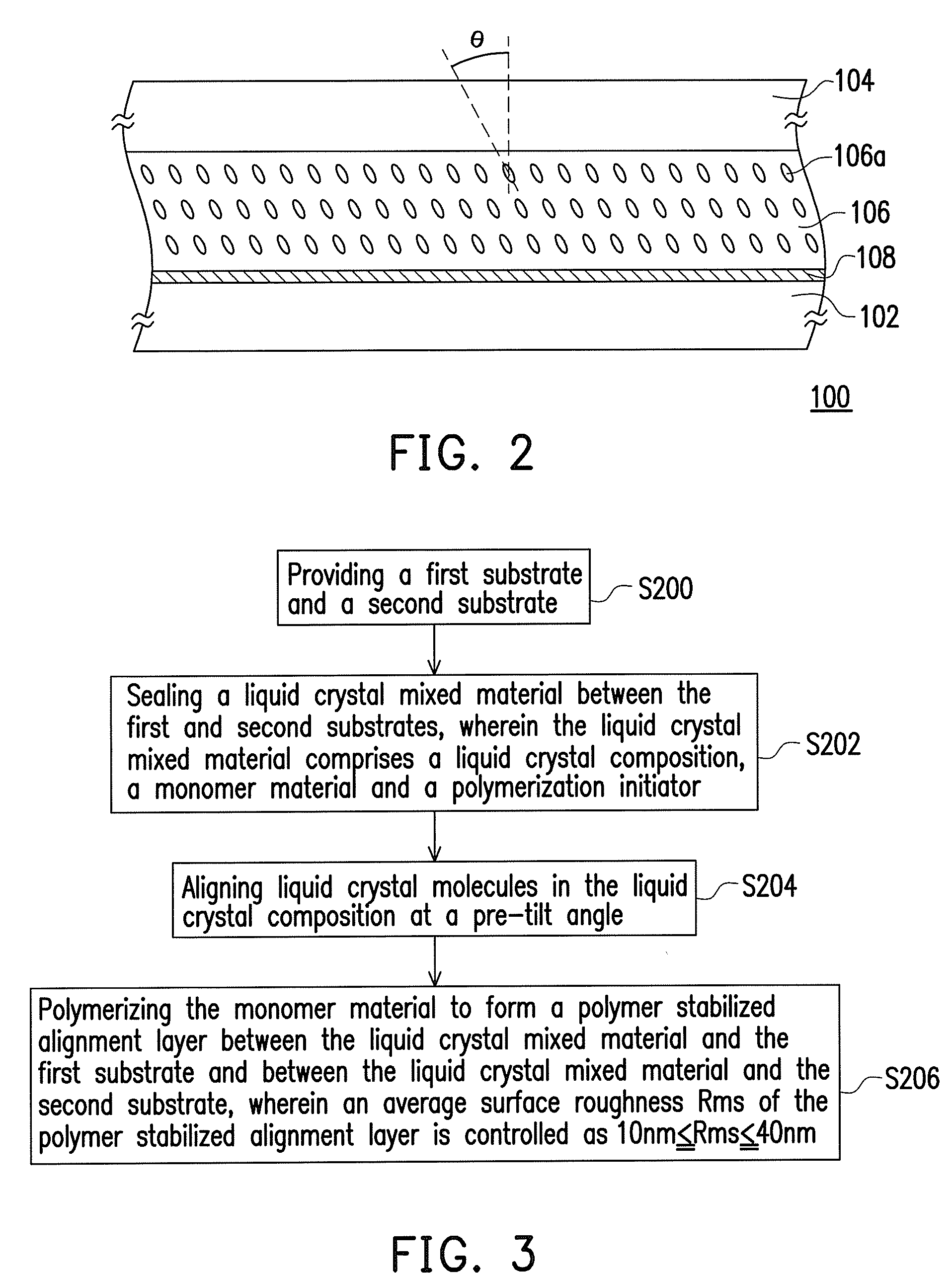

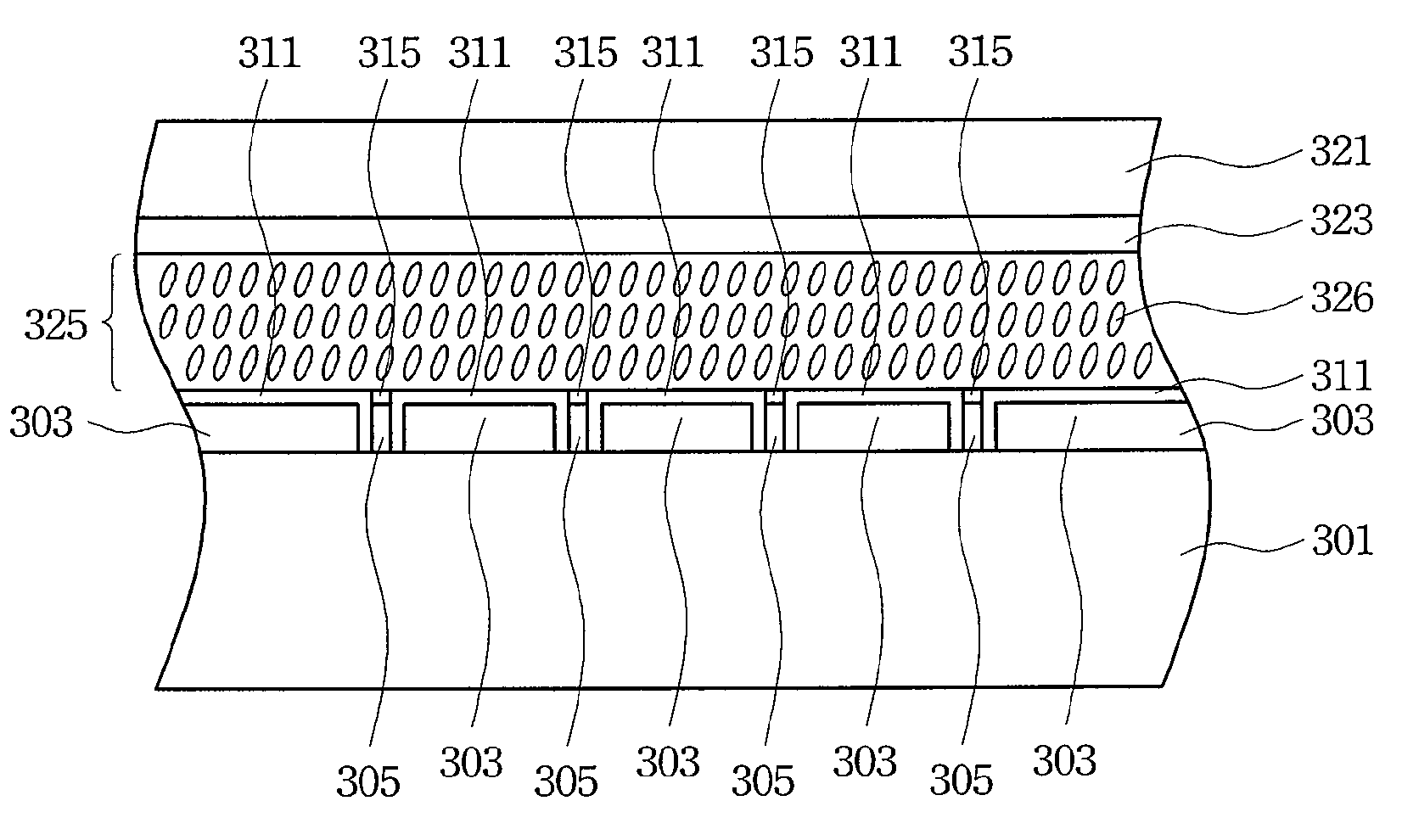

Liquid crystal display panel and fabricating method thereof

ActiveUS20100015363A1Improve response timeReduce image stickingLiquid crystal compositionsThin material handlingLiquid-crystal displayLiquid crystal

A liquid crystal display panel including a first substrate, a second substrate, a liquid crystal layer, and a polymer stabilized alignment layer is provided. The second substrate is disposed opposite to the first substrate. The liquid crystal layer is disposed between the first substrate and the second substrate. The polymer stabilized alignment layer is disposed between the first substrate and the liquid crystal layer, and an average surface roughness of the polymer stabilized alignment layer is greater than or equal to 10 nm.

Owner:AU OPTRONICS CORP

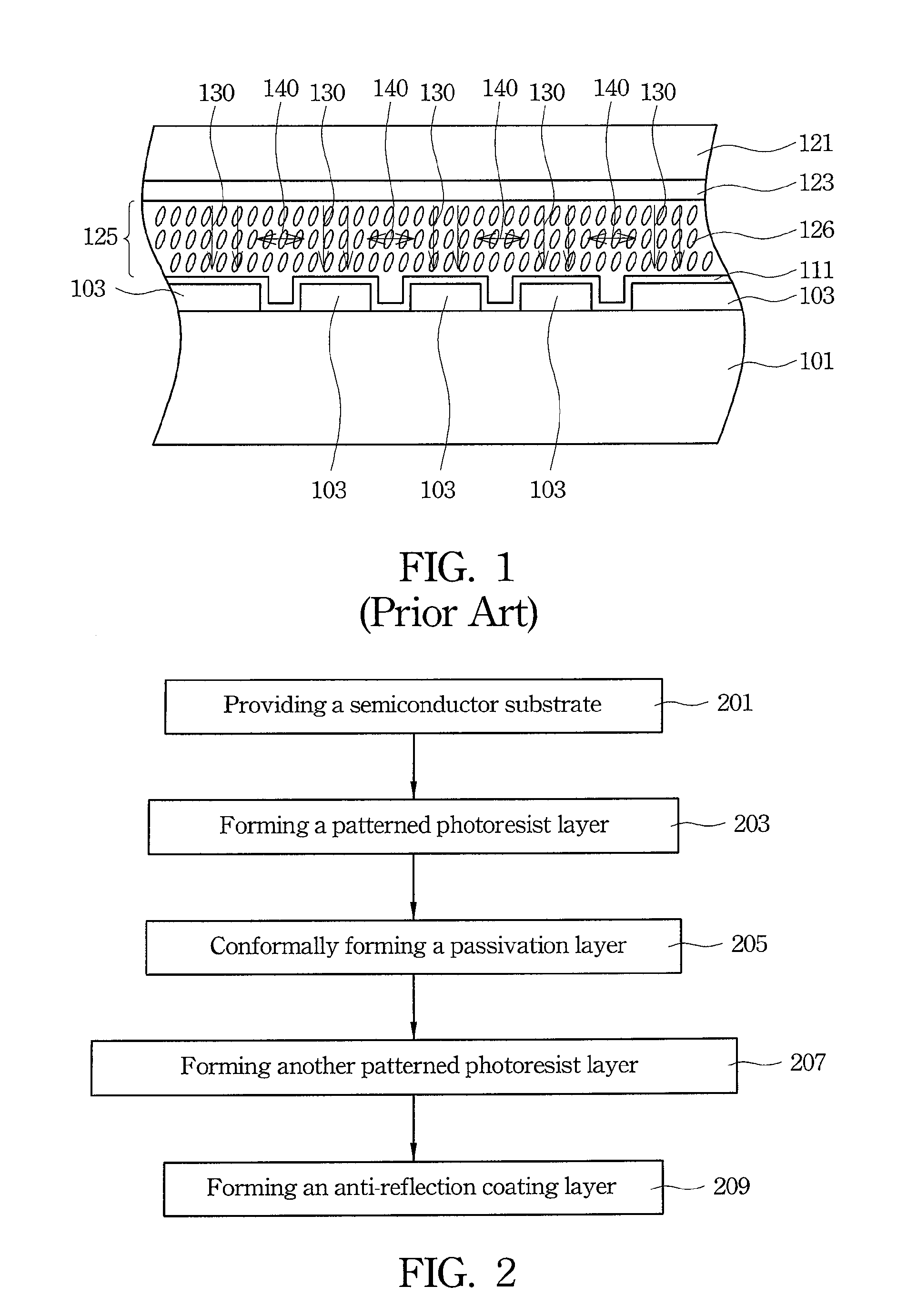

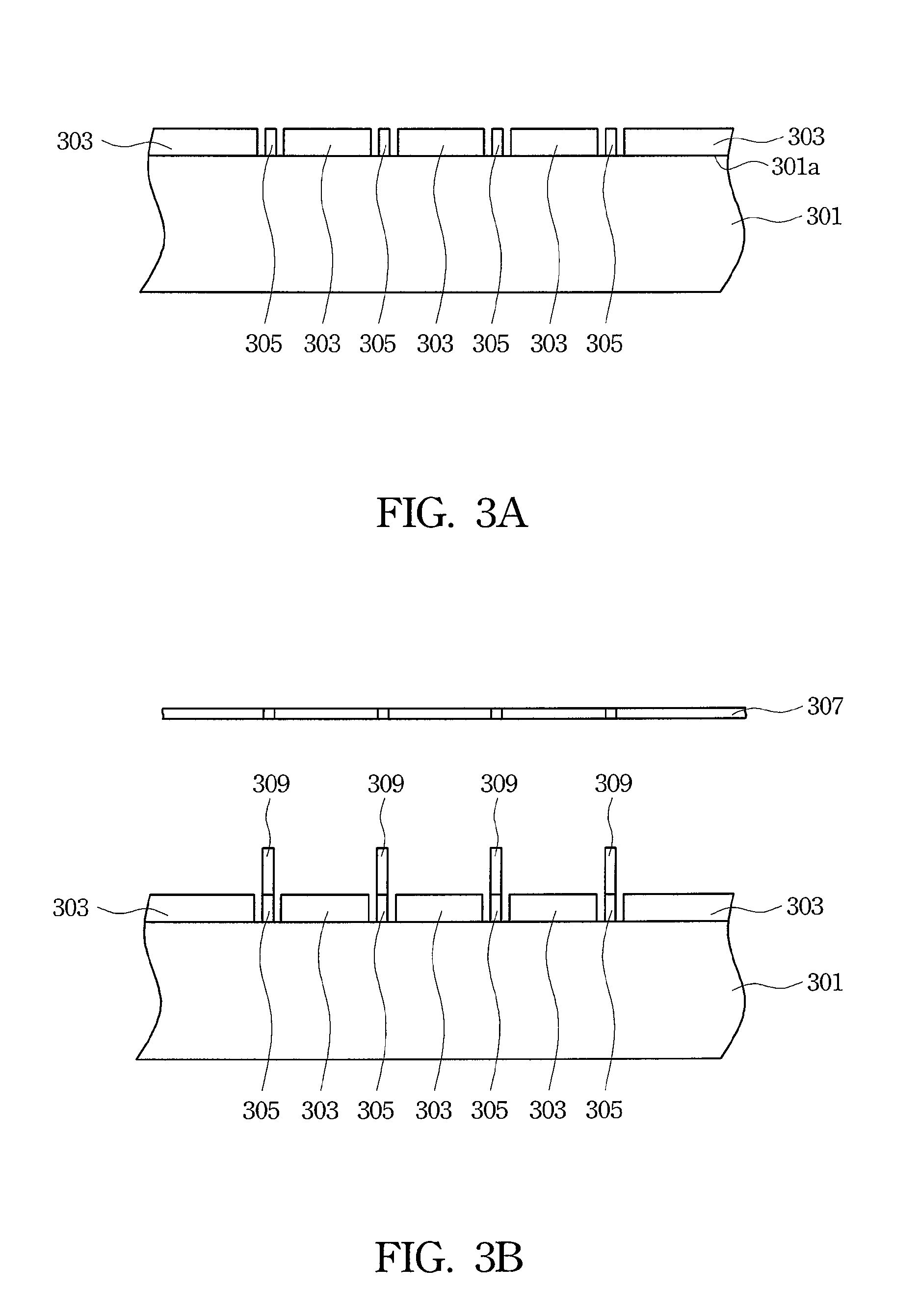

Liquid Crystal on Silicon Display Panel with Reducing Fringe Effect

ActiveUS20090015742A1Reduce edge effectsIncrease production costStatic indicating devicesNon-linear opticsSiliconLiquid crystal on silicon

A liquid crystal on silicon (LCOS) display panel with reducing fringe effect is provided herein. The liquid crystal on silicon display panel includes a common electrode, a semiconductor substrate having a plurality of pixel electrodes and control electrodes, a passivation layer on the pixel electrodes and a part of the semiconductor substrate, an anti-reflection coating (ARC) layers on the control electrodes, a transparent substrate on the semiconductor substrate, and a liquid crystal layer between the transparent substrate and the semiconductor substrate, wherein each of the control electrodes is disposed between and isolated with two adjacent ones of the pixel electrodes.

Owner:HIMAX TECH LTD

Semiconductor device and manufacturing method thereof

InactiveUS20100165255A1High image qualityReduce light leakageTube/lamp screens manufactureSolid-state devicesSemiconductorPolymer

It is an object to provide a liquid crystal display device capable of displaying a moving image with high image quality by employing a time-division display system (also called a field-sequential system) with the use of a plurality of light-emitting diodes (hereinafter referred to as LEDs) as a backlight. Further, it is an object to provide a liquid crystal display device in which high image quality, full color display, or low power consumption is realized by adjustment of the peak luminance. After a liquid crystal layer is sealed between a pair of substrates, polymer stabilization treatment is performed with the use of UV irradiation from both above and below the pair of substrates at the same time, whereby the polymer included in the liquid crystal layer sandwiched between the pair of substrates is evenly distributed. Thus, a liquid crystal display device is manufactured.

Owner:SEMICON ENERGY LAB CO LTD

Liquid crystal display having wide viewing angle

InactiveUS6930740B2Wide viewing angleImprove picture qualityNon-linear opticsLiquid-crystal displayImage quality

A liquid crystal display includes a first substrate with pixel electrodes, and a second substrate with a common electrode facing the first substrate. The common electrode has depression patterns corresponding to the pixel electrodes. The side wall of each depression pattern is at an angle of 30-120° with respect to the first substrate. The depression patterns of the common electrode are formed through making depression patterns at color filters. In this structure, the liquid crystal display bears wide viewing angle and good picture quality.

Owner:SAMSUNG DISPLAY CO LTD

Liquid Crystal Panel, Liquid Crystal Television, And Liquid Crystal Display Apparatus

InactiveUS20070200987A1Reduce light leakageIncrease contrastPolarising elementsNon-linear opticsColor shiftEngineering

It is an object of the present invention to provide a liquid crystal panel, a liquid television and a liquid crystal display apparatus each having significantly reduced light leak and coloring in black display, a high contrast ratio in an oblique direction and a small color shift in an oblique direction. A liquid crystal panel according to the present invention includes: a liquid crystal cell including a liquid crystal layer containing nematic liquid crystals in homogeneous alignment in an absence of an electric field; a first polarizer arranged on a viewer side of the liquid crystal cell; a first laminated optical element arranged between the liquid crystal cell and the first polarizer; a second polarizer arranged on a backlight side of the liquid crystal cell; and a second laminated optical element arranged between the liquid crystal cell and the second polarizer.

Owner:NITTO DENKO CORP

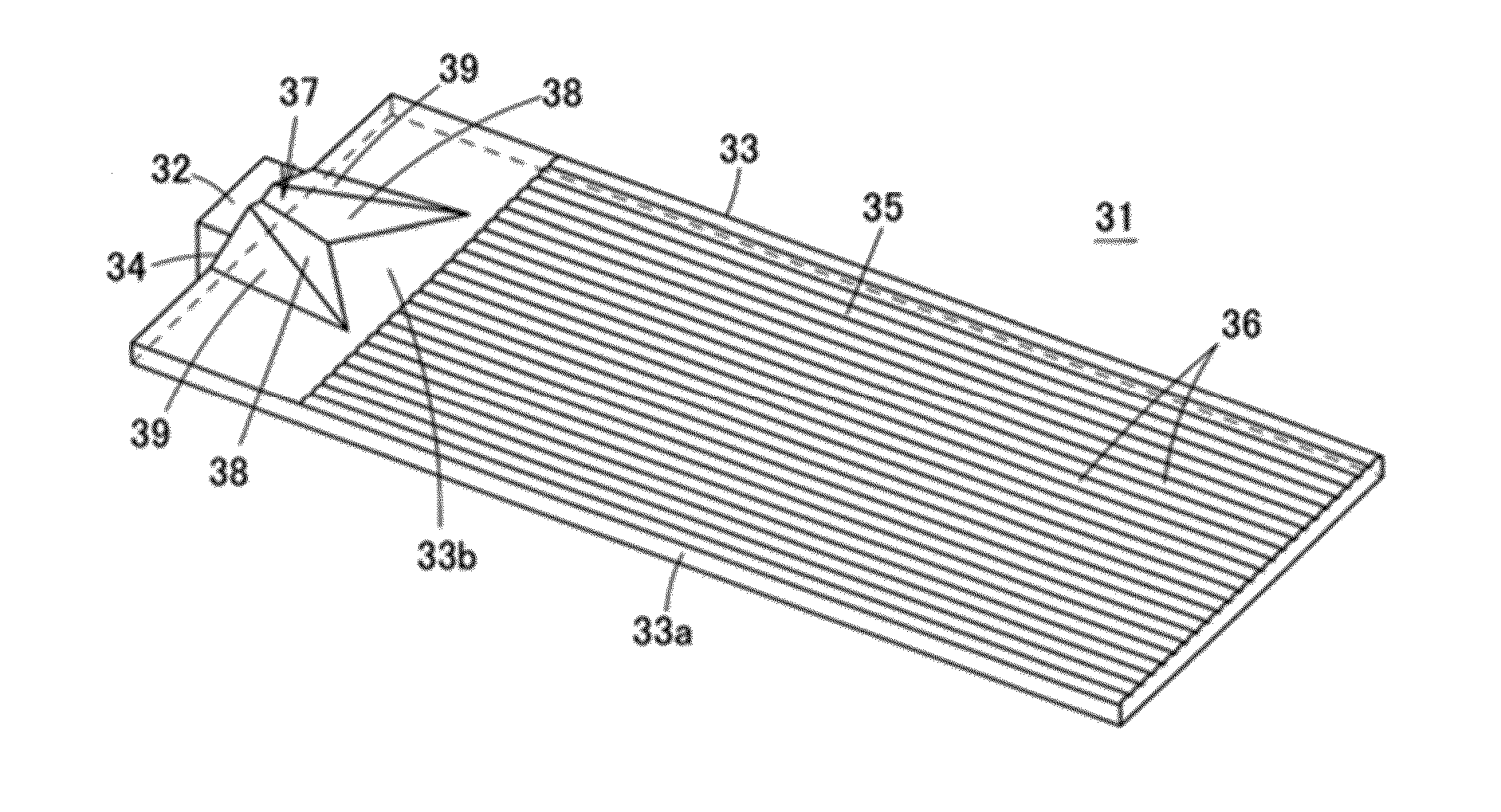

Light guide plate and surface light source device

ActiveUS20150293289A1Efficient entryReduce light leakageMechanical apparatusPlanar/plate-like light guidesLight guideOptoelectronics

A light guide plate has a light guide plate member having a light incident surface on an end face of the light guide member, and a light emitting surface on a front surface of the light guide plate member, wherein the light incident surface is structured to have light incident thereon, and wherein the light emitting surface is structured to widen and emit light incident thereon out of the light guide plate member, and a directivity changing unit arranged on a light incident end portion of the light guide plate member on the front surface or a back surface of the light guide plate member. The directivity changing unit has a first inner inclined surface and a second inner inclined surface that change a directivity of the incident light within the directivity changing unit to widen the light laterally with respect to a direction perpendicular to the light incident surface.

Owner:ORMON CORP