Hybrid task scheduling method of directed acyclic graph (DGA) based reconfigurable system

A directed acyclic graph and system reconstruction technology, applied in the direction of program startup/switching, multi-program installation, etc., can solve the problem of high energy consumption of FPGA, and achieve the effect of reducing scheduling overhead and configuration times.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

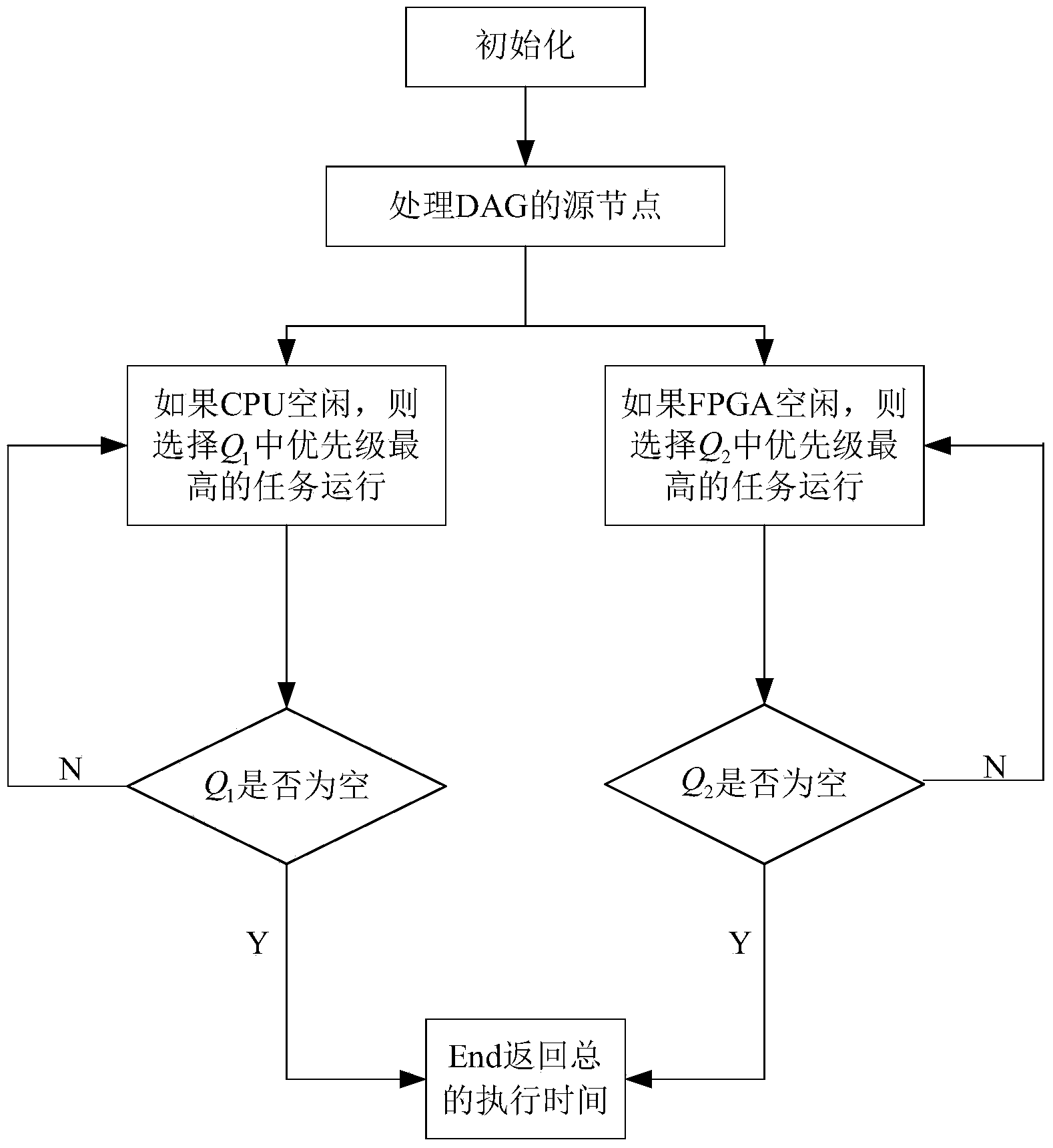

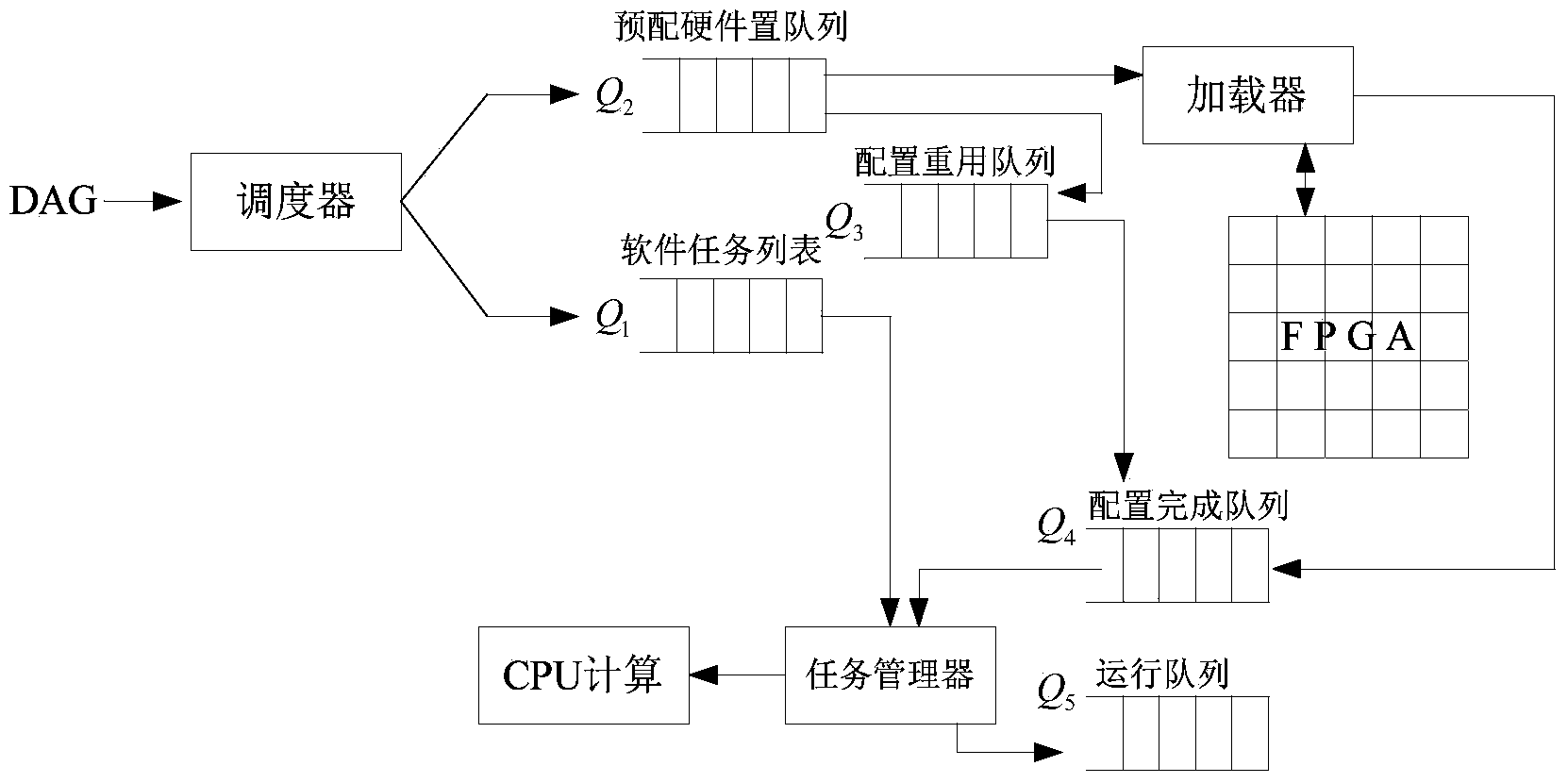

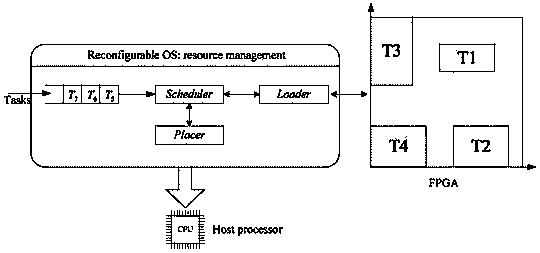

[0020] The method includes a scheduler, a loader, and a layout device. The scheduler includes a task replacement strategy judgment module, a preconfiguration module, and a configuration reuse module. The scheduler schedules tasks into the software task queue and task queue respectively according to the tasks and task types described by the DAG. Preconfigured hardware task queue. For the tasks in the software task queue, the calculation will be based on whether the CPU is idle and the priority; for the tasks in the pre-configured hardware task queue, first apply the configuration reuse policy to judge, if it can be reused, it will enter the configuration reuse queue; if not For reuse, the pre-configured priority calculation method is used to consider the factors that affect the length of task scheduling, and priority scheduling of tasks on the critical path and with a smaller area is beneficial to reduce delay and shorten the length of scheduling time. Wait for the pre-configur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More