Device and method for buffering data in dynamic reconfigurable array

A data cache and array technology, applied in data transformation, electrical digital data processing, general-purpose stored program computer, etc., can solve the problem of slow external memory read and write speed, the algorithm structure cannot be arranged into the array, and affects the calculation of dynamic reconfigurable processors. performance and other issues, to achieve the effect of reducing the number of data transfers, reducing the number of configurations, and achieving array expansion.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

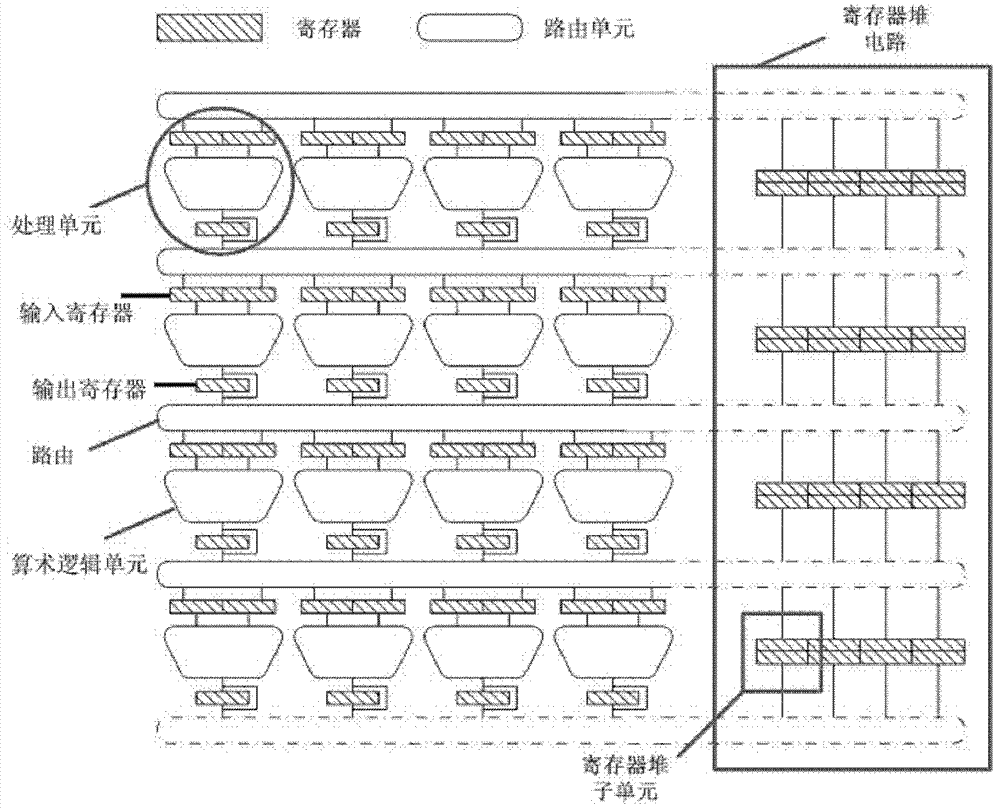

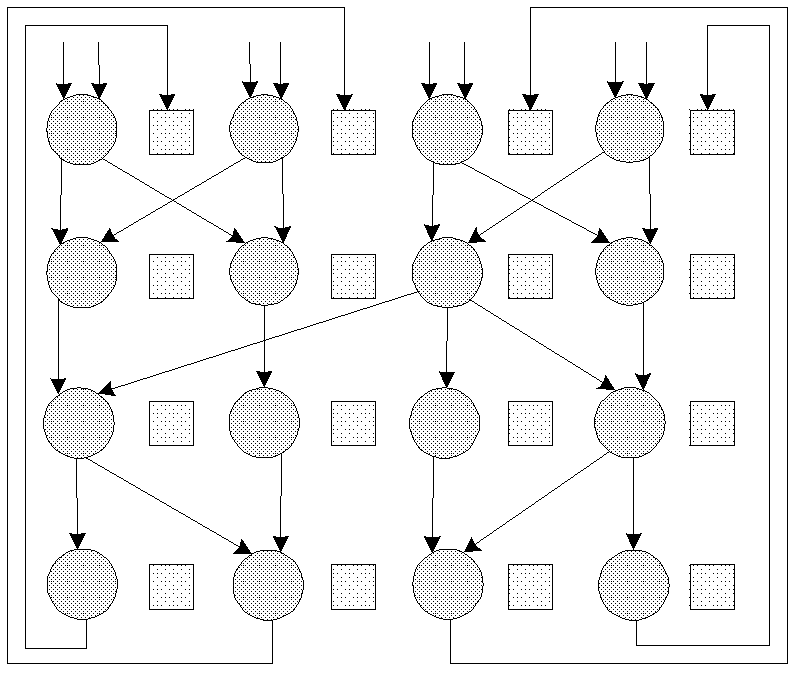

[0087] The circles in the data flow diagram represent processing units, and the squares represent register file subunits.

[0088] refer to image 3 and Figure 4 A data flow diagram using Configuration 1 and Configuration 2 of the present application is shown. Configuration 1 and configuration 2 are executed sequentially, and their data are correlated, that is, the four result data output from the data flow graph in configuration 1 after logical operations will be used as the input data of the data flow graph in configuration 2.

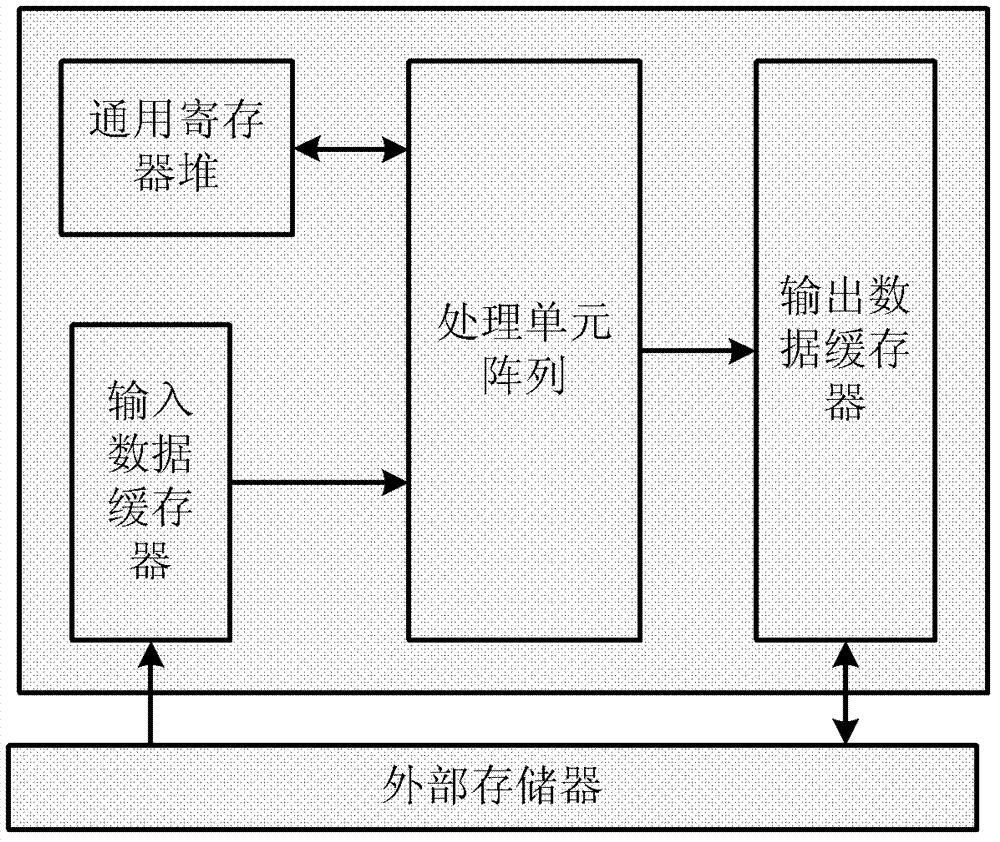

[0089] When the general-purpose register file (Temp_reg) is not introduced, the four result data output in configuration 1 must be input to the output data buffer (Output FIFO) first, and then output to the external memory. When configuration 2 needs to be calculated, the four result data The data is output from the external memory to the input data buffer (Input FIFO), and then input to the processing unit array (RCA) for logical operation.

[0...

Embodiment 2

[0101] refer to Figure 5 and Image 6 The data flow diagram of configuration 3 without using the application and the data flow diagram of configuration 3 after using the application are respectively shown. because Figure 5 The parallel width of the data path in the data flow graph described in the above is 6, which is greater than the width of the processing unit array of 4, so it needs to be decomposed into two sub-graphs and then operated, that is, two operations are required. but if Image 6 After the general-purpose register file is added as shown in , the intermediate data can be cached by the register file, and the additional two paths can be put into it through the general-purpose register file, and the logic operation operation can be completed synchronously with the other four paths.

[0102] Therefore, through the general-purpose register file, additional data paths of the dynamic reconfigurable array can be added to realize array expansion, making the configura...

Embodiment 3

[0119] refer to Figure 7 and Figure 8 The data flow diagram of configuration 4 without using the application and the data flow diagram of configuration 4 after using the application are respectively shown.

[0120] The process of data processing for configuration 4 without using this application includes:

[0121] S41, the external memory outputs the data IN0-IN8 to the input data buffer;

[0122] S42, the input data buffer outputs the data IN0-IN7 to the first row of the processing unit array for calculation; the calculation result of the first row is passed to the second row; so continue to the third row to transfer the result data to the fourth row;

[0123] S43, the input data buffer outputs the data IN8 to the fourth row of the processing unit array, and the fourth row performs a logical operation on the result data input from the third row and IN8 to obtain the result data OUT0-OUT1;

[0124] S44, output the operation result data OUT0-OUT1 to the output data buffer;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More