FPGA verification method and system based on processor system

A processor system and verification method technology, applied in the field of chip design, can solve problems such as difficult to effectively debug and locate faults, and achieve the effects of optimization, resource saving, and rich scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The content of the present invention will be described in detail below in conjunction with the accompanying drawings.

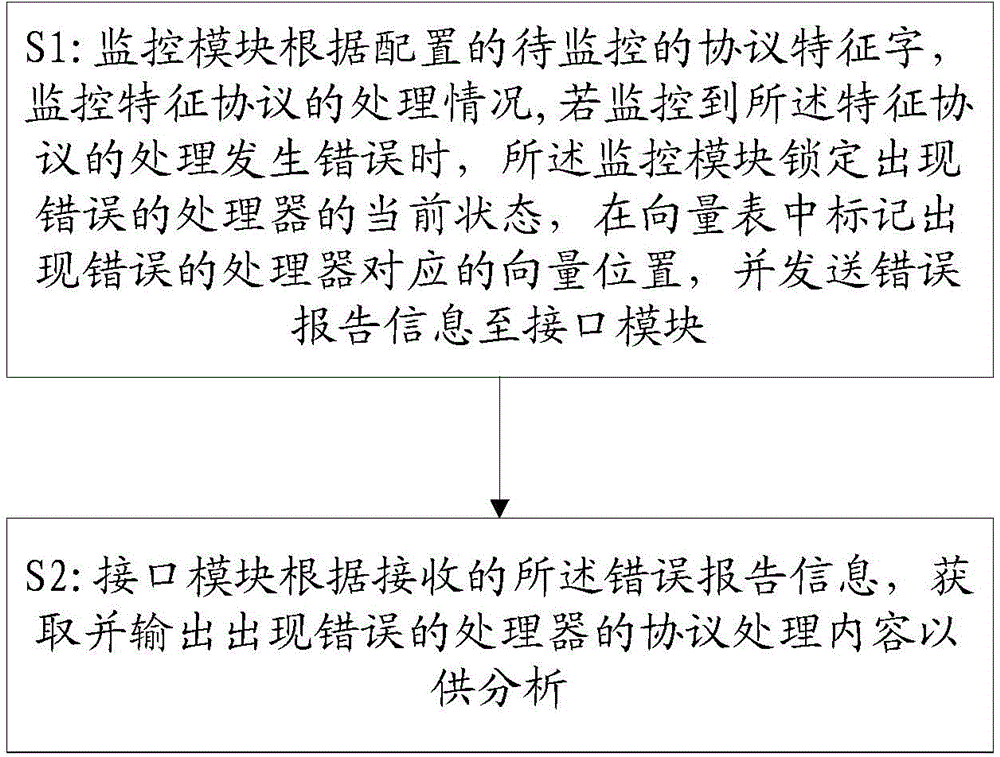

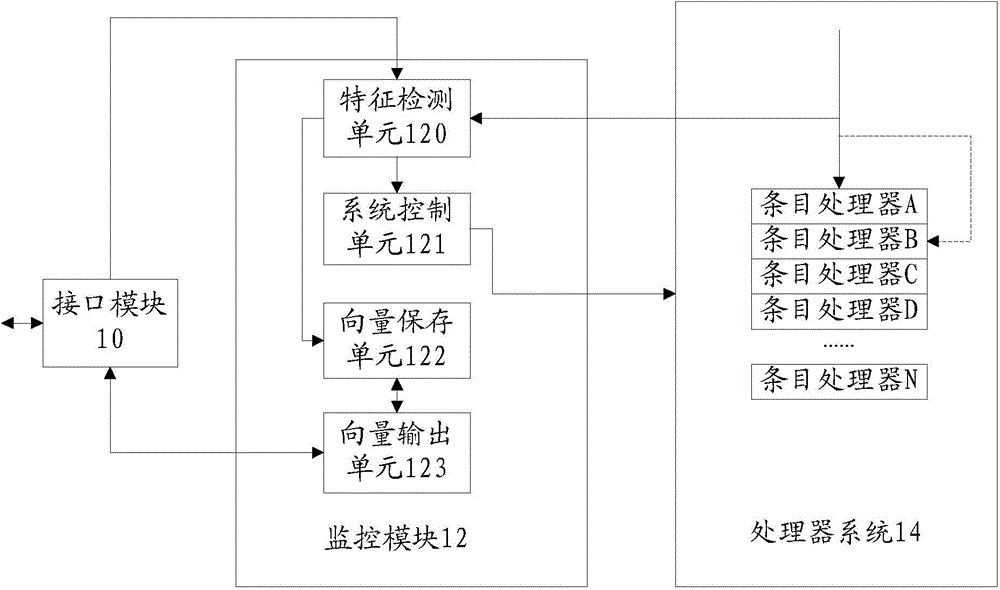

[0021] figure 1 Shown is the outflow diagram of the FPGA verification method based on the processor system provided by the preferred embodiment of the present invention. figure 2 Shown is a schematic diagram of an FPGA verification system based on a processor system provided by a preferred embodiment of the present invention. Please also refer to figure 1 and figure 2 .

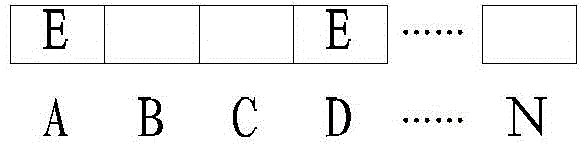

[0022] like figure 1 As shown, the FPGA verification method based on the processor system provided by the preferred embodiment of the present invention includes the following steps: S1: the monitoring module monitors the processing of the feature protocol according to the configured protocol feature word to be monitored, if the feature is monitored When an error occurs in the processing of the protocol, the monitoring module locks the current state of the error processor, marks...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More