Impact-resistant packaging structure of multi-chip integrated circuit

An integrated circuit and packaging structure technology, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as easily damaged wire bonds and chip surfaces, prevent extrusion effects and temperature stress effects, and improve assembly reliability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

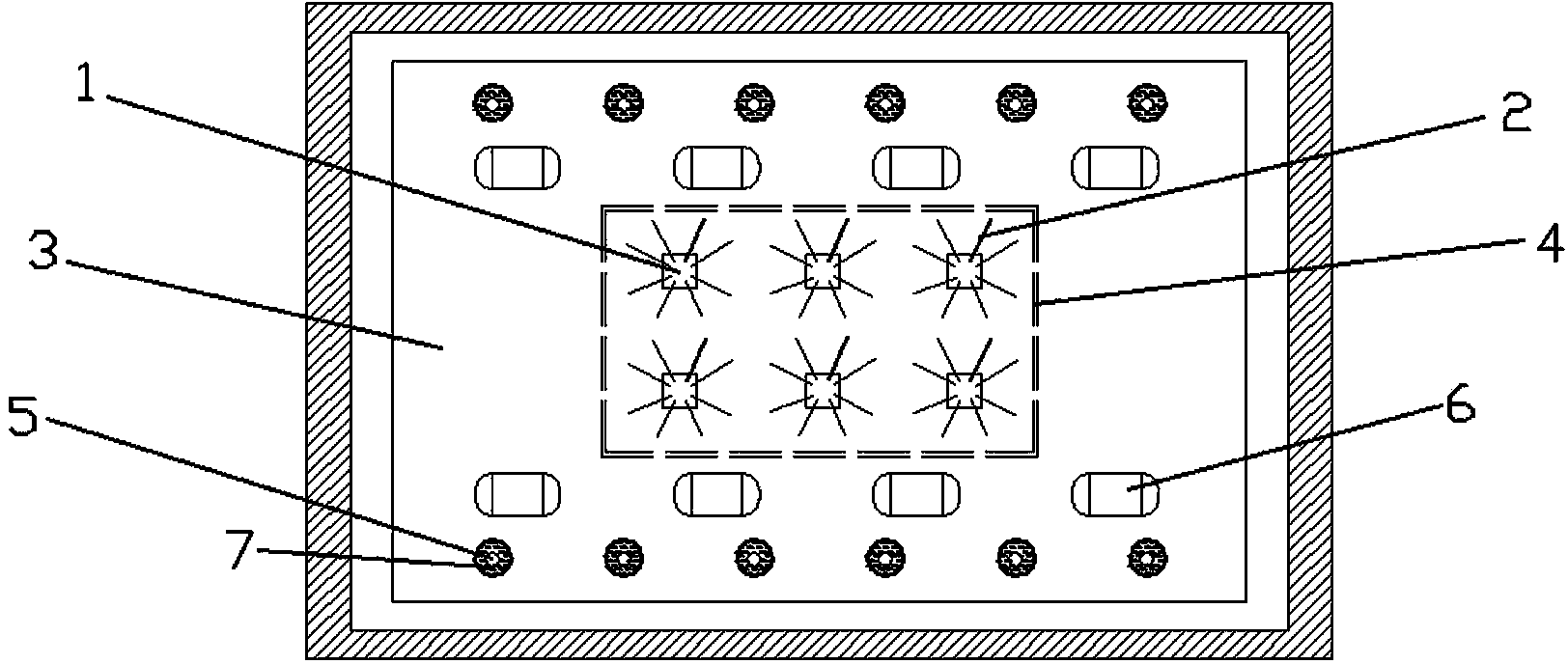

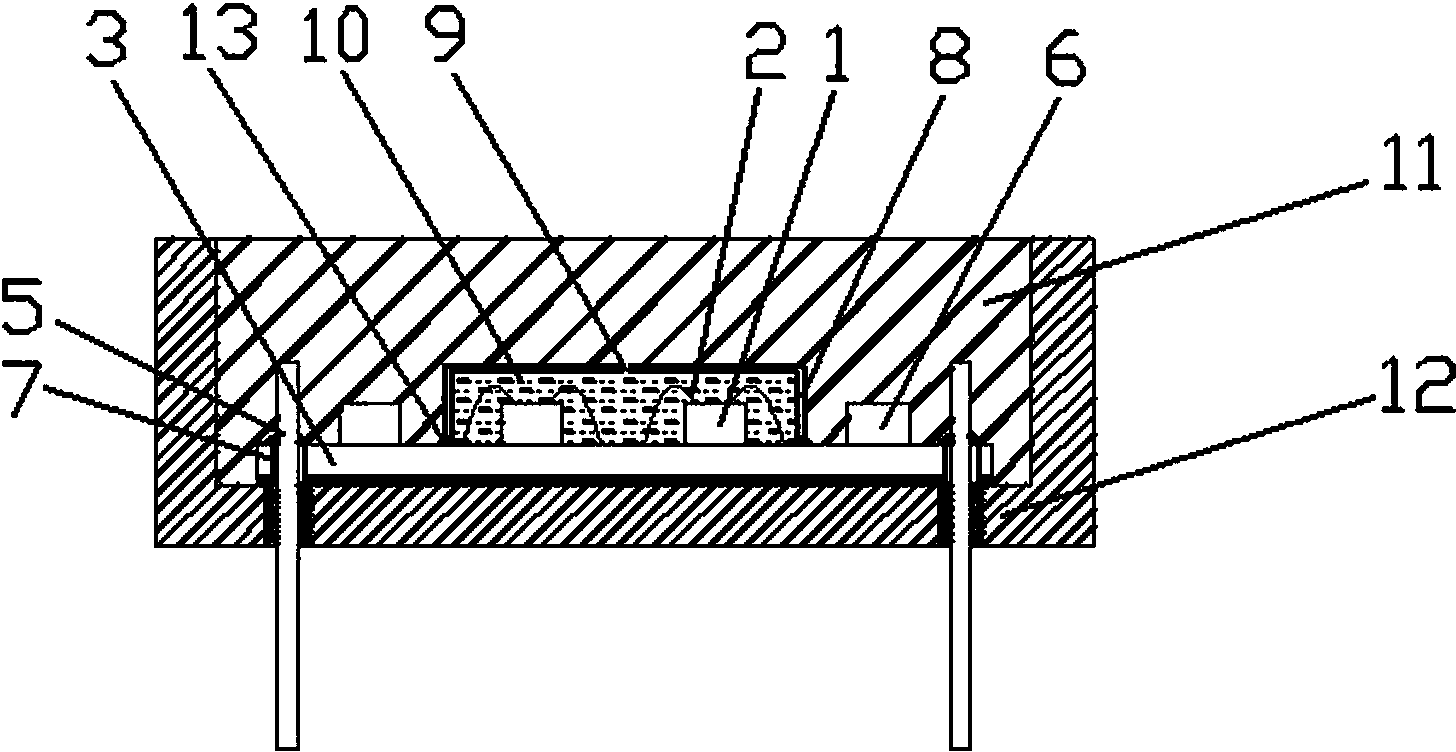

[0016] (1) If figure 1 As shown, the bonding area of the bare chip 1 and the lead wire 2 is concentratedly arranged in the middle of the circuit substrate 3, and the cap bonding area 4 is reserved around the bonding area of the bare chip. Complete the wire bonding assembly between the bare chip 1 and the substrate 3 , the assembly of the substrate 3 and the case base 12 , the electrical connection between the substrate and the case leads 5 , and the assembly of other components 6 on the substrate. Among them, the substrate 3 and the casing lead 5 adopt a conventional package interconnection method, that is, the edge of the substrate 3 is provided with a through hole, the casing lead 5 passes through the through hole, and the conductive material 7 (conductive epoxy or solder, etc.) is used on the periphery of the through hole. Enables interconnection of leads to via pads.

[0017] (2) Make the cap 8 of the box body structure, the top of the cap has a small hole 9, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More