Time sequence estimation method for FPGA (field programmable gate array) post-mapping net list

A netlist and timing technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as lack of block units and wiring resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Synthesize the circuit designed by the user and map the library to form a netlist, so that the basic units and their connection relationships can also be obtained. The basic units include: lookup tables, registers, memories, input and output, etc., and the connections between basic units The connection is called a single-segment connection, and the layout and routing are usually completed once on the FPGA chip. According to the result of the layout and routing, the delay value of any single-segment connection can be uniquely determined.

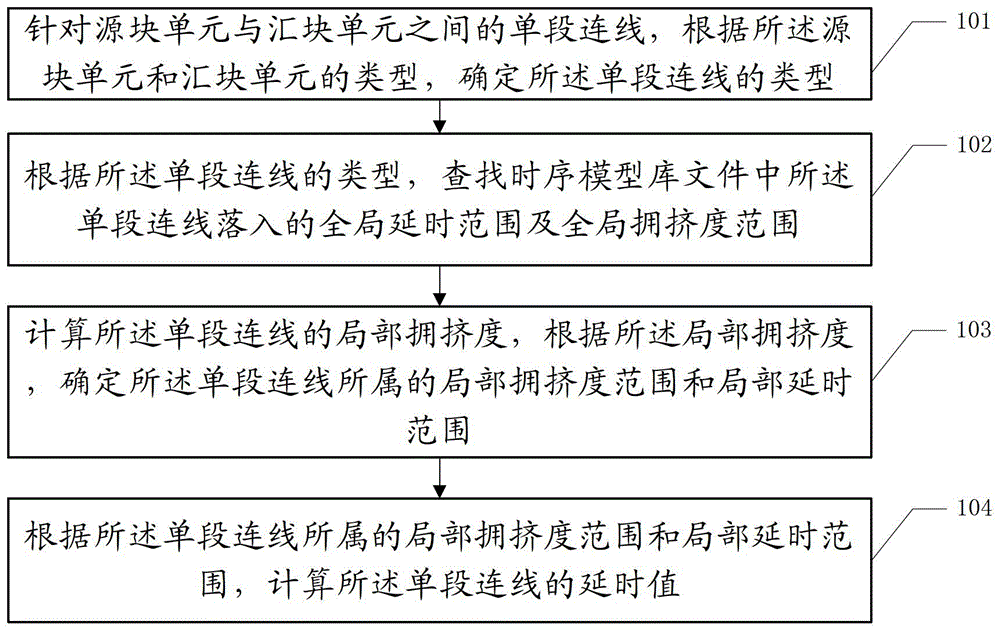

[0042] figure 1 It is a flow chart of the method for timing estimation of netlist after FPGA mapping provided by Embodiment 1 of the present invention. Such as figure 1 As shown, the method provided by the embodiment of the present invention includes:

[0043] Step 101, for a single-segment connection between a source block unit and a sink unit, determine the type of the single-segment connection according to the types of the source ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More