Clock constraint file collection method, device, equipment and storage medium

A technology for constraining files and obtaining methods, which is applied in the field of obtaining clock constrained files, can solve problems such as low development efficiency, failure to use normally, manual writing errors, etc., to improve accuracy and reliability, improve development efficiency, and save writing the effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

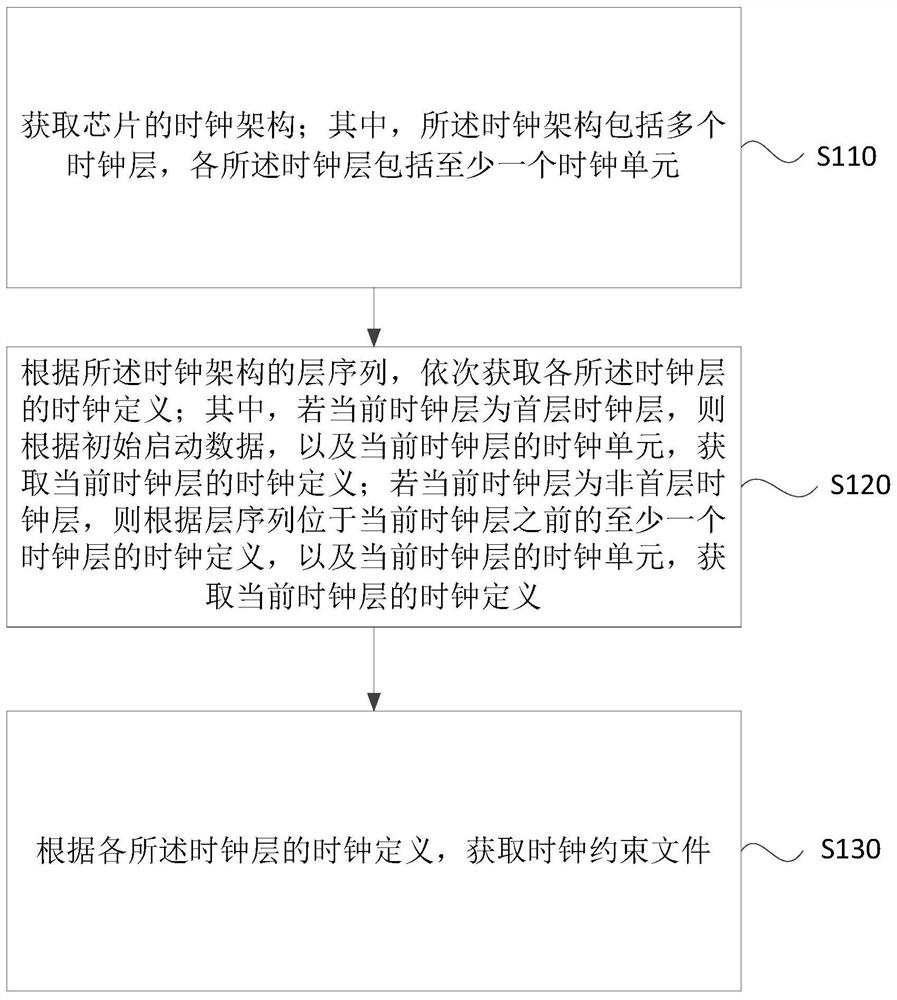

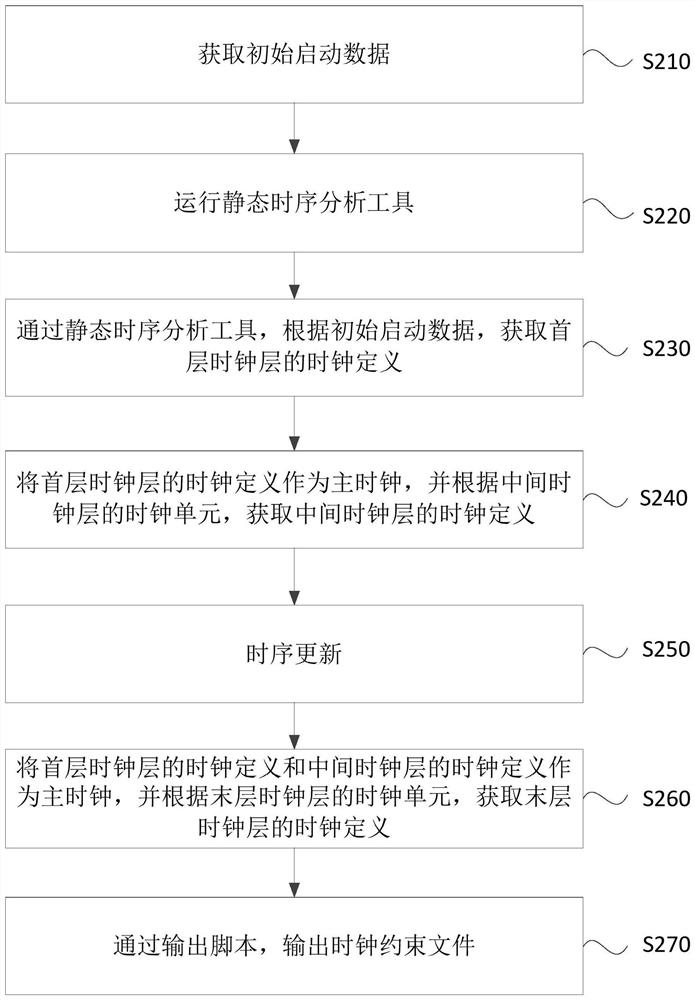

[0027] Figure 1A It is a flowchart of a method for obtaining a clock constraint file provided in Embodiment 1 of the present application. This embodiment is applicable to generating a clock constraint file of a chip, and the method can be executed by the device for obtaining a clock constraint file in the embodiment of the present application. , the device can be realized by software and / or hardware, and can generally be integrated in a chip, and the method specifically includes the following steps:

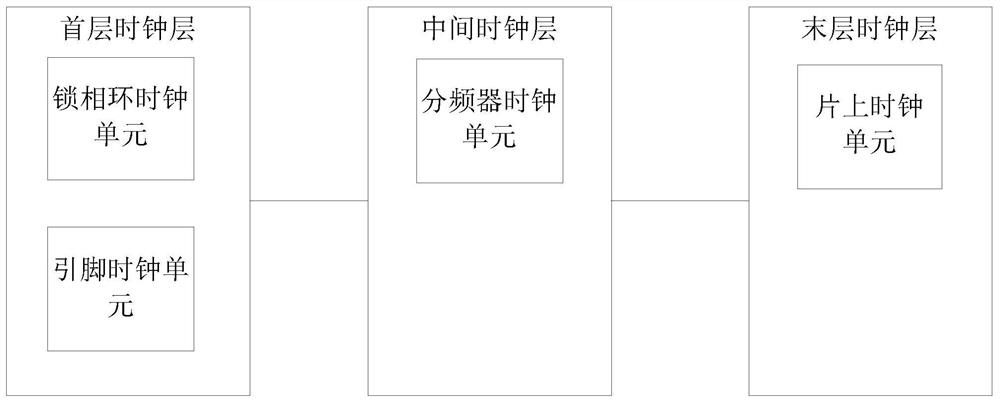

[0028] S110. Acquire a clock architecture of the chip; wherein, the clock architecture includes multiple clock layers, and each clock layer includes at least one clock unit.

[0029] The clock is a periodic pulse signal, which is used to provide a time reference for data transmission between synchronously executed circuits in the chip, and to ensure the synchronous operation of each component unit in the chip. According to different functional requirements of the chip, the trans...

Embodiment 2

[0059] figure 2 It is a structural block diagram of a clock constraint file acquisition device provided in Embodiment 2 of the present application, and the device specifically includes: a clock architecture acquisition module 210 , a clock definition acquisition module 220 and a constraint file acquisition module 230 .

[0060] A clock architecture acquisition module 210, configured to acquire the clock architecture of the chip; wherein, the clock architecture includes multiple clock layers, and each clock layer includes at least one clock unit;

[0061] The clock definition acquisition module 220 is used to sequentially acquire the clock definition of each clock layer according to the layer sequence of the clock architecture; wherein, if the current clock layer is the first clock layer, then according to the initial startup data and the current clock layer Clock unit, to obtain the clock definition of the current clock layer; if the current clock layer is a non-first clock l...

Embodiment 3

[0079] image 3 It is a schematic structural diagram of a device provided in Embodiment 3 of the present application. image 3 A block diagram of an exemplary device 12 suitable for implementing embodiments of the present application is shown. image 3 The device 12 shown is only an example, and should not impose any limitation on the functions and scope of use of the embodiments of the present application.

[0080] Such as image 3 As shown, device 12 takes the form of a general purpose computing device. Components of device 12 may include, but are not limited to: one or more processors or processing units 16, system memory 28, bus 18 connecting various system components including system memory 28 and processing unit 16.

[0081] Bus 18 represents one or more of several types of bus structures, including a memory bus or memory controller, a peripheral bus, an accelerated graphics port, a processor, or a local bus using any of a variety of bus structures. These architectur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More