Asynchronous clock synchronization constraint method in chip design

An asynchronous clock and chip design technology, applied in computer-aided design, calculation, special data processing applications, etc., can solve problems such as increased product time costs, timing problems, and tape-out cost losses, making it easy to find, correct, and reduce Error rate, time and cost saving effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0021] The present invention proposes a theoretical method of asynchronous clock synchronization timing constraints, and performs synchronous processing on the asynchronous clocks in design when timing constraints are achieved, which achieves very good results in practice. This theoretical method can be used as a general clock constraint method.

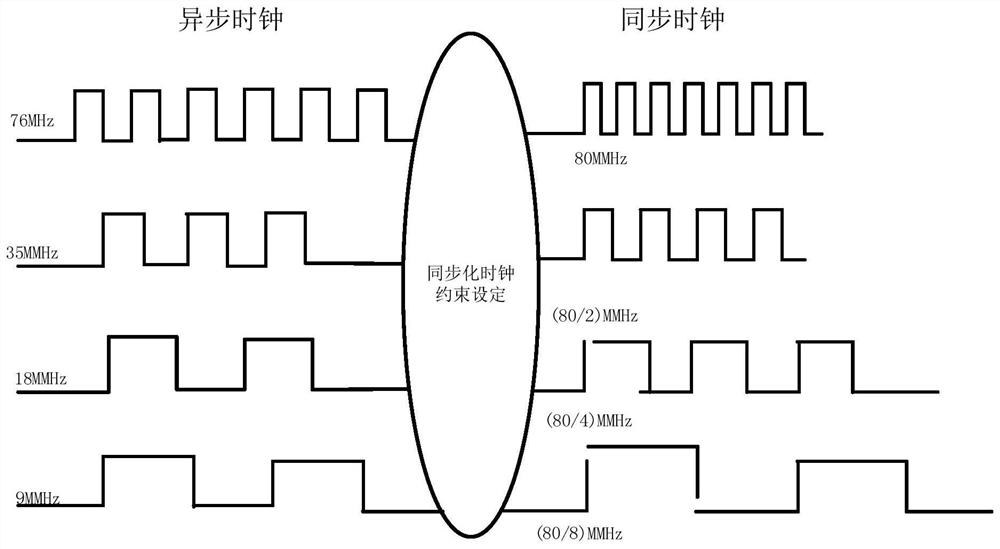

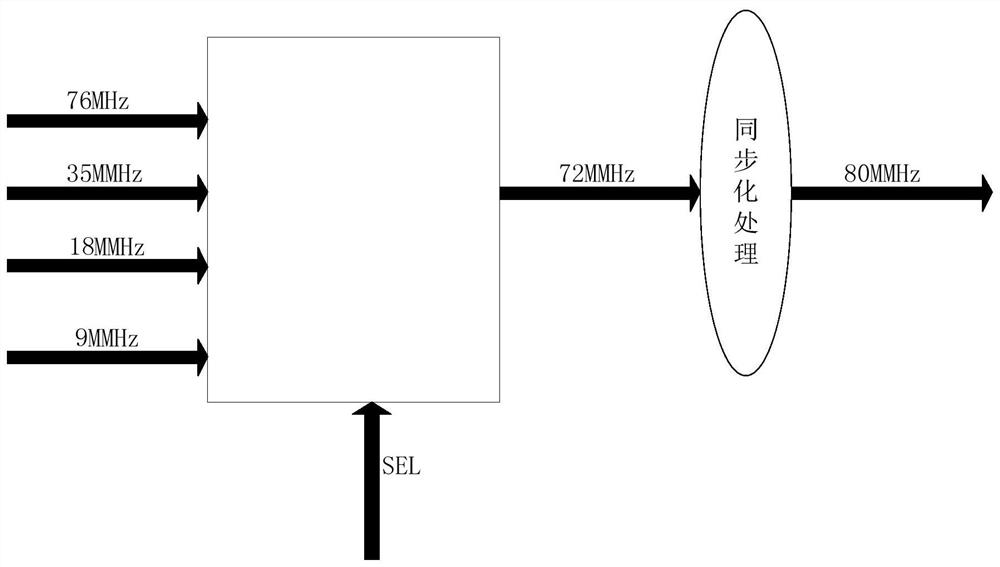

[0022] 1. When performing timing constraints on chip design, the concept of synchronous circuits is adopted, and the synchronous clock declaration is used as the central idea, and the asynchronous clock in the chip design is constrained to the frequency-divided clock of the main clock, so that it can be converted into a synchronous clock, forming Several synchronous clock architectures under one main clock, and then complete the timing constraints on chip design synchronization.

[0023] 2. Determin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More