Classification method of chip bin maps in wafer circuit probing

A technology of wafer testing and classification methods, which is applied in the direction of single semiconductor device testing, etc., can solve the problems of testing hardware damage, large leakage current, and long testing time, and achieve the effects of improving work efficiency, reducing quantity, and reducing testing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

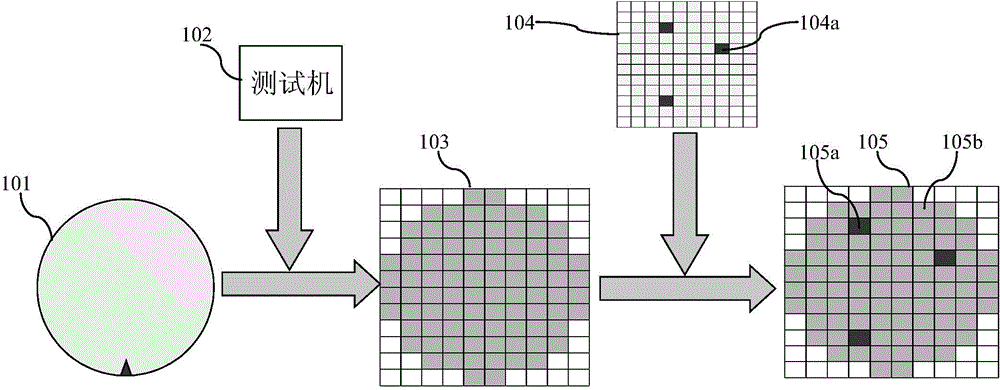

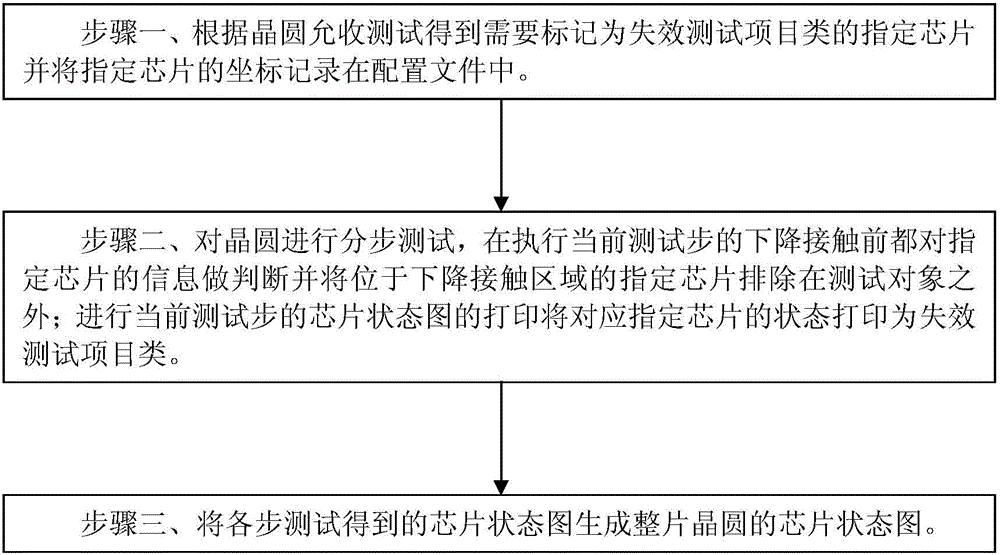

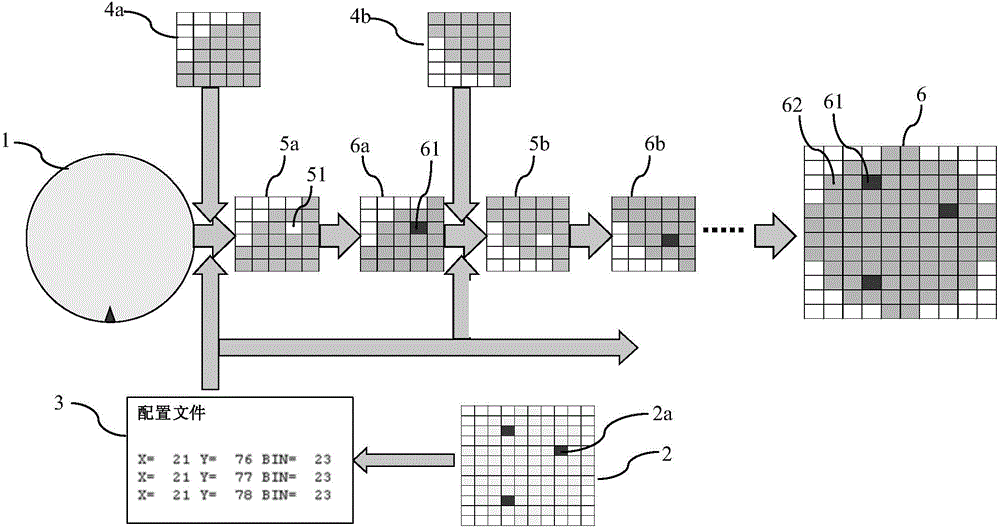

[0020] Such as figure 2 Shown is the flow chart of the classification method of the method wafer test chip state diagram of the embodiment of the present invention; image 3 As shown, it is a BIN MAP schematic diagram of the classification method of the wafer test chip state diagram according to the embodiment of the present invention. The classification method of wafer test chip state map in the embodiment of the present invention comprises the following steps:

[0021] Step 1. According to the results of the wafer acceptance test, it is judged that the chips in one or more specific areas of wafer 1 need to be changed to the failure test item category in the chip state diagram obtained from the wafer test, and will need to be marked as failure test items The chip of the class is defined as a specified chip and the coordinates of the specified chip are recorded in the configuration file 3 .

[0022] The coordinates of the specified chip recorded in the configuration file 3 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com