Clock gating trigger

A technology of gated clocks and flip-flops, applied in the direction of electrical pulse generator circuits, etc., can solve the problems of complex circuit topology, wasteful consumption of power consumption, circuit delay and large power consumption, etc. The effect of small delay and power consumption, improving the running speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

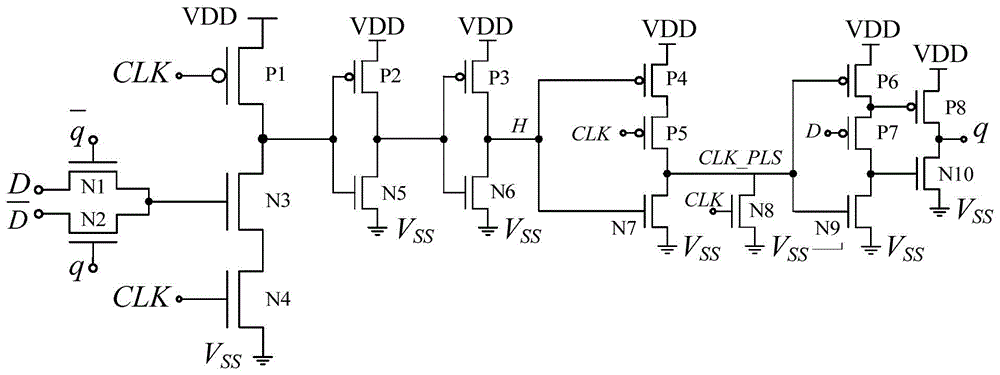

[0015] Example: as image 3 As shown, a gated clock flip-flop includes a first PMOS transistor P1, a second PMOS transistor P2, a third PMOS transistor P3, a fourth PMOS transistor P4, a fifth PMOS transistor P5, a sixth PMOS transistor P6, and a seventh PMOS transistor P6. PMOS transistor P7, eighth PMOS transistor P8, first NMOS transistor N1, second NMOS transistor N2, third NMOS transistor N3, fourth NMOS transistor N4, fifth NMOS transistor N5, sixth NMOS transistor N6, seventh NMOS transistor N7, the eighth NMOS transistor N8, the ninth NMOS transistor N9 and the tenth NMOS transistor N10;

[0016] The source of the first PMOS transistor P1, the source of the second PMOS transistor P2, the source of the third PMOS transistor P3, the source of the fourth PMOS transistor P4, the source of the sixth PMOS transistor P6 and the eighth PMOS transistor P8 The sources of all are connected to the power supply; the gate of the first PMOS transistor P1, the gate of the fifth PMOS ...

Embodiment 2

[0021]Embodiment 2: This embodiment is basically the same as Embodiment 1, except that in this embodiment, the first PMOS transistor P1, the second PMOS transistor P2, the third PMOS transistor P3, the fourth PMOS transistor P4, and the fifth PMOS transistor P5, sixth PMOS transistor P6, seventh PMOS transistor P7, eighth PMOS transistor P8, first NMOS transistor N1, second NMOS transistor N2, third NMOS transistor N3, fourth NMOS transistor N4, fifth NMOS transistor N5, The channel lengths of the sixth NMOS transistor N6, the seventh NMOS transistor N7, the eighth NMOS transistor N8, the ninth NMOS transistor N9 and the tenth NMOS transistor N10 are all 90 nm under the SMIC 90 nm standard process.

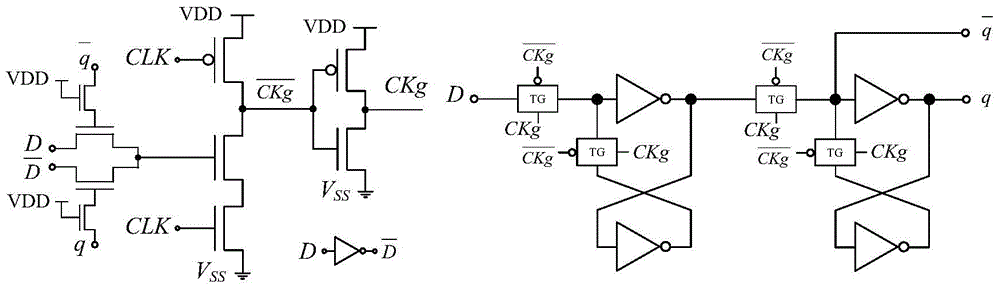

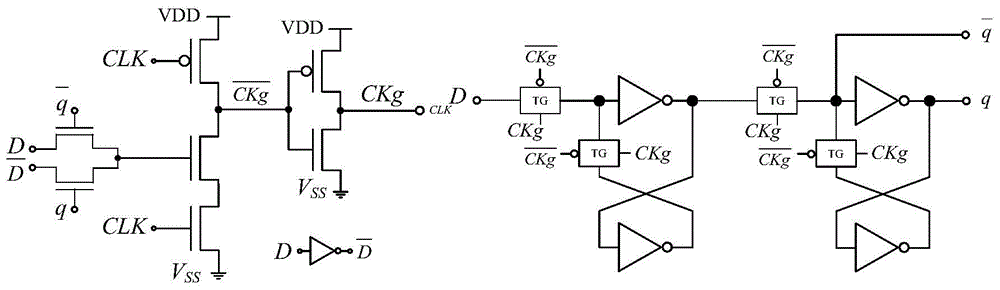

[0022] Under the SMIC130nm and SMIC90nm standard processes, compare the gated clock flip-flop of the present invention with respect to the two traditional gated clock flip-flops, the transmission tube gated clock flip-flop and the gate voltage bootstrap gated clock flip-flop. perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More