Multi-chip semiconductor packaging structure and manufacturing method

A packaging structure and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., to meet the needs of miniaturization development, realize system packaging, and reduce packaging volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

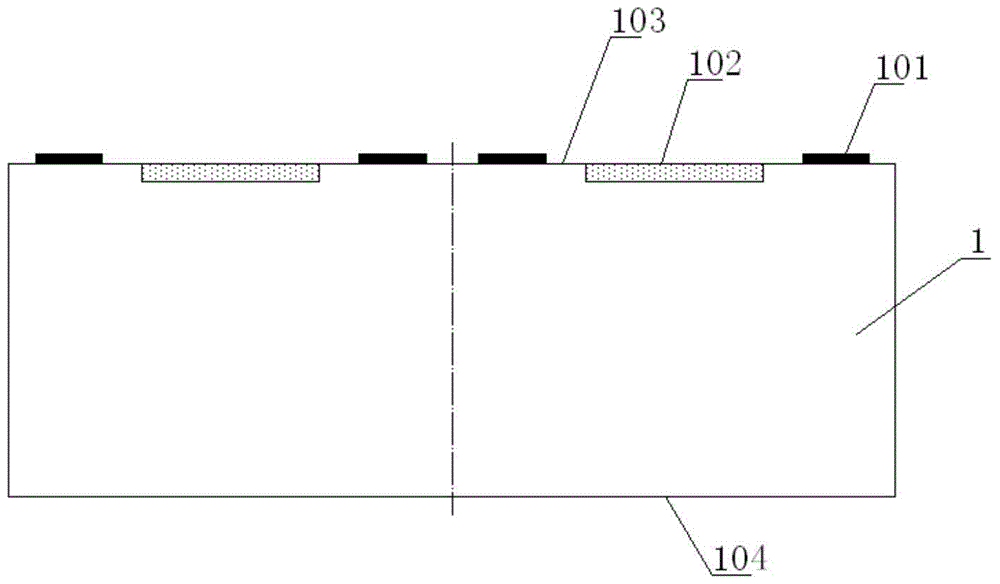

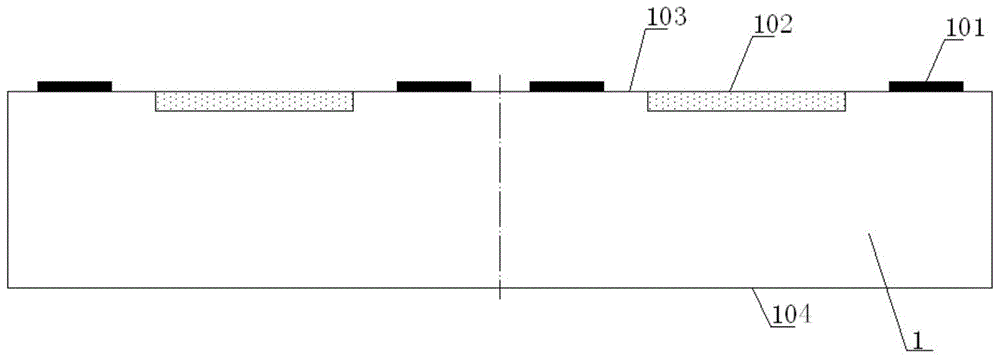

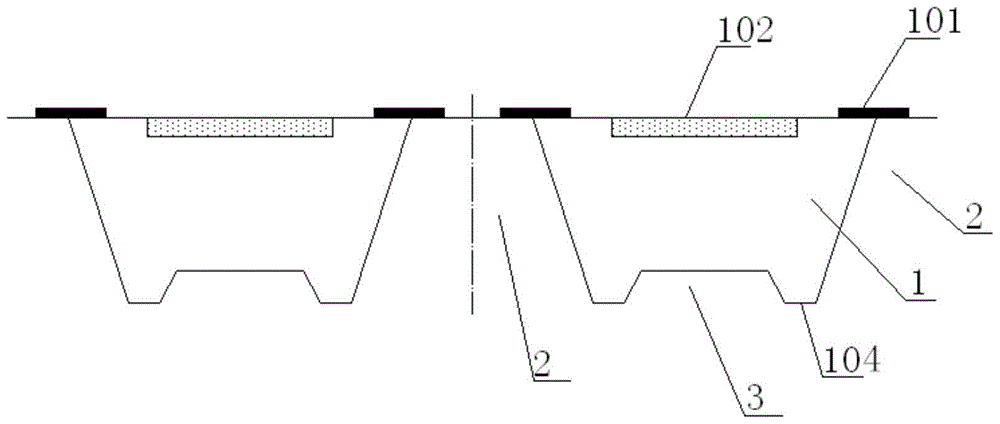

[0051] Such as Figure 12 As shown, a multi-chip semiconductor packaging structure includes a semiconductor bare chip 1, the semiconductor bare chip has a first surface 103 and a second surface 104 opposite to it; the first surface has an element region 102 and is located on the Several first pads 101 around the component area, the component area is used to receive the light source or user fingerprint information, the first pads are electrically connected to the component area; the second surface is formed with a The opening 2 and the groove 3, and the groove is opposite to the element area, the opening is opposite to the first pad and exposes the first pad; the second surface, the groove A first insulating layer 4, a metal wiring layer 5 and a second insulating layer 6 are sequentially formed on the inner wall and the inner wall of the opening, and the second insulating layer covers the metal wiring layer for protecting the metal wiring layer from being oxidized Corrosion, a...

Embodiment 2

[0072] This embodiment 2 includes all the technical features in the embodiment, such as Figure 13 As shown, the difference is that a protective layer 11 is provided on the element region. The protective layer is used to protect the sensing area of the sensor chip from damage. Optionally, the material of the protective layer is protective materials such as glass or film and glass ceramics. Preferably, the thickness of the protective layer is between 1-400 between microns.

[0073] To sum up, the present invention proposes a multi-chip semiconductor packaging structure and manufacturing method, and the grooves in the packaging structure provide favorable conditions for reducing the thickness of the packaging. Using the groove structure, other functional chips are placed in it, through The redistribution process interconnects the lines and realizes system packaging. Therefore, the packaging structure can reduce the packaging thickness and meet the requirements for the miniat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More