IP hard core intellectual property protection method and device based on path delay

A technology of intellectual property rights and path delay, applied in the protection of internal/peripheral computer components, etc., can solve the problem that the arbitrator is vulnerable to attacks, and achieve the effects of protecting interests, easy implementation, and small additional area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

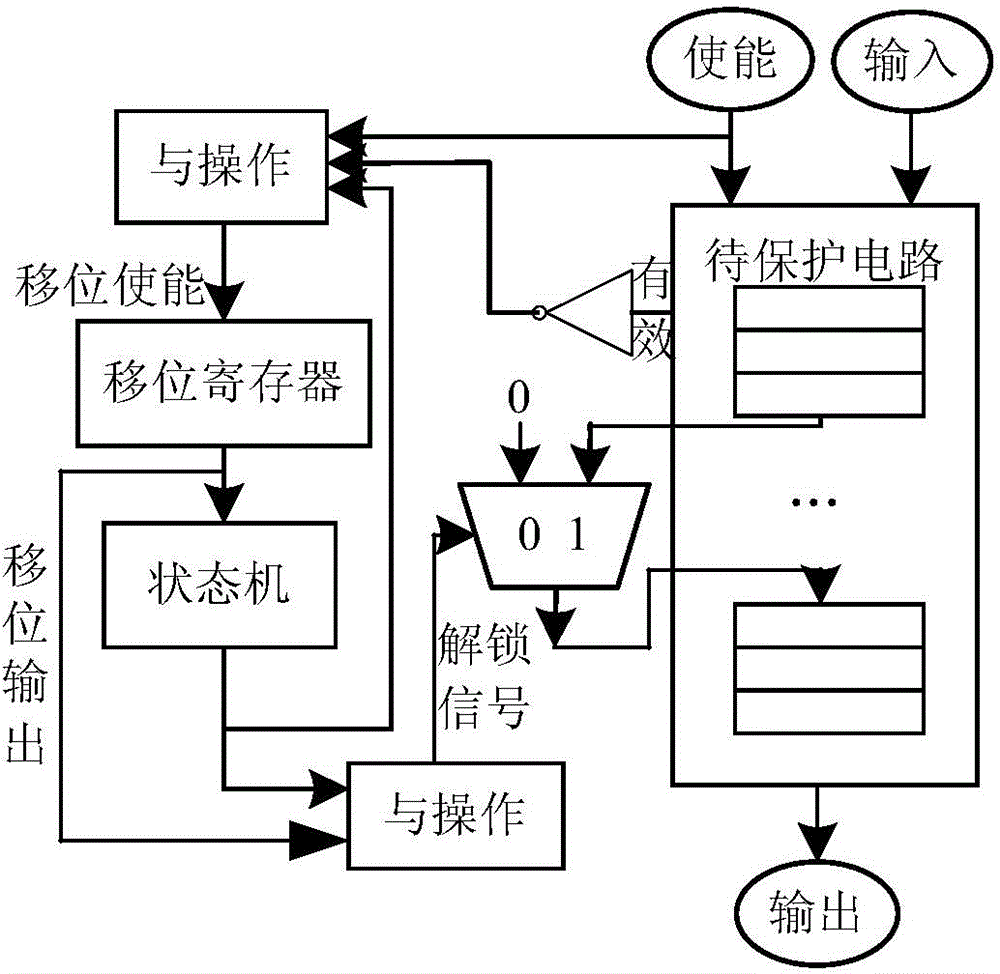

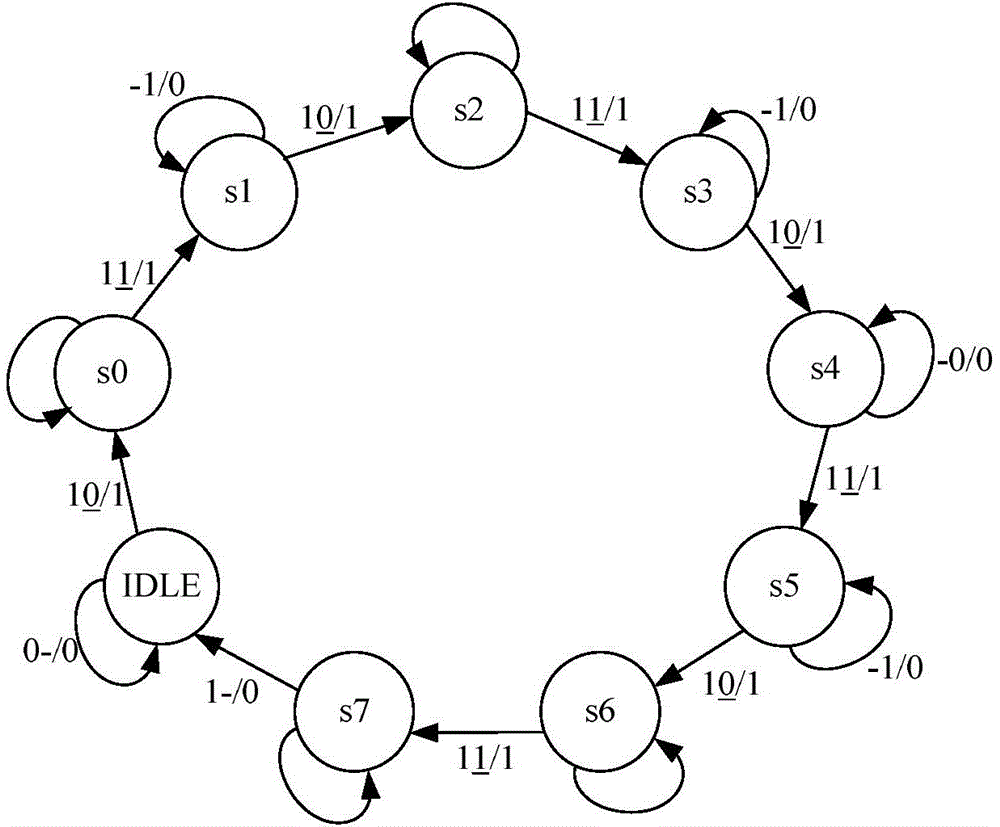

[0027] The invention provides a method for implementing intellectual property protection of hardware circuits by applying delay matching of two sequential logic paths. In the described method, the signal path delay is used as a reference, and the designed protection circuit needs to input the correct key to make it generate an unlocking signal after a specific delay. This specific delay is determined by a finite state machine and the routing delay of the physical layer. This method locks each hardware IP core very well, and the IP hard core cannot work normally without the key. Embedded in the key is proprietary information for the IP designer and buyer. The method mentioned in this paper can not only provide proof for the owner of the IP core, but also trace the source of the illegal dissemination of the IP core.

[0028] See the description below for details:

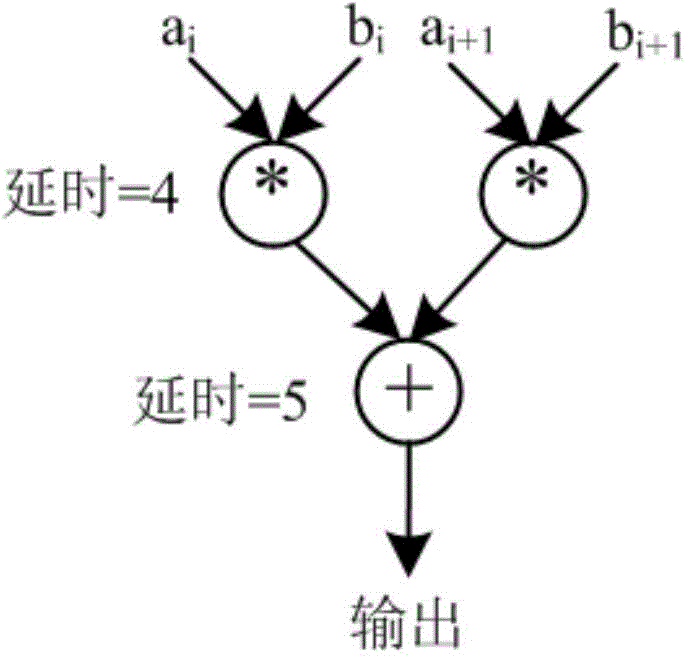

[0029] A method for implementing hardware circuit intellectual property (IP) protection using delay matching of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More