Input interface circuit

An input interface circuit and circuit technology, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problem that the input interface circuit does not have anti-attack, and improve the anti-attack. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

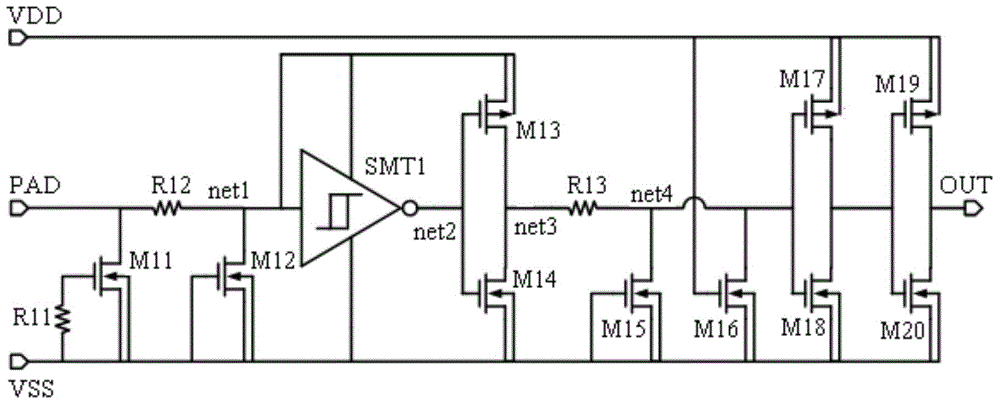

[0026] see figure 2 As shown, the input interface circuit of the present invention includes in the following embodiments:

[0027] An ESD protection circuit is composed of NMOS transistors M11 and M12, and resistors R11 and R12. Wherein, the NMOS transistor M11 and the resistor R11 are the main ESD protection circuit, which adopts a gate coupling structure. The resistor R12 is an ESD current-limiting resistor, and the NMOS transistor M12 is a secondary ESD protection circuit, protecting the gate of the subsequent circuit (Schmidt circuit).

[0028] The drain of the NMOS transistor M11 is connected to one end of the resistor R12 and serves as the input of the PAD, the gate of the NMOS transistor M11 is connected to one end of the resistor R11, and the other end of the resistor R11 is connected to the source and substrate of the NMOS transistor M11 grounded.

[0029] The other end of the resistor R12 is connected to the source of the PMOS transistor M12, and the node connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More