Interpolation estimation method in parallel demodulation bit synchronization

A technology of bit synchronization and interpolation, applied in the field of satellite data transmission, which can solve the problems that serial mode cannot meet the requirements, signal symbol rate is high, and clock frequency is low.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

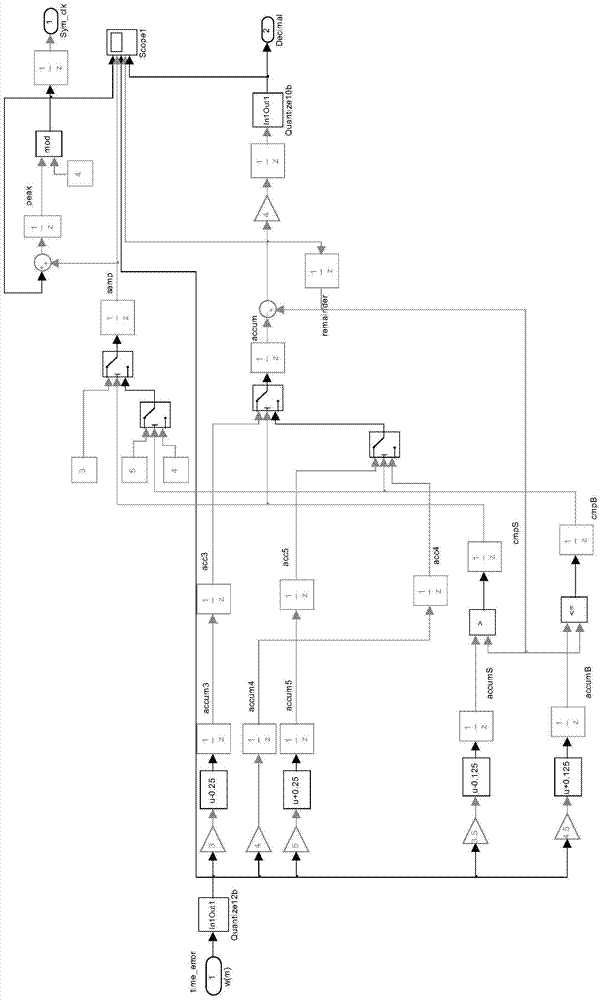

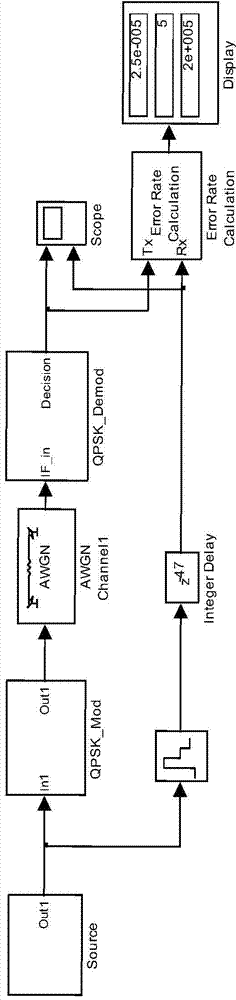

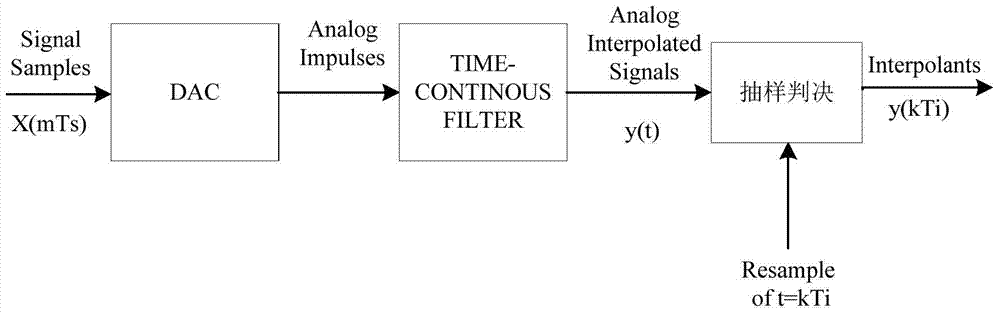

[0074] The invention is based on an all-digital bit synchronization algorithm in which an analog input signal x(t) with a symbol rate T is processed by a local fixed clock period T s After sampling, it becomes a discrete signal x(mT s ). The value obtained by the interpolation filter is sent to the timing error detector to obtain the error τ(n) between the input signal and the local clock, and then a loop filter is used to filter out the noise and high-frequency components, and the obtained value e (n) sent to the controller to calculate the integer sampling time m k and interpolation filter interpolation point position u k , so as to obtain the timing output y(kT i ); the specific method is as follows:

[0075] 1. Derivation of the relationship between η(N(m+1)) and η(Nm), W(Nm) in parallel mode.

[0076] A. In parallel mode, we assume that there are N signals, then the data rate becomes 1 / NT s .

[0077] B. Sampling period T s and the symbol period T ratio,

[007...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More