Multi-picture splitter and splitting method based on fpga for high-definition and standard-definition mixed broadcasting

A multi-screen splitter, high-definition and standard-definition technology, applied in the direction of standard conversion, color TV parts, TV system parts, etc., can solve the problems of high cost and system instability, and achieve low cost, high flexibility, The effect of small peripheral devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

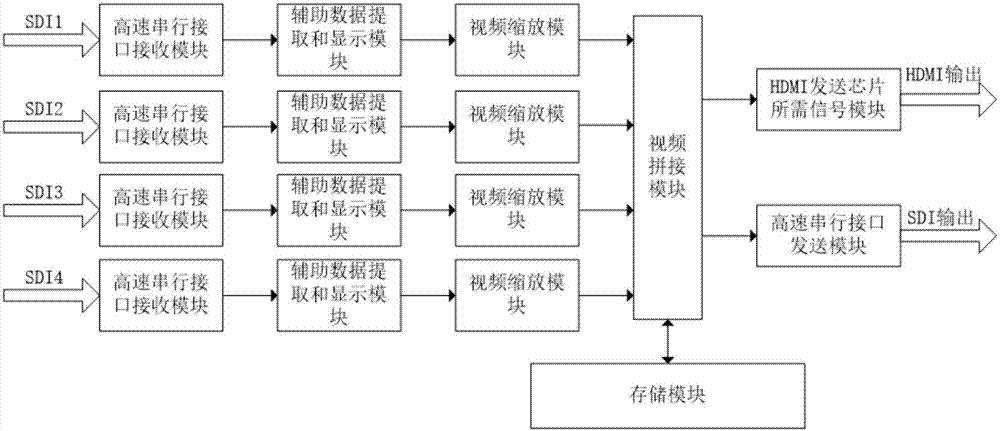

[0059] Such as figure 1 As shown, the FPGA-based high-definition and standard-definition mixed broadcast multi-picture splitter provided by the present invention includes 4 high-speed serial interface receiving modules, 4 auxiliary data extraction and display modules, and 4 video scaling modules. The line interface receiving module, auxiliary data extraction and display module, and video scaling module cooperate to form four groups, which process four SDI video signals respectively; 4 video scaling modules are respectively connected with the video splicing module; the video splicing module is respectively connected with the storage module , The signal module required by the HDMI sending chip and the high-speed serial interface sending module are connected. If there are more channels of SDI video signals, then correspondingly increase the number of high-speed serial interface receiving modules, auxiliary data extraction and display modules, and video scaling modules.

[0060] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More