LDO circuit applied to HSIC connector whole chip integration

A circuit and interface technology, which is applied in the field of LDO circuit for full-chip integration of HSIC interface, can solve the problems of adding chip pins and external components, and achieve the effect of improving response speed, saving external capacitor components, and fast response speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

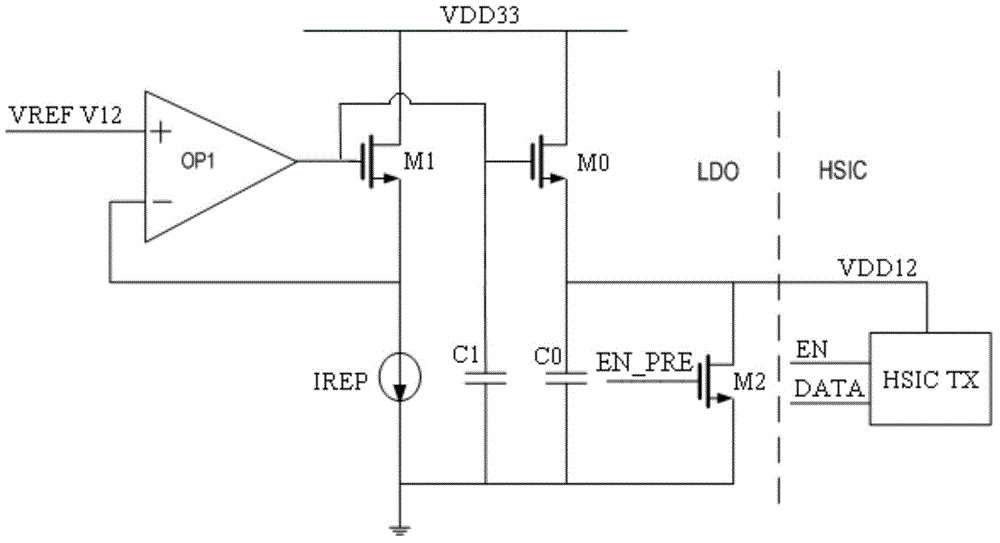

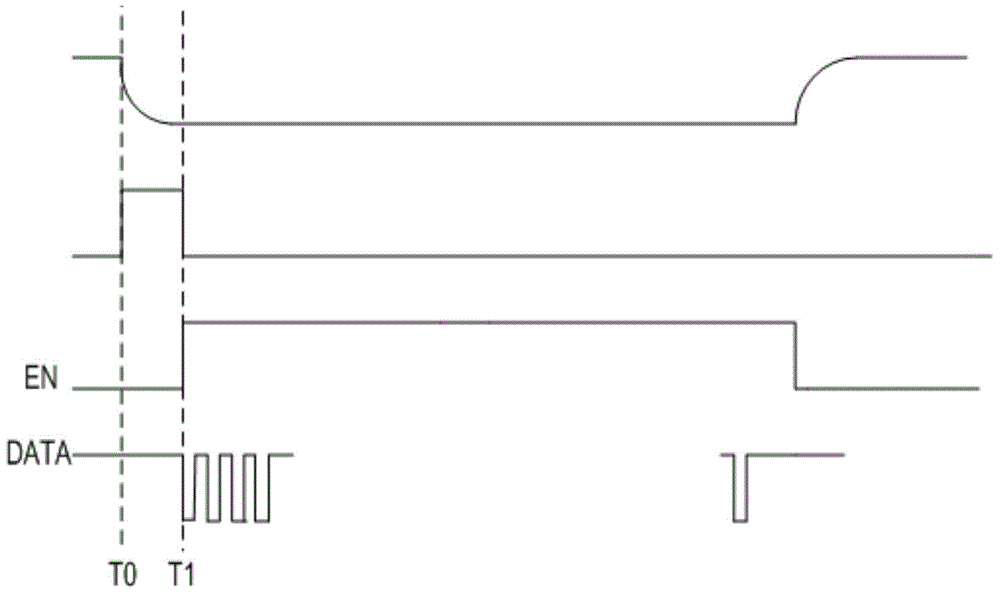

[0017] Aiming at the application requirements of the HSIC interface, the present invention proposes a full-chip integrated LDO circuit. see figure 1 As shown, the LDO circuit applied to the full-chip integration of the HSIC interface, in the following embodiments, adopts a fully integrated filter capacitor, including: an error amplifier OP1, a matching NMOS transistor M1, a gate filter capacitor C1, and a Matching current source IREP, a power NMOS transistor M0, an output stage filter capacitor C0, and an NMOS transistor M2; among them, the error amplifier OP1, matching NMOS transistor M1, gate filter capacitor C1, and matching current source IREP form the low-frequency control loop of the LDO circuit Road; the power NMOS transistor M0 is used as the output stage of the LDO circuit, and the NMOS transistor M2 is a high-speed response tube, which is used as the load of the LDO circuit.

[0018] The error amplifier OP1 is an operational amplifier, its positive input terminal in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com