Phase Locked Loop System

A phase-locked loop and phase technology, applied in the field of phase-locked loop systems, can solve the problems of deterioration of charge pump noise contribution, deterioration of skew index of anti-skew PLL, clock skew cannot meet the requirements of the index, etc., to eliminate skewed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

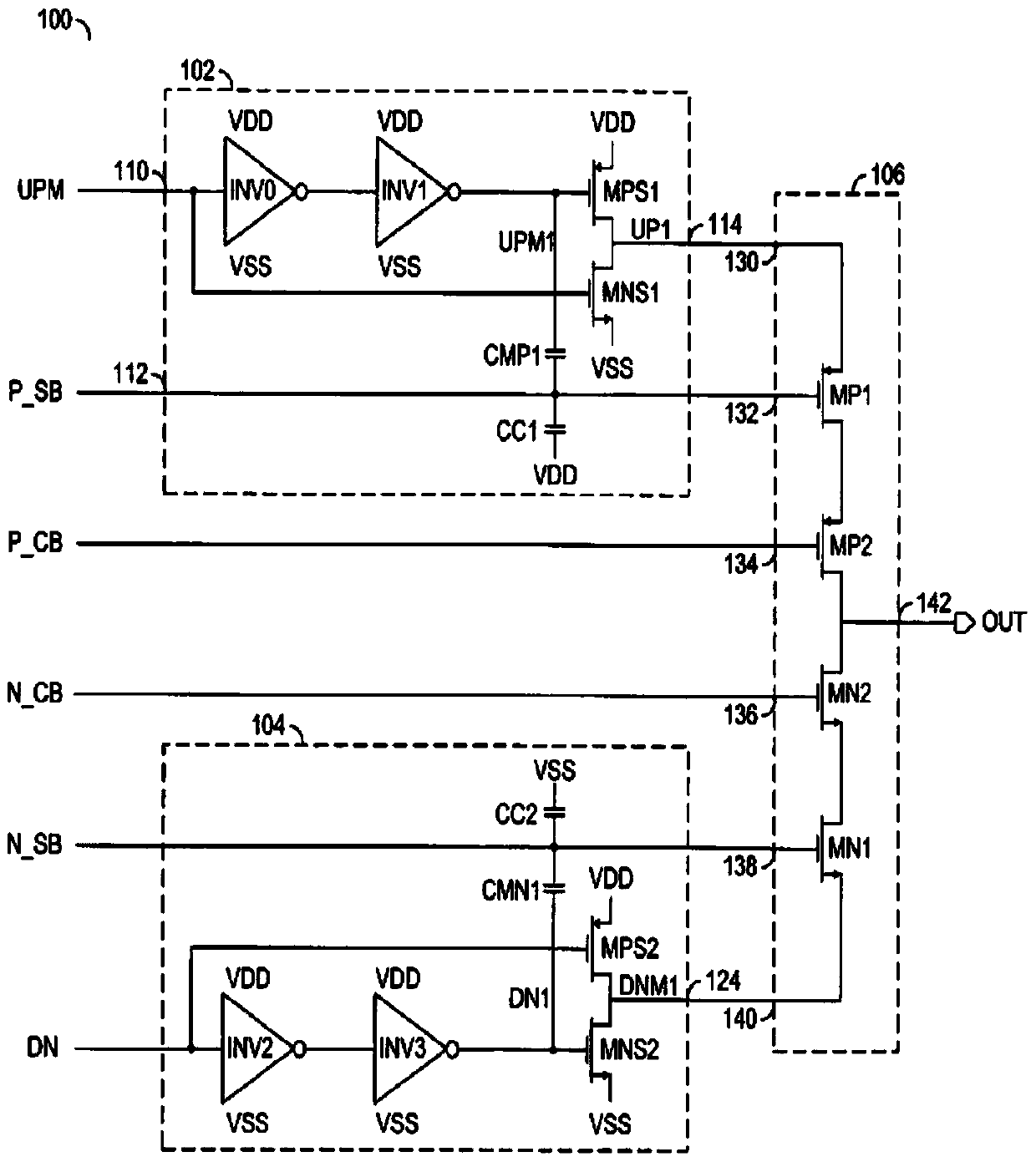

Embodiment Construction

[0056] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

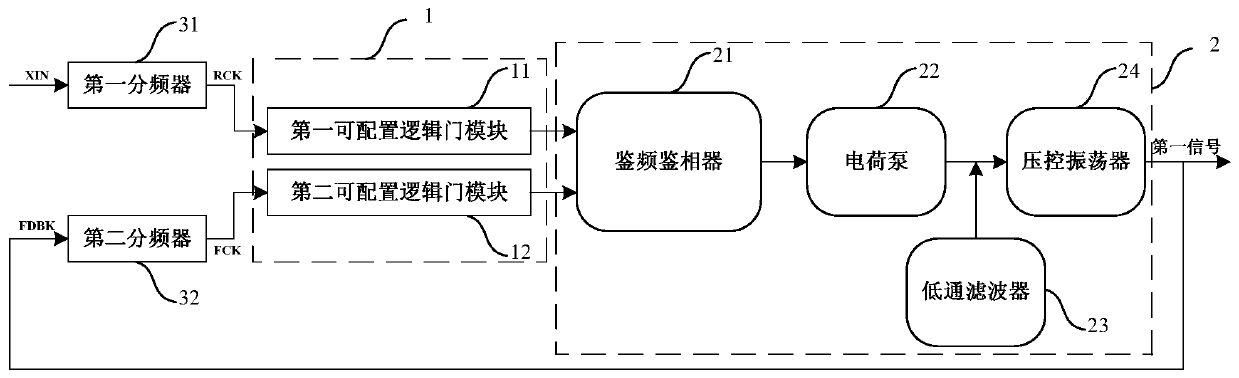

[0057] see figure 2 , the phase-locked loop system of the embodiment of the present invention at least includes: a delay unit 1, which is used to delay the reference clock signal and the feedback clock signal; a phase-locked loop component 2, which is connected to the delay unit 1, and is used to The clock signal is fed back, and the first signal locked to the frequency and phase of the reference clock signal is output. It should be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More