Universal verification platform and method for development of network core chip technology

A chip technology and universal verification technology, applied in the field of network core chips, can solve problems such as unreasonable resource utilization, expensive materials, more manpower and time costs, and achieve the effects of convenient design and testing, simplified settings, and flexible configuration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

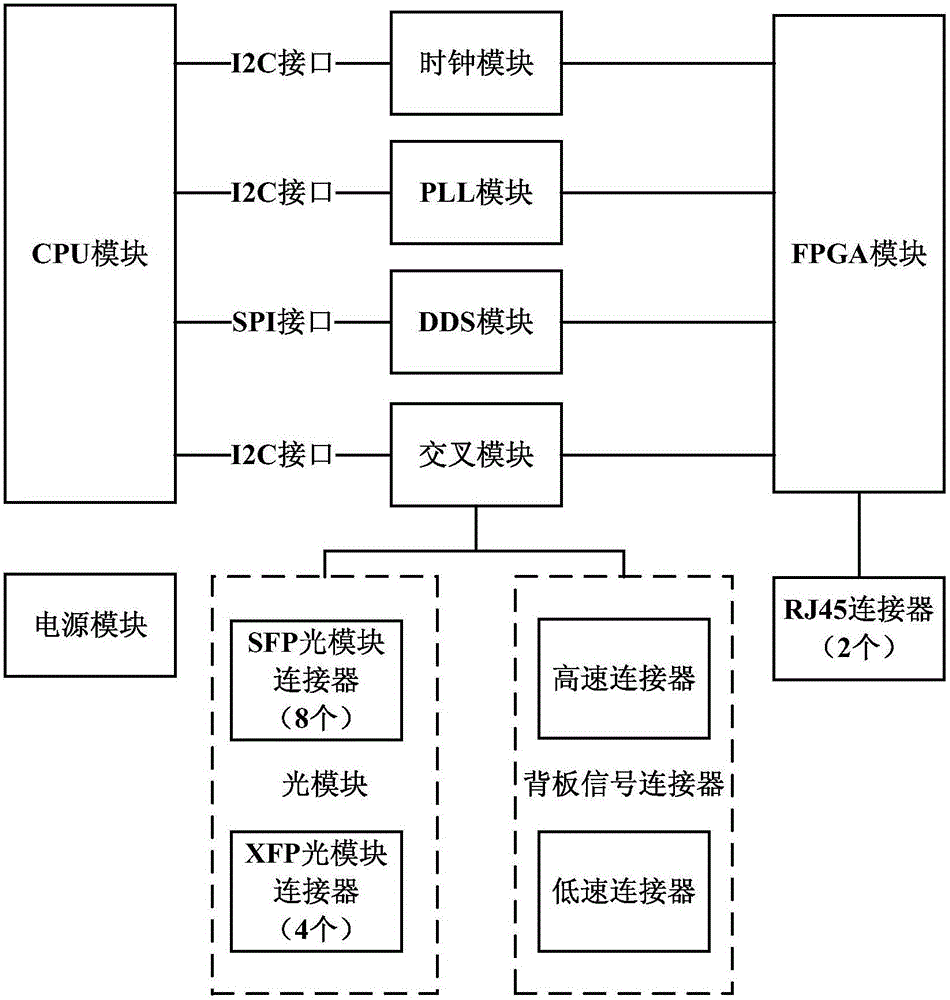

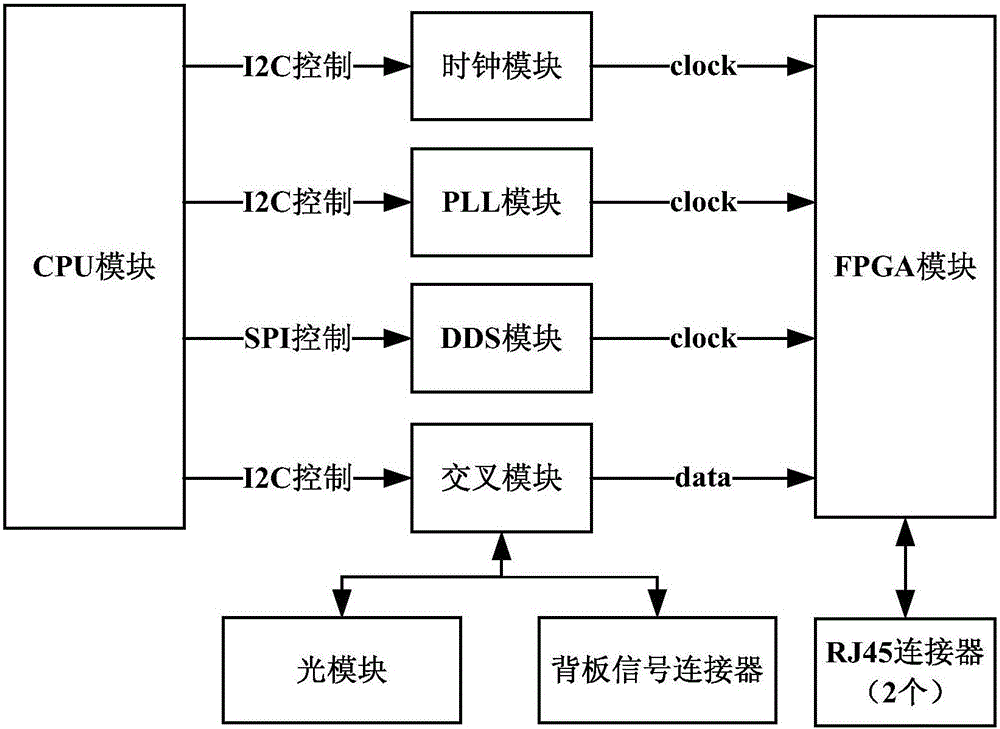

[0039] see figure 1 and figure 2 As shown, the general verification platform for network class core chip technology development in the embodiment of the present invention includes a power supply module, a CPU module, a clock module, a PLL (PhaseLockedLoop, phase-locked loop) module, a DDS (DirectDigitalSynthesizer, direct digital frequency Synthesizer) module, crossover module, FPGA module, backplane signal connector, optical module and RJ45 (standard 8-bit modular interface) connector.

[0040] All modules and connectors are connected to the power module, the CPU module is connected to the FPGA module through the clock module, PLL module, DDS module, and the crossover module, and the FPGA module is connected to the RJ45 connector; the crossover module is connected to the backplane signal connector, optical The modules are connected.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More