Sorting mistake-proofing method and device for multiple layers of printed circuit board (PCB) lamination

An error-proofing and board-stacking technology, which is applied in multi-layer circuit manufacturing, electrical components, printed circuit manufacturing, etc., can solve problems such as flow to customers, failure to detect core board sorting errors, and loss of production costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and through specific implementation methods.

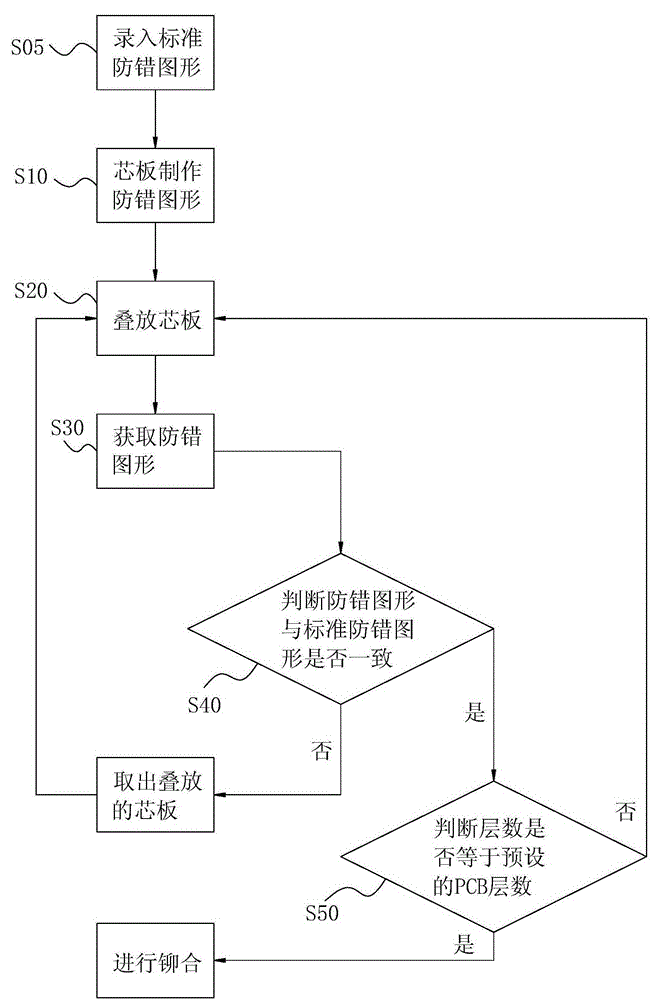

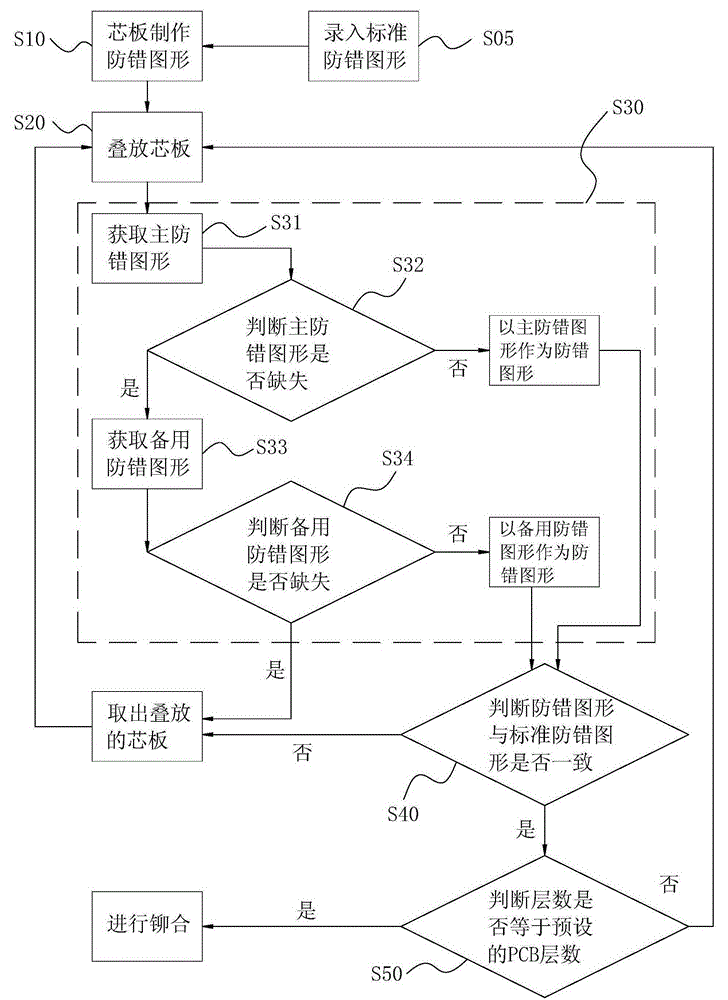

[0070] In this embodiment, if figure 1 and image 3 As shown, a sorting and error-proofing method for multilayer PCB stacks is provided, including the following steps:

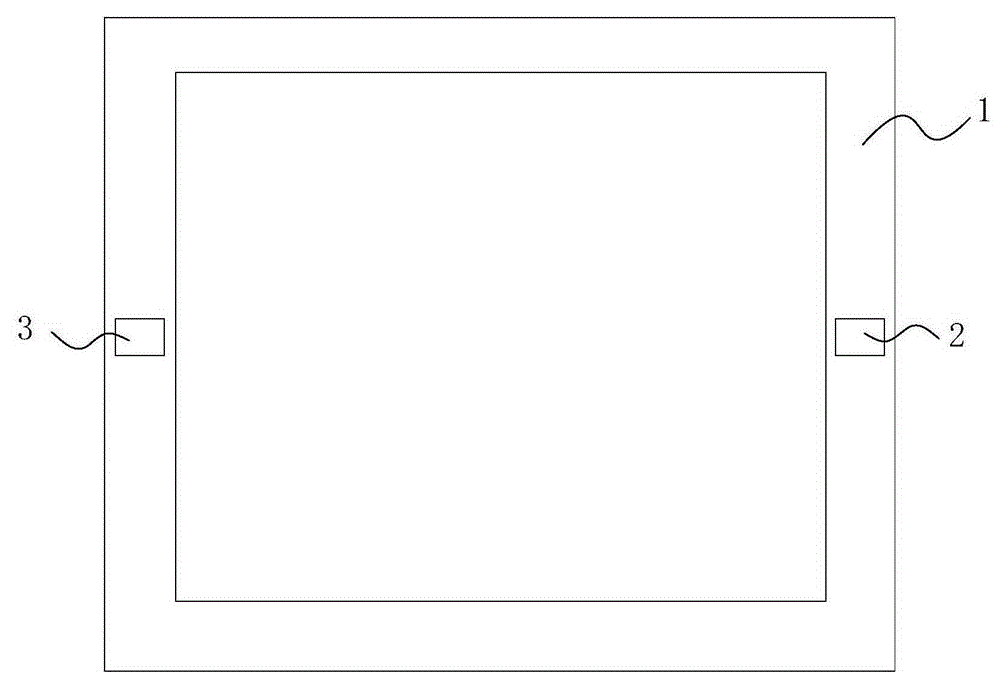

[0071] S10, making different error-proof graphics on core boards 1 of different levels;

[0072] S20, stacking one core board 1;

[0073] S30. Obtain the error-proofing pattern on the stacked core board 1;

[0074] S40. Judging whether the acquired error-proofing pattern is consistent with the standard error-proofing pattern of the corresponding level in the control system:

[0075] If not, take out the stacked core board 1, and return to step S20;

[0076] If yes, enter step S50;

[0077] S50, judging whether the number of layers of the core board 1 is equal to the number of pre-designed PCB layers:

[0078] If not, return t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More