A sorting and error-proofing method and device for multi-layer PCB stacked boards

An error-proof and board-stacking technology, which is applied in multilayer circuit manufacturing, electrical components, printed circuit manufacturing, etc., can solve problems such as difficult products to be found, flow to customers, and core boards that cannot be reused.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] The technical solutions of the present invention are further described below with reference to the accompanying drawings and through specific embodiments.

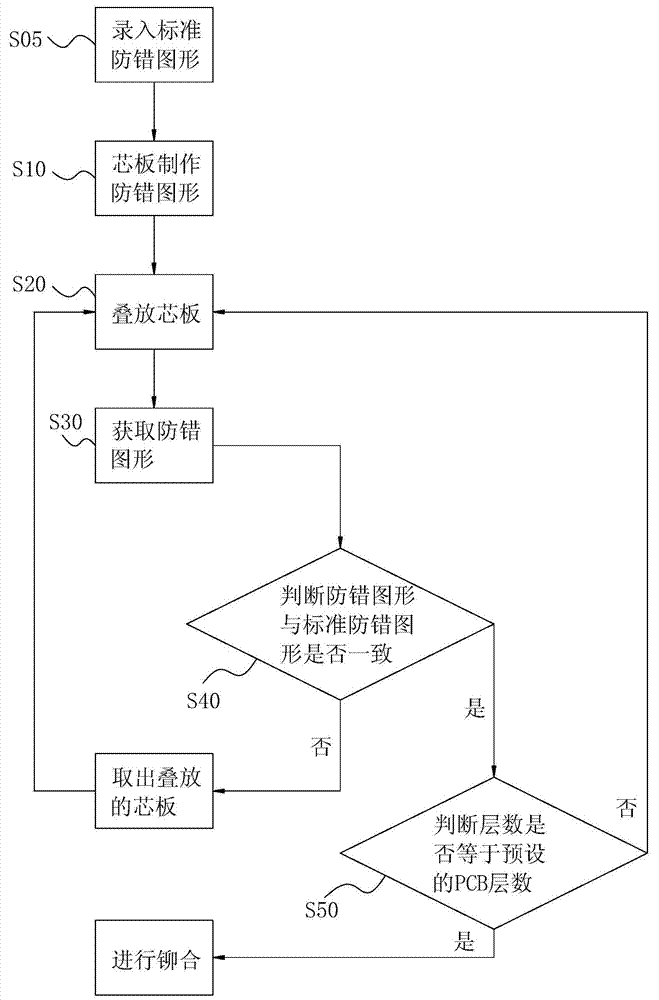

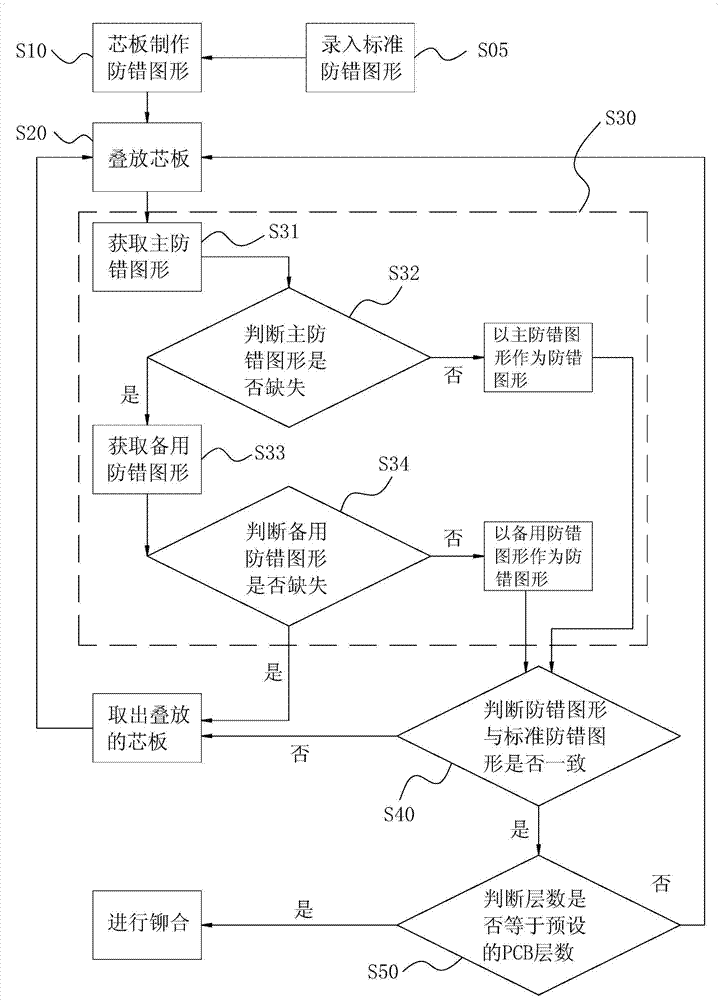

[0070] In this embodiment, as figure 1 and image 3 As shown, a method for sorting and error prevention of multilayer PCB stacks is provided, which includes the following steps:

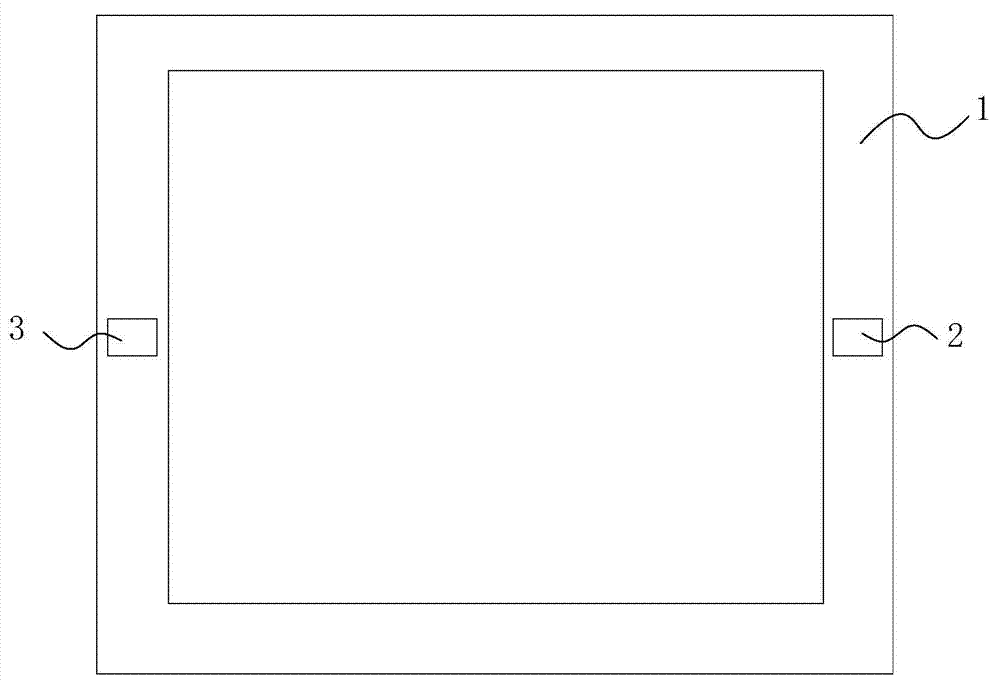

[0071] S10, making different error-proofing patterns on the core boards 1 at different levels;

[0072] S20, stacking a piece of the core board 1;

[0073] S30, acquiring the error-proofing pattern on the stacked core boards 1;

[0074] S40, judging whether the obtained error-proofing graphic is consistent with the standard error-proofing graphic of the corresponding level in the control system:

[0075] If not, take out the stacked core boards 1, and return to step S20;

[0076] If yes, go to step S50;

[0077] S50, determine whether the number of layers of the core board 1 is equal to the number of pre-designed PCB layers:

[0078...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More