Automatic analysis method capable of reconstructing start interval of periodic pipeline iteration in complier

A technology for cycle pipeline iteration and automatic analysis, applied in the direction of instruments, memory systems, program control design, etc., can solve the problem that affects the promotion of fine-grained reconfigurable compilers, cannot deal with the problem of pipeline start-up distance between non-innermost loop iterations, Issues such as automated analysis and related optimization methods are not raised

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described in detail below with reference to the accompanying drawings.

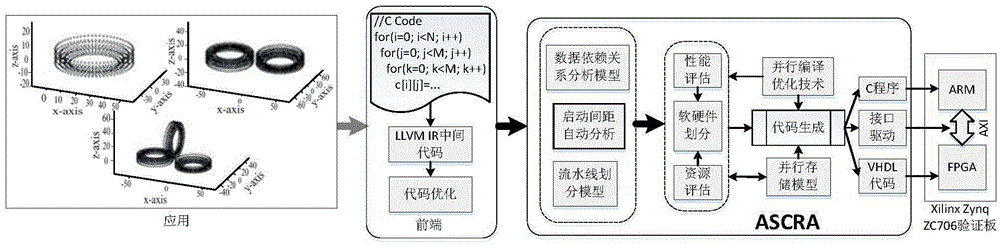

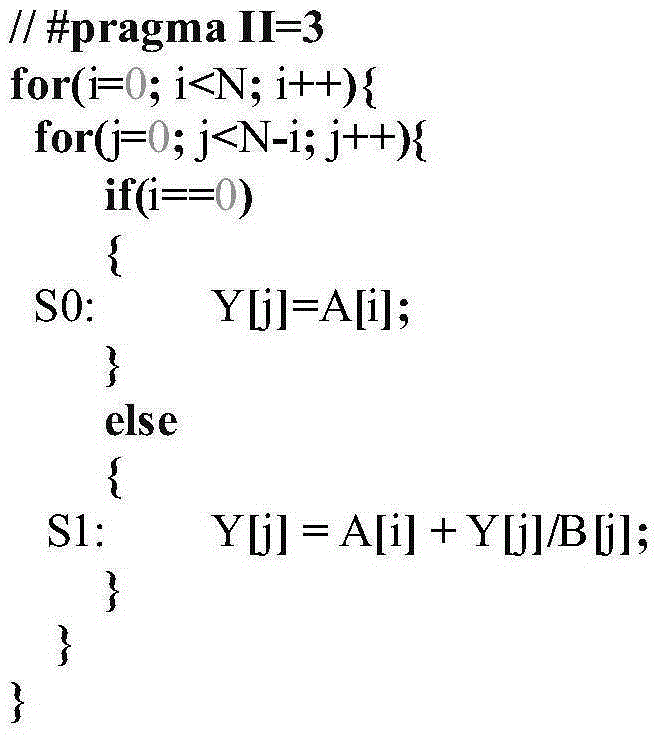

[0042] In the reconfigurable hybrid computing system, due to the customizability of FPGA and the uncertainty of the hardware structure, it is impossible to directly use the software pipelining technology designed in the general computer system structure to realize the variable start-up spacing control between multi-layer loop iterations. When the existing fine-grained reconfigurable compiler realizes the loop pipeline parallel hardware structure mapping, the statement-guided method is mainly used to realize the generation of the pipeline startup interval between iterations. The improvement in the implementation of the startup interval between loop pipeline iterations, this part uses an example of a multi-layer nested loop to describe the problem.

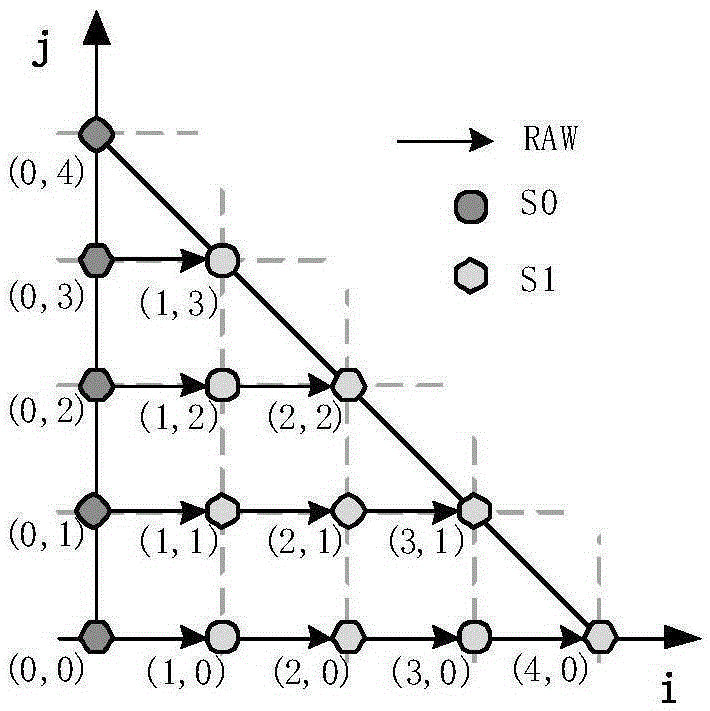

[0043] As shown in Figure 1(a), it shows a typical nested loop with data correlation between iterations of the out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More