Task-level parallel scheduling method and system for dynamically reconfigurable processor

A scheduling system and scheduling method technology, applied in the computer field, can solve the problem that reconfigurable processors do not have parallel processing specifications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The specific embodiments of the present invention are given below in conjunction with the accompanying drawings, but the present invention is not limited to the following embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in very simplified form and use imprecise ratios, which are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

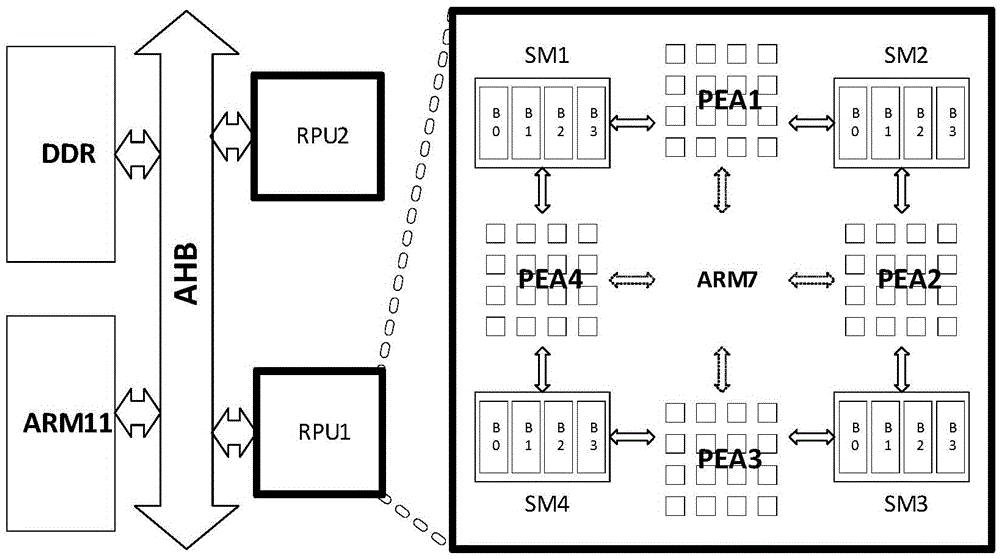

[0030] Please refer to figure 1 , figure 1 Shown is a schematic structural diagram of a task-level parallel scheduling system of a dynamically reconfigurable processor according to a preferred embodiment of the present invention, wherein the enlarged view of RPU1 on the right side of the box is used to display its internal functional structure. The present invention proposes a task-level parallel scheduling system of a dynamically reconfigurable processor, i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More