Method for forming semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, to achieve the effects of good shape, stable and easy-to-control stress, and accurate size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

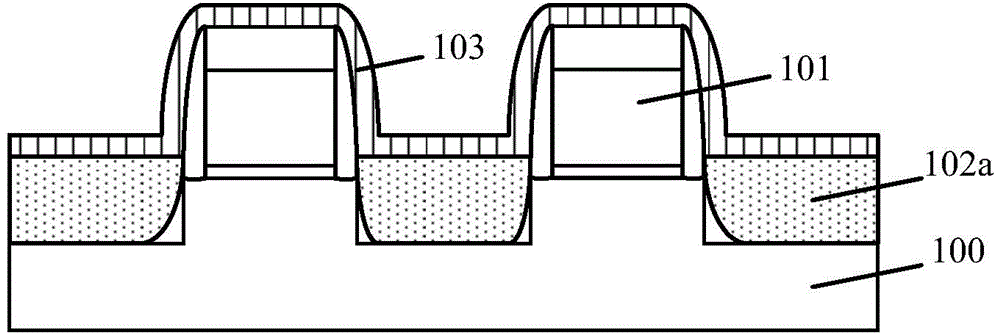

[0035]As mentioned in the background art, the stress provided by the stress layer formed in the source region and the drain region of the transistor cannot meet the technical requirements, and the stress on the channel region of the transistor needs to be further increased.

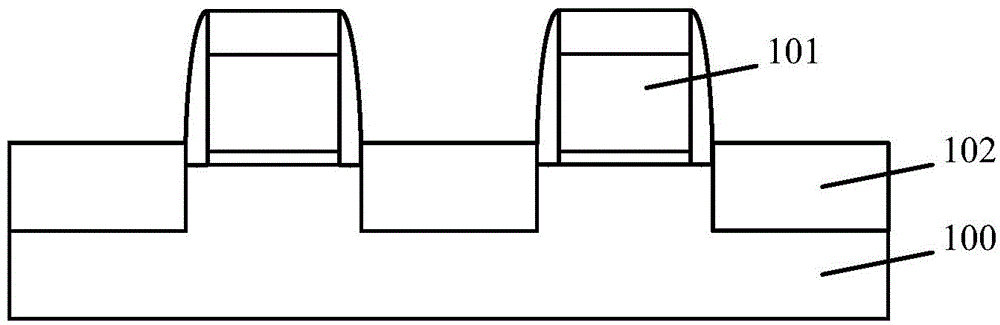

[0036] Please refer to figure 1 , figure 1 It is a schematic cross-sectional structure diagram of a transistor with a source region and a drain region with a stress layer according to an embodiment of the present invention, including: a substrate 100; a gate structure 101 located on the surface of the substrate 100; and a substrate 100 located on both sides of the gate structure 101 Inner stress layer 102 .

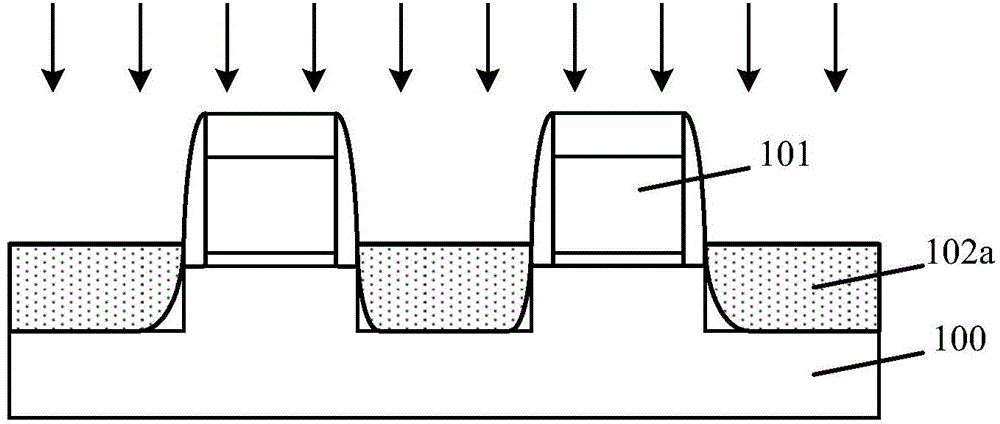

[0037] Since the embedded stress layer (embedded stress layer) is formed behind the source and drain regions of the transistor, the stress layer can apply stress to the substrate due to the lattice mismatch between the stress layer and the substrate, and the stress layer is inserted into the subst...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More