An embedded memory emb configuration chain structure and configuration method

An embedded memory, configuration chain technology, applied in static memory, digital memory information, information storage and other directions, can solve problems such as unfavorable FPGA chip integration, and achieve the effect of reducing the number of interface lines, reducing complexity, and reducing wiring.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

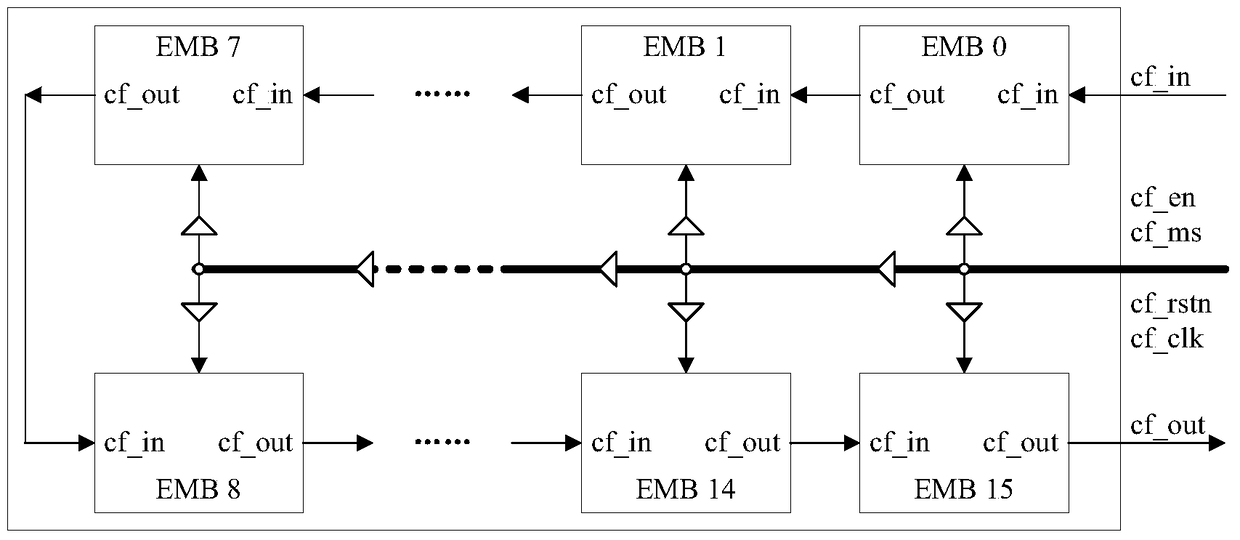

[0032] The EMB configuration chain provided by the embodiment of the present invention is composed of at least two EMBs that are cascaded. figure 1 It is a schematic diagram of an EMB configuration chain structure in an FPGA chip provided by an embodiment of the present invention. in such as figure 1 In the example shown, the EMB configuration chain includes 16 sequentially cascaded EMBs.

[0033] In the EMB configuration chain, the clock signal cf_clk, the configuration mode selection enable signal cf_ms, the enable signal cf-en, and the reset signal cf_rstn are transmitted from right to left through the buffer level by level as shown in the figure, and the configuration data input port Under the sampling of the clock signal cf_clk, the input data cf_in selects the setting of the enable signal cf_ms and the enable s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com