Method and device for self-adaptive adjustment of chip memory write operation timing path

A technology of self-adaptive adjustment and writing operation, which is applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of long data path delay, etc., and achieve the effect of increasing the operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

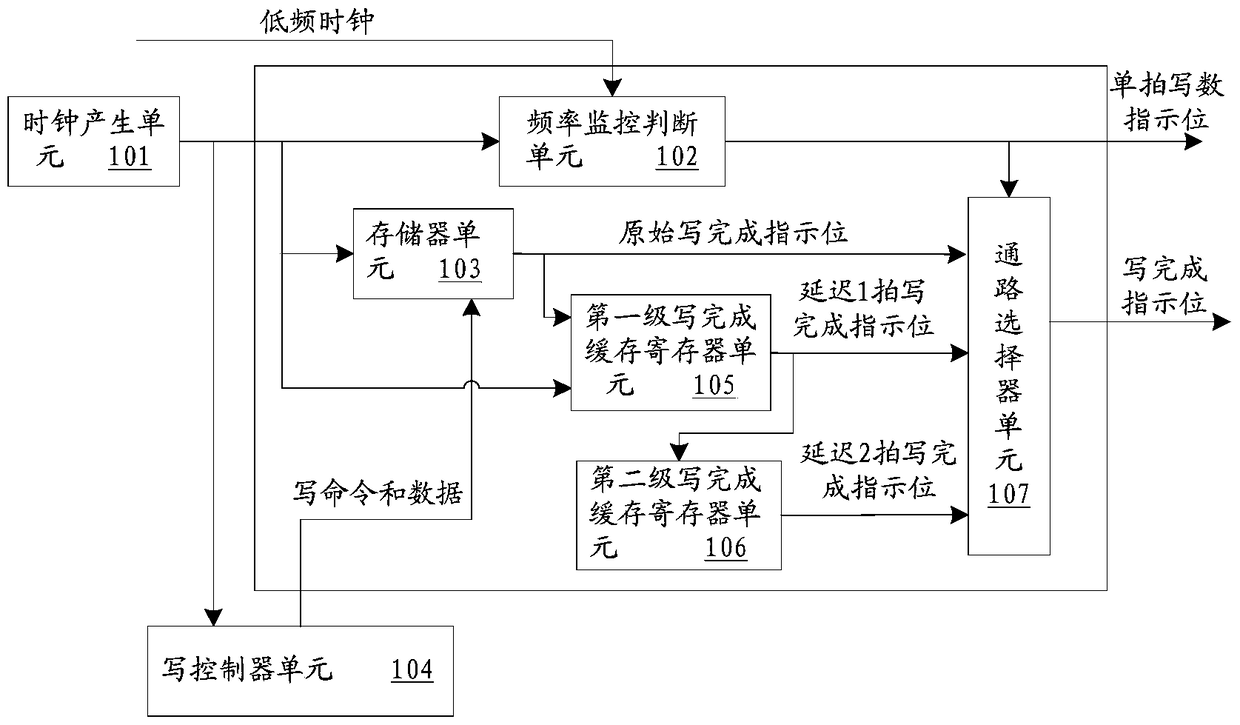

[0015] The self-adaptive adjustment method for the chip memory write operation timing path of the present invention comprises the following steps:

[0016] After the chip initialization is completed, it starts to work and generates a working clock;

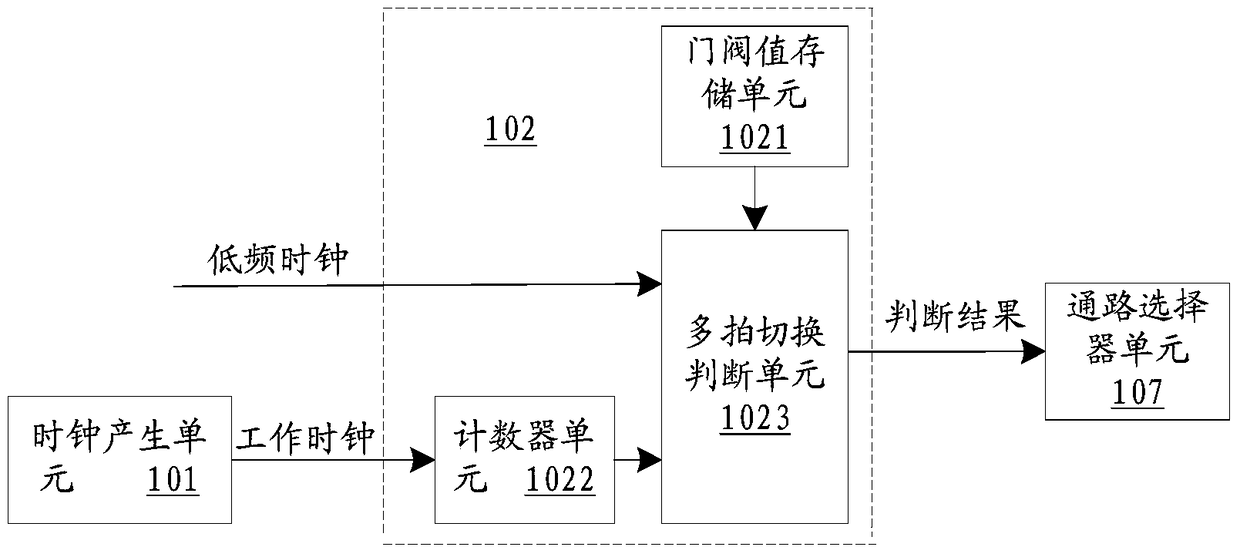

[0017] Judging the working clock frequency according to the low-frequency clock input by the chip and the working clock;

[0018] The write control memory unit outputs a write command and write data to the memory unit to perform a write operation, and at the same time, after one working clock cycle of the write command, the original write completion indicator bit is set to be effective;

[0019] According to the received write command, write data and working clock, the memory unit outputs the original writing completion indication bit after the write command is sampled by the working clock, and after the delay time of the write action inherent in the circuit;

[0020] The original write completion indicator is respectively delaye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More