Hash algorithm hardware realization device based on FPGA

A hardware implementation and algorithm technology, which is applied in the field of encryption algorithm and large-capacity data search, can solve the problems of impracticality and low Hash performance, and achieve the effect of fast search

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

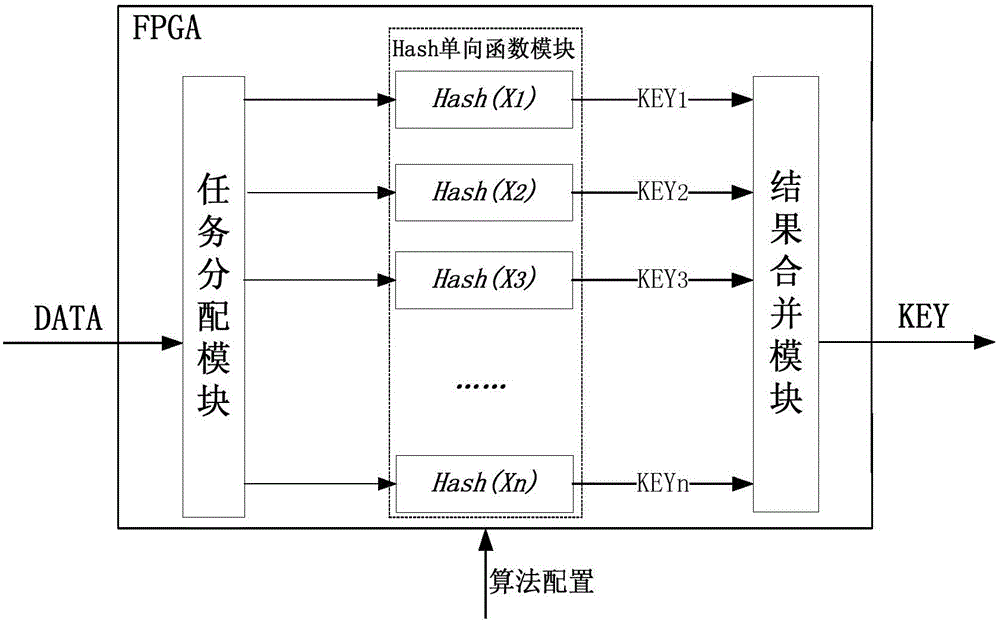

[0024] As shown in the figure, the FPGA-based Hash algorithm hardware implementation device includes a task allocation module, a Hash one-way function module and a result merging module, and the input DATA data is disassembled into n small pieces by the task allocation module, respectively X1, X2...Xn is calculated by n Hash one-way functions in the Hash one-way function module to obtain n KEY values, and then the results are merged and calculated by the result merging module, and finally the KEY value of the DATA data is obtained.

[0025] The working process of the FPGA-based Hash algorithm hardware implementation device of the present invention is as follows, and a comparative test is carried out.

[0026] 1. Make sure the DATA data is 2G in size, and n is 64;

[0027] 2. Select the HASH algorithm of MD5, SHA-1, SHA-256 and SHA-512 as the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More